针对电路关键路径的硬件木马监测与防护

张浩宇,应健锋,宋晨钰,王可可,易茂祥

合肥工业大学 电子科学与应用物理学院,合肥230009

1 引言

随着集成电路技术的快速发展,当前IC 芯片的设计与制造趋于分离,致使IC 芯片面临诸多的安全威胁[1]。集成电路的外包设计和制造过程为攻击者提供了绝佳的机会。攻击者通过更改IC 芯片的原始设计或插入具有一定功能的硬件木马电路。它们在特定条件下触发,修改电路功能或者直接破坏电路、泄露重要信息等[2]。硬件木马可以在电路的设计、制造的任何阶段插入。由于IC 构成了航空航天、军事国防、电子通信、工业制造、医疗设备等关键领域,因此预防和检测硬件木马的插入对IC芯片的安全性起着至关重要的作用。

近年来,硬件木马的检测方法主要分为两类:旁路信号分析法[3-5]和逻辑测试法[6]。基于旁路分析的方法是通过测量电路旁路信号的参数(例如延时[7]、功耗[8]、电磁信号等),通过与相同的已确定无硬件木马插入的电路——“黄金模型”作对比,分析电路旁路信号参数的变化来判断是否有硬件木马的插入。该类方法不仅需要无木马插入的“黄金模型”作为对比,而且易受到工艺偏差和外部噪声的影响。特别当硬件木马尺寸比较小(例如晶体管级、门级的小型硬件木马),对电路旁路信号的影响特别小的情况下,工艺偏差和噪声会掩盖硬件木马活动带来的旁路信号的影响。基于逻辑测试的方法是通过大量的测试向量激活隐藏在电路中的硬件木马,并与“黄金模型”的主输出响应值比较以判断电路中是否存在硬件木马[9-10]。但该类方法不能检测到不改变电路主输出逻辑值却通过改变电路内部的逻辑值破坏电路正常的工作的硬件木马。在本文中,针对很难通过传统的旁路信号分析法检测到的小型的硬件木马,本文方法具有显著的优点。

硬件木马的防插入方法主要体现在可信性设计方面。可信性设计(Design-for-Trust,DFT)技术是指设计者为了实现对芯片更加全面、准确的检测,在原始电路设计中加入一些额外的辅助电路提高硬件木马检测覆盖率或预防硬件木马的插入。该方法的优点不仅可以针对性地预防硬件木马的插入,而且可以节省检测成本,此外,该方法也可以与旁路分析检测技术、逻辑测试技术相互结合、相得益彰,共同组成更加全面的硬件木马检测架构。

现有的研究中简化硬件木马的检测[11-14]或预防硬件木马插入的可信任设计[15-17]显得更加的突出。电路中存在许多路径,每个路径代表整个电路特性的一部分,而且每个路径都有着自身的延时属性[18]。文献[11]中指出在整个电路中延时最大的路径称为关键路径。在不违反电路的时序约束前提下,攻击者在电路的关键路径中植入小型的硬件木马对电路的延时影响相对较小,通过基于延时的旁路信号检测方法更难以检测。因此,一个聪明的攻击者更倾向于在电路的关键路径上插入在特殊条件下激活并实施恶意功能的硬件木马。另外,文献[12]指出攻击者可能会选择转换概率较低的节点插入硬件木马,因为转换概率较高的节点所对应的逻辑门具有较大的活动性。不仅对电路的旁路信号影响较大,而且较容易通过逻辑测试法检测到硬件木马的插入。文献[12]以转换概率较低的节点作为构造锁存结构的目标节点,以此防止硬件木马在转换概率的目标节点插入。以上研究表明,电路中延时最大的关键路径及转换概率比较低的节点是硬件木马插入的重要目标。因此,针对关键路径和转换概率较低节点的硬件木马预防与检测是比较具有价值的研究点之一。

2 关键路径的实时监测方案

本文提出了一种针对电路关键路径的硬件木马实时监测方法,主要的目的是预防和检测小型的硬件木马在关键路径的插入。该方法将监测器插入电路关键路径的关键节点,监测器可以检测并报告目标节点及其相邻节点逻辑值的正确性,以此判断电路的关键路径是否插入了硬件木马。硬件木马可以不改变电路主输出,而是通过改变电路内部逻辑值,破坏电路正常工作。本文方法的主要优点是无需检测电路的主输出,可以实时监测电路关键路径的关键节点是否被硬件木马攻击。

2.1 电路关键路径的挑选

2.1.1 实时监测目标选择

电路中包含多条路径,不同的路径具有对应的延时属性。攻击者在关键路径中插入小型硬件木马对电路的影响较小,基于延时的硬件木马检测方法难以检测到硬件木马的插入。另外,电路中转换概率(Transition Probability,TP)较低的节点是攻击者优先考虑插入的目标。由此,本文把关键路径中转换概率较小的节点认为是硬件木马优先攻击的主要目标节点。假设电路有n条路径,分别记为P1,P2,…,Pn,各路径时延分别记为T1,T2,…,Tn,其中T1是时延最大的路径,Tn是时延最小的路径,那么T1路径称为电路中的“关键路径”;然后计算关键路径上所有节点的转换概率,转换概率较小的优先插入监测器。

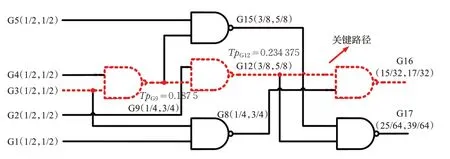

如图1所示是简单的c17组合电路,由节点G3、G9、G12、G16 节点组成的红色路径表示的是c17 组合电路中延时最大的路径。该路径上的G9、G12 节点作为实时监测的主要对象,由于G9 节点的转换概率TpG9=0.187 5 小 于 G12 节 点 的 转 换 概 率TpG12=0.234 375,所以在一定面积开销的约束下,优先选择G9节点插入监测器。实时监测的主要目标是电路的内部节点,由于电路的输入和输出是可控可观测的,且攻击者一般不会选择电路的输入和输出插入硬件木马,所以不作为实时监测的目标。

图1 简单的c17电路实时监测目标选择

2.1.2 电路节点转换概率计算

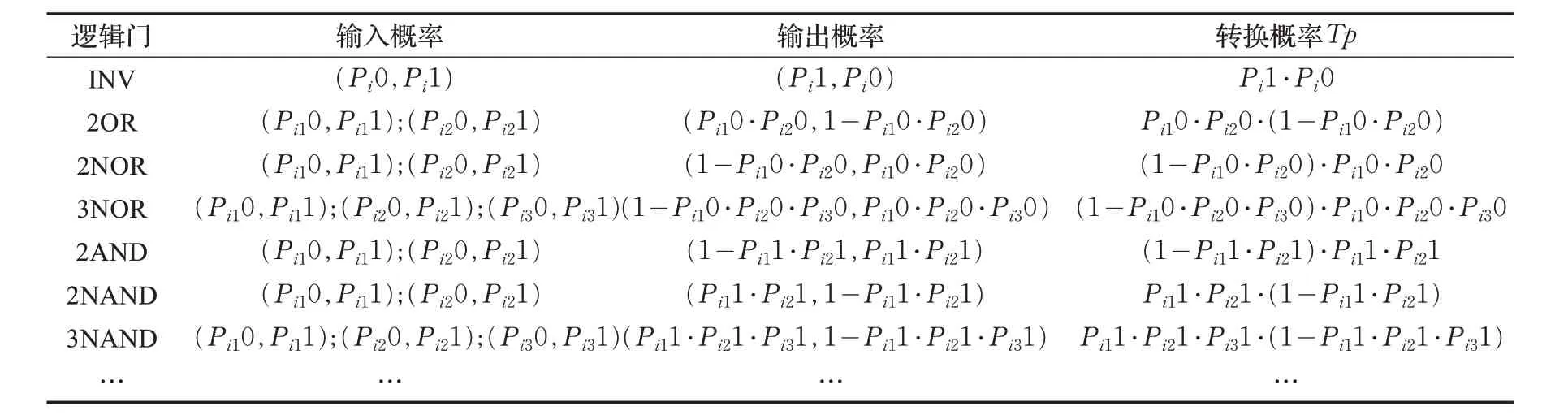

电路的输入逻辑值可能是“1”,也可能是“0”,如果随机向量数量趋于无穷大,那么电路的每一个主输入的逻辑值是“0”和“1”的概率均趋于1/2。由此,本文中把主输入的逻辑值为“0”和“1”的概率表示为(1/2,1/2)。电路主输入端的逻辑值概率根据逻辑门的类型进行传播,每种逻辑门的传播公式如表1 所示。根据电路的拓扑顺序,由传播公式可以计算得到各个节点逻辑值为“0”和“1”的概率(Pi0,Pi1)。进而可计算出该节点的转换概率:Tpi=Pi0×Pi1,即节点转换概率的计算公式。

2.1.3 电路关键节点选取算法

电路的关键节点选取算法伪代码如算法1 所示。首先输入电路的门级网表,并设定转换概率Tp 的阈值Th;然后根据电路门级网表的拓扑排序找到延时最大的路径,并用传播公式计算关键路径上所有节点的转换概率;最后统计低于阈值的节点集合,以此作为优先插入监测器的选择对象。

算法1电路关键节点选取算法伪代码

Input:The gate level netlist Ng,Tp threshold Th;

Output:The critical node list CNL;

1.Init circuit paramerters.e.g.initial duty cycle,gate delay time,etc;

2.Construct circuit logical structure C according to Ng;3.Topo sort the circuit strctrue C;

4.Forward Propagation: calculate the delay of each gate on topo-sort order;

5.Backward Trace:search path which have the lon‐gest delay as the critical path P;

6.Calculate transition probablity of each gate on the critical path P;

7.Select gate whose transition probability lower than Th as critical gate and put them into the critical gate list CNL;

8.return CNL

2.2 电路的实时监测

2.2.1 监测器结构

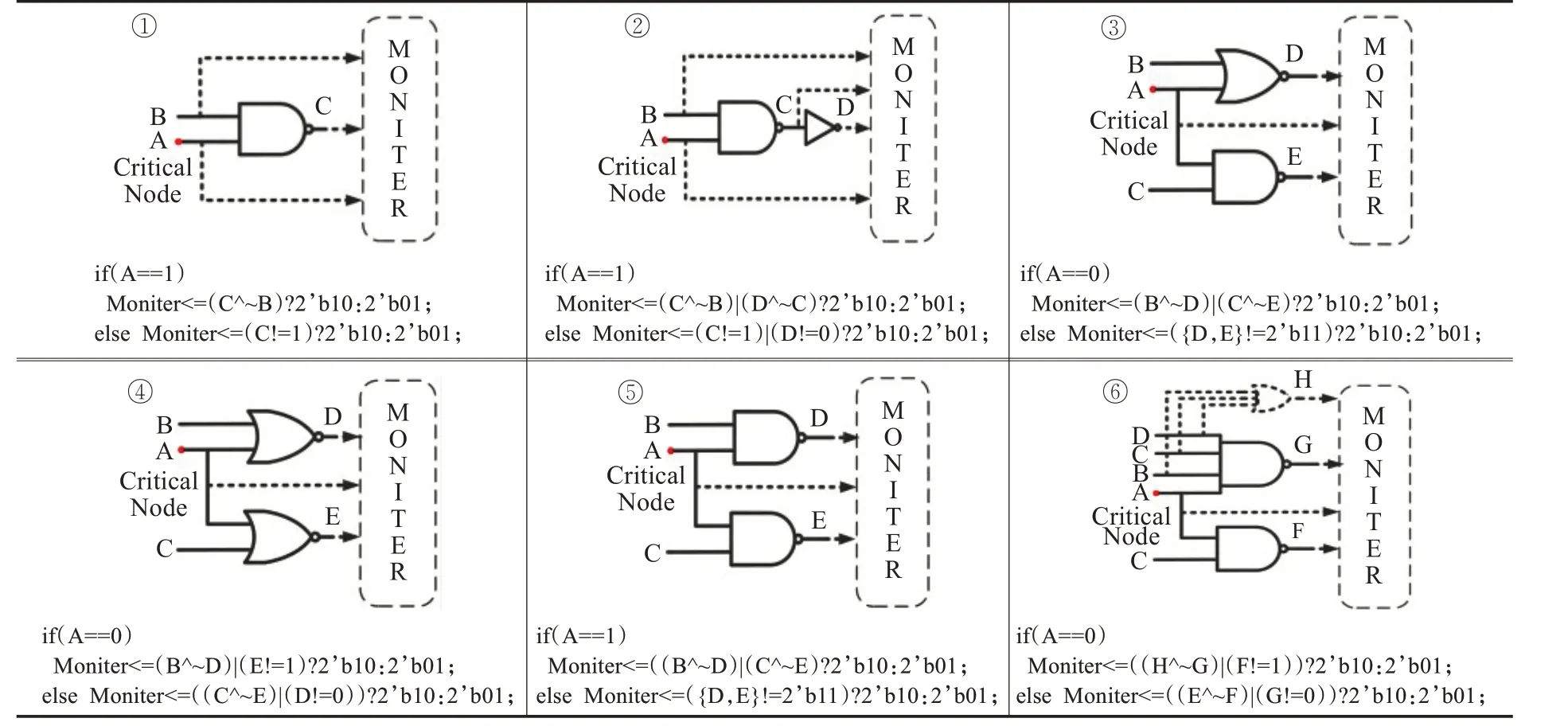

如图2 所示是具有相关性逻辑门组合的监测器结构原理图。红色节点A 表示的是电路关键路径的关键节点。关键节点连接的所有逻辑门的输出都与关键节点A 直接相关,由此对A 点相关的逻辑门进行监测,这样可以提高硬件木马的检测准确度。例如图2 中的⑤监测器,当节点A 的逻辑值为1 时,则相对应逻辑门的输出的正确逻辑值分别为D=~B 和E=~C;当节点A 的逻辑值为0 时,逻辑门的正确输出值D=E=1。如果攻击者在A 点插入硬件木马以修改其逻辑值,那么各个节点逻辑值的相关性会被干扰。通过监测器可以实时监测各个节点的逻辑值变化,并报告监测值与预期值的偏差。当节点A 无木马插入时,监测器的输出值为“01”;当检测到木马时,监测器的输出值为“10”;当监测器发生故障时,那么监测器的输出值为“11”或“00”,即监测器有自检功能。

电路关键路径的关键节点存在着多种类型逻辑门的连接,所以在插入监测器时,需要对关键节点有相关性的逻辑门进行分析,然后根据逻辑门的相关性,构建不同算法逻辑的监测器。如图2 中,根据关键节点的逻辑相关性列举了6 种不同算法逻辑的监测器。当A 关键节点无相关逻辑门连接时,监测器是检测A、B、C 节点的逻辑值相关性。当A 关键节点对应的是多输入逻辑门时,除关键节点外的其他节点决定了监测器H 端逻辑值的变化。如⑥监测器表示的是当A 关键节点对应的逻辑门是与门(与非门)时,则由(B&C&D)决定H 端逻辑值变化。同理,如果关键节点对应的逻辑门是或门(或非门)时,则由(B|C|D)决定H端逻辑值变化。

表1 电路节点转换概率的传播公式

图2 不同逻辑相关性的监测器

2.2.2 硬件木马和监测器的插入

聪明的攻击者通过选择电路关键路径的关键节点插入硬件木马。为了使插入的木马对电路的影响较小,一般攻击者会植入小型的组合硬件木马,其典型结构如图3 所示。该木马由一个“与”门和一个“异或”门组成,“与”门作为硬件木马的触发逻辑部分,“异或”门作为硬件木马的负载部分。当触发部分“与”门输入的逻辑值全为“1”时,则负载逻辑“异或”门把M 的逻辑值修改为~M。

图3 典型的小型组合硬件木马

图4 硬件木马和监测器的插入

如图4(a)是原始电路,红色的部分是电路的关键路径,假设G30 节点是电路的关键节点,该节点是硬件木马插入的主要攻击对象。图4(b)是插入监测器(蓝色虚线)的电路,假如攻击者在G30节点插入硬件木马(红色虚线),当G10 和G20 逻辑值同时为“1”时,硬件木马被激活,G30的逻辑值被修改为~G30。当G4逻辑值为“0”时,对于任何输入的测试向量,通过观测电路主输出的硬件木马检测方法,都检测不出电路中被激活的硬件木马。其原因是“与非门”掩盖了硬件木马触发的影响,而监测器可以检测到硬件木马的插入。由此可以类推到:如果一个电路中的硬件木马被激活,可能不会改变电路的主输出,但是会改变电路内部的逻辑信息,使电路内部功能紊乱。因此,对于只通过对比电路主输出的硬件木马检测方法,并不能有效地检测到关键路径的硬件木马,而监测器可以立即检测到硬件木马的激活。

2.2.3 实时监测的系统架构

如前所述,IC芯片的安全性和可靠性是构建电路系统架构的首要条件。从整个系统角度而言,芯片存在缺陷是不可避免的,一个芯片产生故障信号,可能是硬件木马引起的,也有可能是缺陷引起的。硬件木马是攻击者故意插入的,而缺陷是由于不完善的制造工艺产生的。具有相同缺陷的两个芯片的概率是非常低的。若攻击者把木马电路伪装成与工艺缺陷相同的故障信号,则会花费较大的成本。因此,针对多个具有相同故障信号的芯片被认为是感染硬件木马的芯片,故障信号完全不同的芯片是缺陷芯片。在监测器的系统架构中,可通过对多个芯片的检测,判断芯片发生的故障类型。但如果检测设备自身出现故障,则会导致检测结果发生错误,甚至会导致重大的事故。所以,具有自检功能的监测器对电路故障的检测尤为重要。

如图5 所示是电路的实时监测的系统架构图。电路中的每个监测器的输出信号为两位,所有的监测器的输出结果汇总于最终监测器,最终监测器形成两位输出f和g。如果电路中的任何一个监测器检测到硬件木马,最终监测器则会输出“10”;没有检测到木马,监测器输出“01”;若监测器发生故障,则最终监测器输出“11”或“00”。对于复杂的片上系统SoC 来说,监测器可以划分在其不同的IP核中,实时监测电路关键路径上关键节点逻辑值的变化。

随着电路规模的增大,传统的硬件木马检测方法对于小型硬件木马检测难度也随之增大,所以对于电路的关键节点的防护也尤为重要。本文所提的实时监测的系统架构在考虑电路规模与硬件木马不改变电路主输出的情况下具有明显优势。对于小型待测电路,应该适当合理安排监测器的应用数量,避免过大的面积开销。

3 实验结果与分析

如前文所述,在硬件木马检测方法中的旁路分析法由于其方法机制的原因,难以检测到小型硬件木马的存在。所以本文实验主要基于逻辑测试法进行了对比实验,证明基于文章所提监测器结构检测硬件木马的优势。

3.1 实验条件

本文实验基于45 nm 工艺库的ISCAS85 基准电路,采用C++语言编程实现电路的延时分析和转换概率的计算,实验平台VS2017。实验所用基准电路的网表是由Synopsys 公司的DC(Design Complier)综合得到,网表中只由INV、2-4 输入的NAND 及2-4 输入的NOR 基本逻辑门单元组成。其中,电源电压Vdd=0.8 V,温度设置为378 K。

3.2 实验结果分析

3.2.1 关键路径

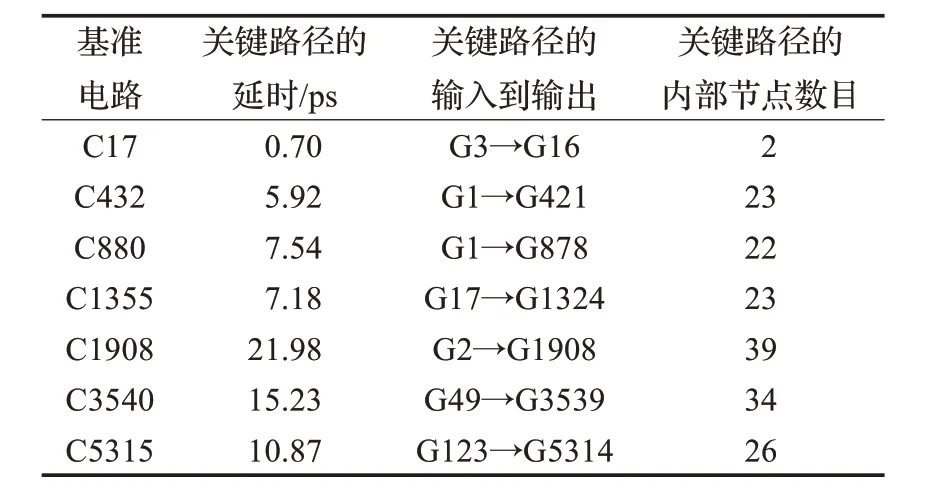

表2 所示ISCAS85 基准电路关键路径的选取结果。电路中存在多条路径,选取延时最大的路径作为关键路径,不同电路关键路径的节点数目以及各节点所对应的逻辑门的类型有所区别。所以需要根据关键路径逻辑门的类型设计监测器。

表2 ISCAS85电路的关键路径

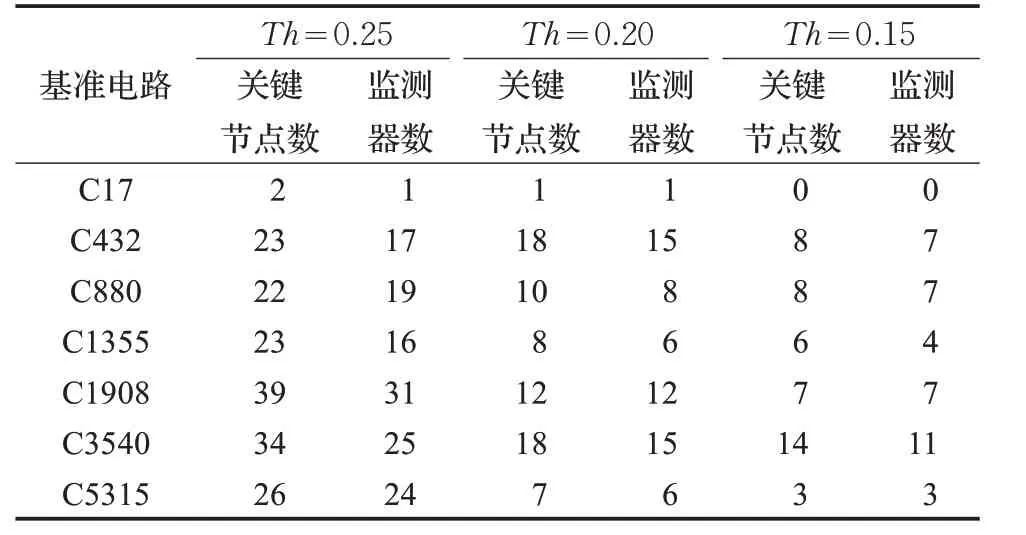

3.2.2 关键节点的选取和监测器的插入

根据关键路径各个节点的转换概率,设定合理的阈值,使插入监测器后的电路的面积开销控制在理想的范围内。转换概率小于(等于)阈值的节点称为“关键节点”。针对“关键节点”相关逻辑门的类型插入监测器,实时监测关键节点逻辑值的变化,以检测电路中是否插入硬件木马。如表3 所示是各电路在不同阈值下的关键节点的个数和插入监测器的数量。从表3 中可以看出,关键节点的数目和监测器的数量并非一致,这是因为电路的关键路径中包含有“非”门,构建监测器的原理如图2-②所示。

转换概率的最大值为0.25,当Th=0.25时,关键节点的数目等于关键路径上内部节点的数目。当阈值Th降低时,从表3 中可以看出电路中关键节点及插入监测器的数量也会随之减少。因此可以说本文的设计具有可控的面积开销。

表3 ISCAS85电路在不同阈值下的关键节点个数和插入监测器的数量

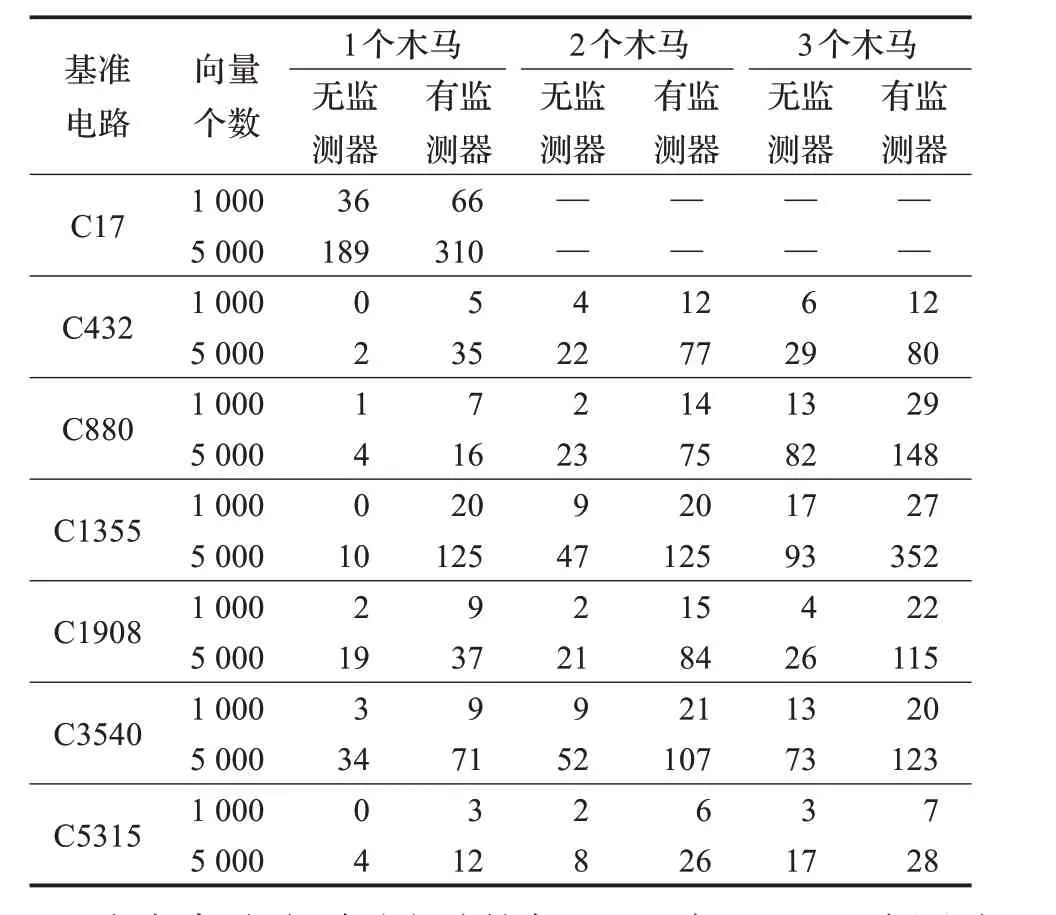

3.2.3 硬件木马的检测结果

本文基于ISCAS85电路,在转换概率阈值Th=0.25进行实验设计与结果分析。如表4 所示是有监测器与无监测器的硬件木马检测结果对比。从表中可以看出,没有检测器的电路,通过与“黄金模型”的主输出对比,检测电路中是否具有硬件木马。虽然该方法可以检测使电路主输出改变的硬件木马,但是检测不到某些已经激活的但不改变电路主输出的硬件木马,本文在2.2.2小节已举例阐述。由此,针对关键路径上的硬件木马检测也存在木马被激活但不改变电路主输出的情况。

表4 ISCAS85电路在Th=0.25的硬件木马监测与基于电路主输出的硬件木马监测结果对比

本文实验分别对电路施加1 000 个和5 000 个测试向量,统计在测试向量激励下检测到硬件木马激活的次数。如表4所示,关键路径中插入一个木马时,电路C432和电路C5315在1 000个测试向量激励下,无监测器的方法检测不到电路中有硬件木马的存在,而本文方法检测到电路中的有硬件木马存在的次数分别为5 次和3 次。当测试向量增加到5 000 或关键路径木马数量的增加时,从实验数据可以看出,无监测器和有监测器检测到硬件木马的激活次数差距明显地增大,也就意味着无监测器的方法检测不到硬件木马激活的次数增加。因此,本文方法针对关键路径硬件木马的检测具有更明显的优势,可以有效地检测到关键路径上激活的硬件木马。

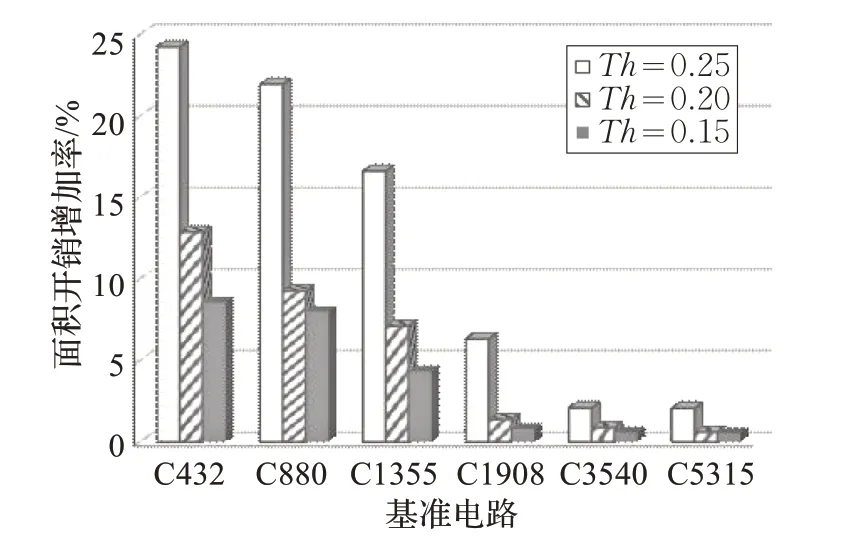

3.2.4 面积开销分析

如图6 所示是ISCAS85 电路在不同转换概率阈值下,插入监测器的面积开销增加率。当Th=0.25时,电路关键路径的所有内部节点皆是关键节点,所以电路插入监测器的面积开销最大。从图中可以看出,关键路径所有关键节点插入监测器的面积增加率最高不到25%,随着电路规模的增大,监测器所占面积开销的比例会越来越小。C17 电路的规模较小,对于监测器插入的面积开销分析不具代表性。除此之外,当转换概率的阈值减小时,监测器所带来的面积开销增加率明显降低。由此,可以通过设定转换概率的阈值,使插入监测器面积的开销控制在理想的范围内。

图6 不同阈值下插入监测器的面积开销

4 结论

本文针对电路的关键路径提出了一种硬件木马实时监测与防护的方法。同只检测电路主输出的逻辑测试法相比,充分考虑了电路中硬件木马的激活不改变主输出的情况。实验结果表明,本文方法不仅具有可控的面积开销,并且可以准确高效地实时监测电路关键路径上硬件木马的激活。在最多增加24.23%的面积开销下,可全面监测硬件木马在ISCAS85电路关键路径的插入,而且电路规模越大,电路相对面积开销率越小。