新型多相结构MWC宽带数字接收机设计*

陈 涛,蔡兴鹏,潘大鹏

(哈尔滨工程大学 信息与通信工程学院, 黑龙江 哈尔滨 150001)

随着高速模/数转换器 (Analog-to-Digital Converter, ADC)的不断发展,现代电子战对宽带数字接收机的需求越来越大[1-5]。然而,随着电磁环境的不断复杂化,雷达普遍开始采用大带宽的低截获率雷达信号[6],这对传统信道化宽带数字接收机提出了非常严峻的考验。传统信道化宽带数字接收机大多采用均匀信道化结构,其信道一经划分,各信道监测带宽就不可改变[7],在接收大带宽信号的时候会产生严重的跨信道问题,导致信道判决出错,生成错误的脉冲描述字信息,对后续的信号处理产生严重的影响[8-11]。

针对上述传统数字接收机亟待解决的问题,压缩采样理论给出了新的解决方案。Chen等[12-13]提出的基于压缩采样的调制宽带转换器构造(Modulation Wideband Converter, MWC)结构可对频域稀疏多带信号进行欠奈奎斯特(sub-Nyquist)采样,并推导出了基于MWC结构的压缩采样信号检测方法。Chen等[14]将MWC结构从模拟域扩展到离散域,推导得出了基于MWC结构的新型数字宽带接收机。Chen等[15]进一步通过MWC结构对欠奈奎斯特采样信号进行了频谱估计。文献[16]扩展了MWC结构的能力,提出了一个完整的欠采样雷达数字接收机。文献[17]利用MWC离散压缩采样数据,完成了基于压缩采样宽带数字接收机的脉内调制类型识别。文献[18]进一步提出了MWC均匀线阵结构,提高了MWC的灵敏度和重构精度。文献[19-21]分别研究了不同的MWC均匀线阵结构,完成了信号载频和到达角的联合重构。Rani等[22]从概念、原理、实现和应用等不同角度对现有的基于MWC结构的压缩感知系统进行了整体综述。

但是上述文献均采用了对ADC采样得到的离散数据,先混频再滤波最后抽取的MWC结构。在实际工程应用中,ADC的随路时钟往往处在一个很高的频率,导致现有MWC结构整体工作在较高的数据速率下。受限于现有现场可编程门阵列(Field Programmable Gate Array, FPGA)芯片的工作速率,现有的MWC数字接收机结构无法在FPGA端进行工程上的物理实现。

1 MWC数字接收机原理

文献[23]指出,电子侦察环境中的非合作信号通常在时频二维平面上是稀疏分布的,且现如今电子战战场中雷达发射信号均为脉冲形式,信号频谱不会充满整个监测频段,因此电子战接收机接收信号可以被视为频域稀疏信号,故可以使用MWC结构的宽带数字接收机对信号进行欠采样,再利用信号重构算法对原始信号进行恢复。

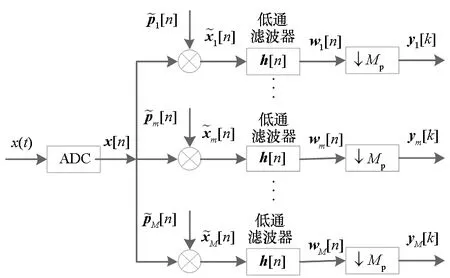

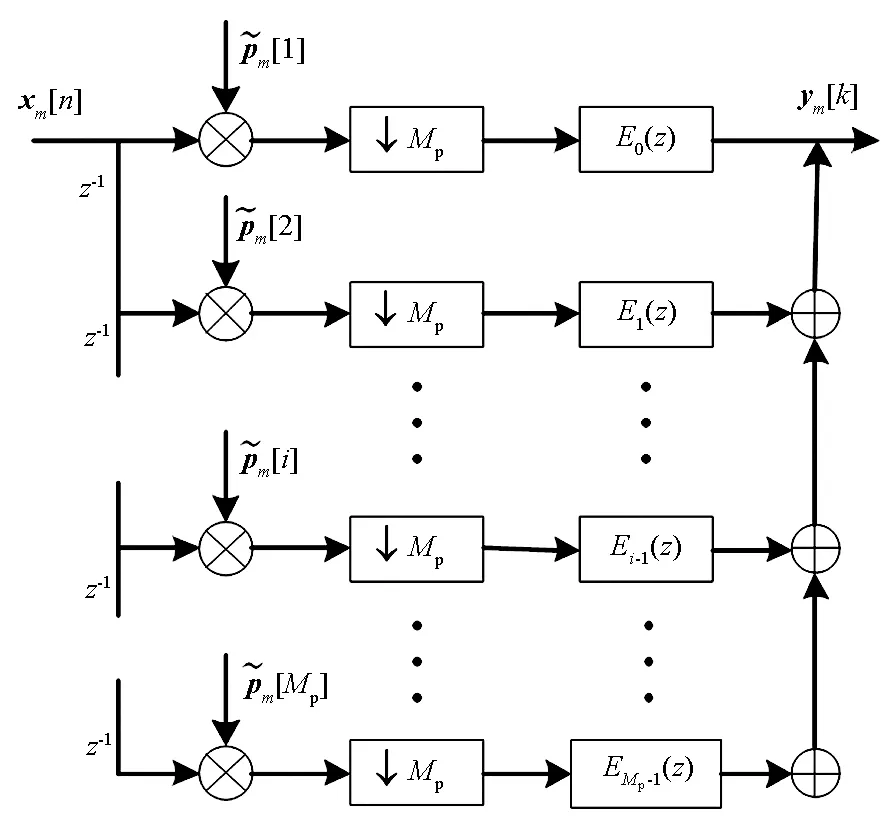

原型MWC结构离散压缩采样数字宽带接收机的总体结构如图1所示。该接收机处理信号为经过ADC采样后的数字信号,在各支路上离散数字信号经过伪随机序列(Pseudo-Random Sequence,PRS)混频后,其频谱被混频到所有子带上,选用低通滤波器进行滤波,再对滤波后的信号进行抽取,便可以得到MWC数字接收机输出的压缩采样信号。

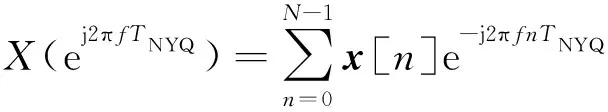

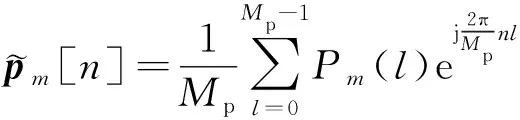

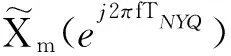

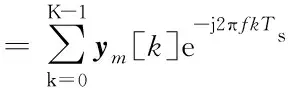

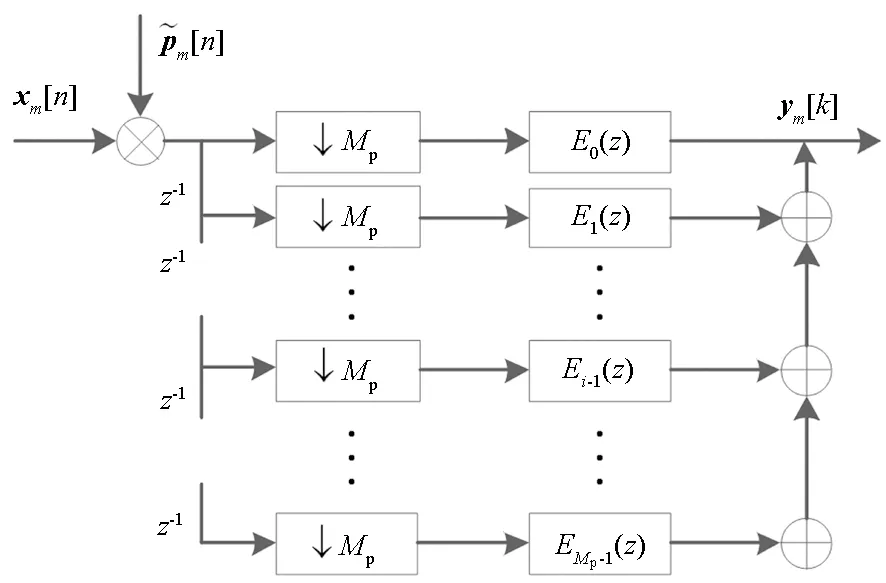

假设MWC压缩采样宽带数字接收机接收到的一个脉冲信号的离散数字模型如式(1)所示:

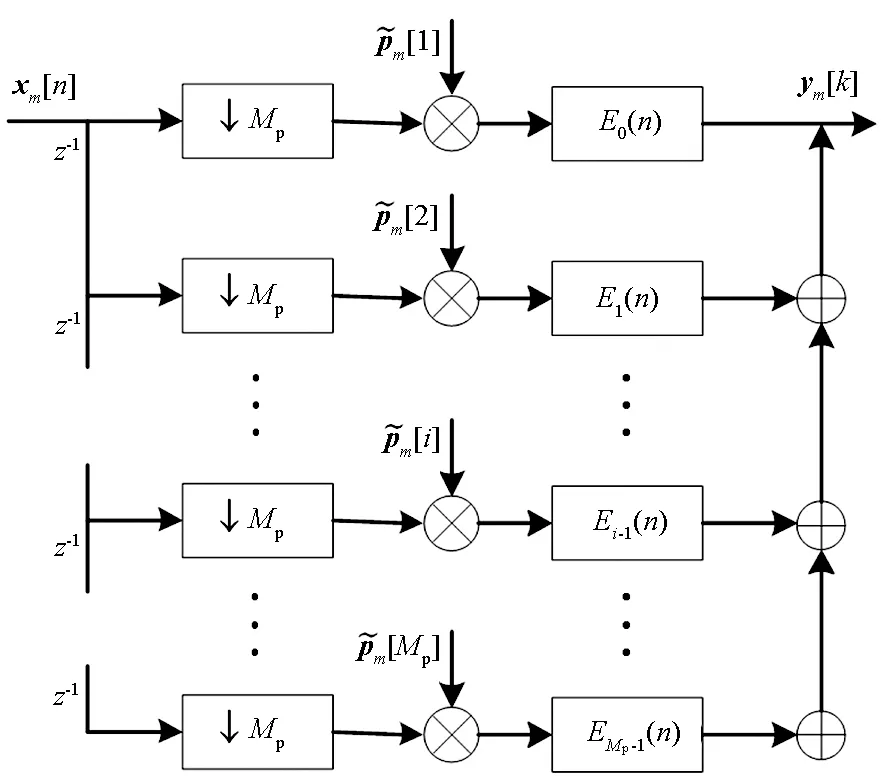

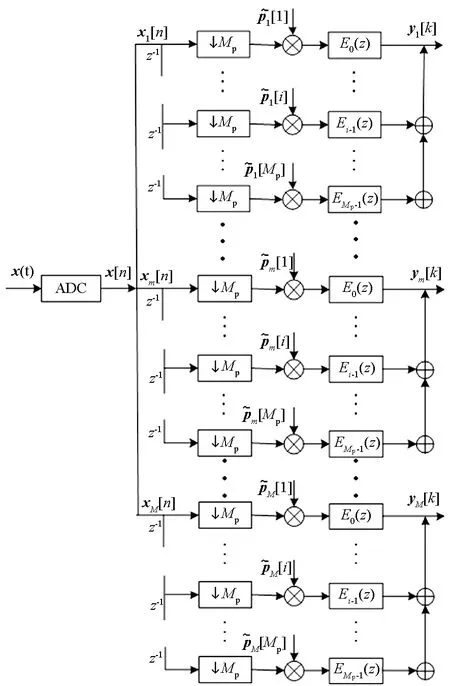

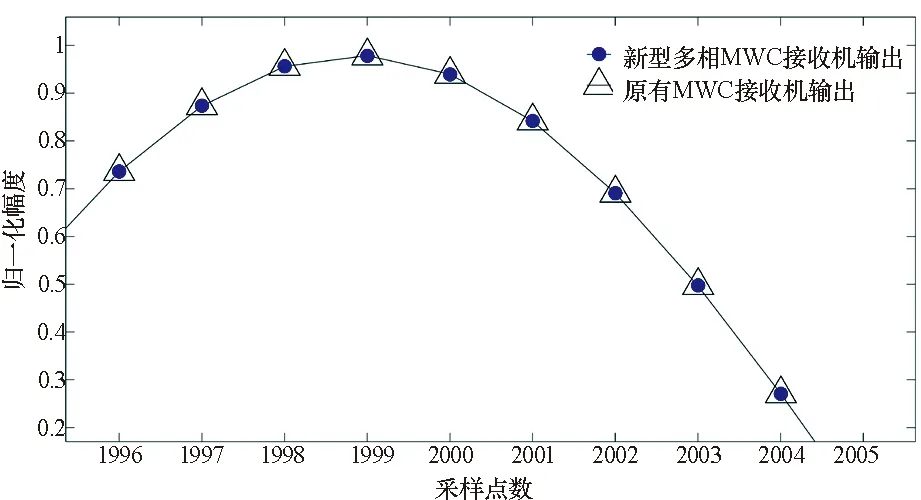

x[n]=s[n]+η[n], 0≤n (1) 式中,x[n]为接收机处理的采样信号,s[n]为采样信号中的有用信号,η[n]表示信号中的噪声,N为原始信号采样点数。则x[n]的离散时间傅立叶变换为: (2) 式中,TNYQ表示ADC采样时间间隔。 图1 现有MWC数字接收机总体框图Fig.1 Existing MWC digital receiver general block diagram 文献[14]提出的离散MWC数字接收机结构所采用的混频信号为循环移位的周期性PRS,其第m路的主值序列pm[n]与第1路的主值序列p1[n]之间存在如下关系: pm[n]=p1[n-m+1]MpRMp[n] (3) (4) 式中,l代表子带索引号。 (5) 之后对混频后的信号进行低通滤波,并对滤波后的信号进行Mp倍抽取操作,最终得到MWC一个支路输出。假设使用低通滤波器进行滤波,根据文献[16]可知,最终推导得到第m路输出为: (6) 为了保证后续压缩采样信号的完整重构,MWC压缩采样宽带数字接收机支路数需要满足如式(7)所示条件[24]。 M≥CKlg(Mp/K) (7) 式中:K为信号的频域稀疏度,M为支路个数,C为一个独立的正整数。 从图1中可以看出,现有MWC压缩采样数字宽带接收机的混频模块和低通滤波模块均工作在高速奈奎斯特采样频率下。这使得现有MWC数字压缩接收机虽然为后续数字信号处理节省了大量的冗余采样数据,但是整体接收机结构仍然工作在高速数据速率下。 本节将在现有MWC数字压缩接收机的基础上,利用低通滤波器抽取前移定理和混频伪随机序列的周期特性,推导得到多相MWC结构的压缩采样宽带数字接收机。与原型接收机结构相比,在消耗相同乘法器资源的情况下,可以大幅降低接收机工作时的数据速率,使其可以在FPGA端进行物理实现。 假设MWC结构中低通滤波器单位脉冲响应为h[n],则其Z变换可以表示为: (8) 对式(8)进行Mp倍的抽取可以得到其多相形式如式(9)所示。 (9) 记 (10) 则可将式(9)变换为式(11)的形式。 (11) 若将M倍的抽取器前移到滤波器之前,则滤波器的变量z的幂会减少M倍[25]。因此,将现有MWC结构中的Mp倍抽取器前移到多相形式的低通滤波器之前,则可以得到抽取前移后滤波器单位脉冲响应的Z变换为: (12) 因此,得到单支路的多相MWC滤波抽取前移结构图如图2所示。 图2 单支路多相滤波抽取前移示意图Fig.2 Single polyphase filter extraction forward shift diagram 由于原型MWC压缩采样接收机中,混频序列具有周期性,其周期为Mp。这说明,对于该接收机某一支路来说,信号每隔Mp个点所乘的数是相同的,即为该支路混频序列主值序列中的第i个元素。所以将MWC结构中各支路PRS的主值序列所有Mp个元素与多相低通滤波器中的对应项并行排列,即可构成新的多相MWC结构。新多相结构的单位脉冲响应的Z变换如式(13)所示。 (13) 若定义: (14) 则仍可以将多相结构的单位脉冲响应的Z变换表示成式(12)的形式。从而得到如图3所示的新多相结构。 从图3中可以看出,原结构中的混频模块实现方式变为输入信号各点与该路PRS的主值序列各点并行相乘,而主值序列中元素均为已知常数,因此,根据数乘的交换律,可以再次将抽取模块提前到混频模块之前,最终得到如图4所示的单路压缩采样宽带数字接收机的多相结构形式。 图3 新型多相结构框图Fig.3 Diagram of the new polyphase structure 图4 单路新型多相MWC接收机支路框图Fig.4 Single branch diagram of new polyphase MWC receiver 考虑到接收机输出数据需要M个支路来进行信号重构,因此考虑M路结构模型,推导出M路新型MWC压缩采样接收机如图5所示。 图5 新型多相MWC接收机整体框图Fig.5 Global diagram of new polyphase MWC receiver 从图5可以看出,与图1的现有MWC宽带数字接收机结构相比较,本文提出的多相MWC结构宽带数字接收机使用的乘法器资源相同,但各支路的工作数据速率下降到原结构工作速率的1/Mp倍,因此本文接收机结构更易于在FPGA端进行实现。 本节利用MATLAB对第2节中推导得到的新型多相MWC压缩采样宽带数字接收机结构进行仿真,将其输出与现有MWC压缩采样数字接收机的输出进行对比,从而验证新结构的正确性。 仿真采用fs=2.24 GHz的采样频率对载频为720 MHz的常规单载频雷达信号进行采样。将采样得到的离散化数据分别输入抽取倍数Mp=128的现有MWC宽带数字接收机和新型多相MWC宽带数字接收机中,得到的输出结果如图6所示。 图6 两种数字接收机输出结果对比Fig.6 Comparison of two digital receivers′ output results 图6给出了改进后的新型MWC结构宽带数字接收机单路输出和原始MWC结构宽带数字接收机单路输出的对比。其中用三角形表示输出数值点的黑色曲线为原始MWC压缩采样数字接收机的输出,用实心圆表示输出数值点的蓝色曲线为基于多相结构的新型MWC压缩采样数字接收机的输出。从图6可以看出,两者的输出完全相同,从而验证了改进后的基于多相结构的新型MWC结构宽带数字接收机的正确性。 相比原型MWC压缩采样宽带数字接收机结构,本文推导出的多相MWC压缩采样宽带数字接收机结构,可以有效地降低整体工作数据速率,更易于在FPGA上进行实现。 本文提出的多相MWC结构的数字宽带接收机结构更具有实际工程应用价值。利用将现有MWC数字接收机结构抽取模块不断前移的改进方法,在整体结构最前端将高速串行数据转换为低速并行数据,使结构从理论推导扩展到物理可实现,提供了新型宽带数字接收机的设计理念。

2 新型MWC数字接收机结构推导

2.1 多相滤波抽取前移

2.2 新型多相结构

3 仿真实验及分析

4 结论