一种基于FPGA的模拟潜艇噪声信号产生模块的设计

漆万鹏,刘天华,晏生剑

(1.海装驻武汉地区军事代表局,湖北 武汉 430000;2.海装驻宜昌地区军事代表室,湖北 宜昌 443003;3.中国船舶重工集团有限公司 海声科技有限公司,湖北 宜昌 443005)

0 引言

隐蔽性在潜艇作战效能中起着决定性作用。水声支援干扰系统,其使命是通过逼真模拟潜艇目标声谱特征及行为特性,形成对敌反潜预警系统和人员心理的干扰及欺骗,提升潜艇作战效能。

通常情况下,水声支援干扰系统是由信号处理机完成声特征谱信号的算法实现,信号产生模块实现信号的数模转换,功放模块实现信号的功率放大,换能器实现信号的电声转换。为了灵活适配各类平台,方便系统前期方案验证和效能评估,必须降低系统复杂度。功放模块和换能器是发射系统不可缺少的2个环节,所以将信号处理机与信号产生模块合二为一是比较理想的解决方案。本文介绍了一种基于FPGA的模拟潜艇噪声信号产生模块,综合了信号处理机与信号产生模块二者的功能,既能实现声特征谱信号生成算法,又能实现数字信号的数模转换。

该信号产生模块根据上位机下发的参数命令可以实时产生线谱、调制谱和宽带噪声信号,信号经过合成运算、匹配滤波后,再通过高频、中频、低频3路D/A通道输出,控制发射系统产生模拟潜艇噪声信号。

1 组成及工作原理

1.1 硬件组成

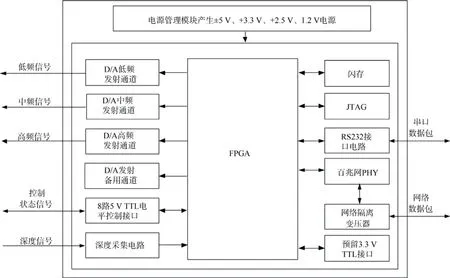

信号产生模块硬件电路主要由供电电路、FPGA主控电路、串口通信电路、以太网通信电路、深度采集电路、D/A输出电路、TTL信号控制电路组成,如图1所示。

图1 硬件组成框图Fig.1 Hardware composition block diagram

1.2 工作原理

信号产生模块需要根据上位机下发的命令参数实时产生相应的模拟潜艇噪声信号。模拟潜艇噪声信号的特征需要通过信号发射系统(功放发射模块和换能器)实际工作的频率特性来进行调整,信号产生模块根据反复测试后确定的参数产生模拟潜艇噪声电信号,再经发射系统发射出逼真的模拟潜艇噪声水声信号。

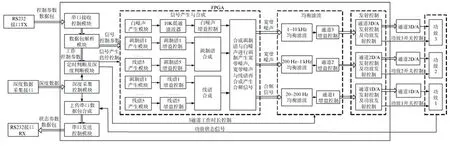

FPGA系统接收到命令参数数据包后,将命令参数数据解析为信号控制参数和工作控制参数。

信号控制参数包含的信息有白噪声的增益控制、开关控制;每根线谱的起始频率、截止频率、调频时间、增益控制、开关控制;每根调制谱的起始频率、截止频率、调频时间、增益控制、开关控制;各发射通道的增益控制、开关控制。通过信号控制参数可以确定白噪声的增益特性,线谱数量、线谱频率特性、线谱增益特性,调制谱数量、调制谱频率特性、调制谱增益特性。然后将白噪声、线谱、调制谱进行合成生成宽带噪声和合频信号。此时的宽带信号和合频信号与发射系统不匹配,需根据各发射通道实测的频率特性进行均衡滤波,最后经发射控制模块输出给功放,以达到模拟潜艇噪声信号的真实性。

工作控制参数包含的信息有系统启动总延时,深度开关设定值、深度开关启停、达到指定深度后延时、各发射通道工作时长、任务编号。如果深度开关停止,则系统根据系统启动总延时定时,定时完成后启动信号产生与合成模块。如果深度开关开启,则系统启动总延时、定深启动、达到指定深度后延时同时工作,深度后延时定时器在达到指定深度后才会开启,与系统启动总延时定时器并行工作,以2个定时后定时完成的控制信号作为信号产生与合成模块启动标识。各发射通道工作时长定时器在信号产生与合成模块开启后开始工作,定时完成后关闭均衡滤波模块停止信号输出。该系统可以同时设置3组参数存储在FPGA的RAM中,每组参数的编号通过参数编号选项区分,参数的工作顺序为编号1、编号2、编号3。信号产生模块工作原理如图2所示。

图2 工作原理框图Fig.2 Working principle block diagram

2 硬件电路设计

FPGA是本电路中的核心控制器件,串口协议解析,各种信号实时产生,信号合成,滤波器实现等均由其实现。电路中选择 ALTERA公司飓风 3系列EP3C40F324I7作为控制器件[1]。

网络传输功能是本设计中预留的功能,为后期信号处理机控制信号产生模块做准备。该电路主要实现百兆以太网全双工网络通讯。百兆网络物理层采用以太网芯片 DP83640实现,与 FPGA内部MAC控制器通过MII接口连接。

D/A芯片选用TI公司的16位分辨率的D/A芯片DAC8830ICD,输出信号先经过1级电压跟随电路增加驱动能力,然后经过电容隔直流电压[2],接着通过1阶RC低通滤波器进行平滑虑波,最后通过差分运放THS4130放大输出[3]。

RS232通信选择MAXIM公司的低功耗收发器MAX3227。选用表压型深度传感器,由 ADS8320采样得到深度数据。控制输出、状态输入接口使用电平转换芯片SN74LVC2T45实现3.3 V与5 V TTL电平转换系统输入电压为±8 V,需要产生±5 V,+3.3 V,+2.5 V,+1.2 V共5路稳定电源。+5 V和+3.3 V电源选用LINEAR公司的DCDC芯片LT3991产生。+2.5 V和+1.2 V电源电流需求较小,选用LINEAR公司的VLDO芯片LT3022产生。-5 V电源选用TI公司的负输入电压LDO芯片tps7a3001产生。

3 FPGA片内逻辑设计

3.1 白噪声的实现

伪随机序列是人为构成的数字序列,只包含高低2种电平,它是离散的,不具有真正的正态分布特性,但当序列的长度逼近无限大时,它趋于正态分布[4]。

本设计中数字白噪声是使用63位移位寄存器产生的m序列伪随机码实现。移位寄存器noise的初始值为63位2进制数63'h491290201840B084(16进制表示方法),移位寄存器每个时钟周期右移一位,将移位寄存器第 0位 noise[0]与第 1位noise[1]进行异或运算,运算结果赋值给第 62位noise[62],此运算方法作为m序列特征多项式。

因为使用D/A芯片为16位分辨率,所以M序列输出也定义为16位寄存器。将移位寄存器noise的低16位noise[15:0]作为M序列输出,即得到16位白噪声数据。

3.2 线谱的实现

线谱信号为单频或者调频的正弦信号,可以使用Altera官方提供的NCO IP Core来实现。NCO IP Core即数字压控振荡器知识产权核可以通过多种算法实现一个离散的正弦波信号输出[5]。正弦波信号时域方程如下:

式中:T为该模块的工作时钟周期;f0为输入频率控制字φINC设置的未调制的输出信号频率;fFM是调制频率控制字φPM决定的调制频率;φPM为该输出正弦波的调制相位,,由输入控制字p的比特位数pwidth决定它的精度;φDITH为模块内部自身的不稳定而引起的相位杂散(噪声);幅值 A=2N-1,其中N为幅值精度,取值在4~32之间。

f0与频率控制字φINC满足以下关系:

式中:M为相位累加器精度;fclk为模块工作时钟频率。

输出信号频率精度:

通过Altera公司的FPGA编译软件 QuartusII 12.0 中的MegaWizard Plug-In Manager 功能调用NCO V12.0 软核,配置软核中相应参数,根据式(1)-(3)来实现所需要的频率输出功能。NCO软核的实现选择 CORDIC算法,相位累加器精度设为24位,输出幅值精度为16位,输入时钟频率为340 kHz。CORDIC算法实施方案选择串行模式,目标器件选择Cyclone III,1路NCO通道,1路频率预置分支,单路正弦信号输出。

NCO模块信号输出是连续变化的,不随φINC设置值发生改变而间断。为了实现NCO模块的线性调频信号输出,需要等时等量的改变φINC设置值。

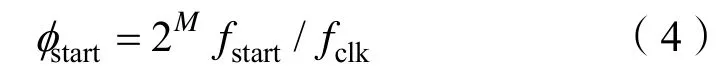

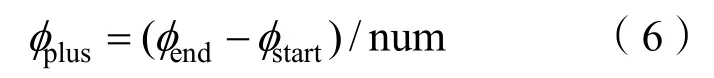

信号频率从fstart到fend线性变化,信号输出时间宽度为φwidtht,每1 s改变INCφ设置值,则INCφ变化次数为 n um =twidth/1s 。根据关系式(2)得,起始频率fstart对应的φINC设置值为

截止频率fend对应的φINC设置值为

每1 s后φINC设置值步进量为

收到信号控制参数后,首先根据式(4)-(6)分别计算出线谱产生的起始频率、截止频率和每秒频率增量,然后将 NCO模块的复位信号nco_reset_n拉低,对NCO模块进行初始化,使能NCO模块时钟使能信号nco_clken。然后将φstart赋值给NCO模块的相位累加寄存器nco_pfi_inc_i,输出起始频率正弦信号,等待1 s将φstart与φplus相加值赋给 nco_pfi_inc_i,输出下一个频率递增的信号,像这样连续输出(num-1)个频率递增的正弦信号就实现了调频线谱信号输出。如果设置的调频信号的起始频率与截止频率一致,则输出为固定线谱。

3.3 信号合成与宽带噪声的实现

宽带噪声是多根调制谱信号(单频或者调频的正弦信号,与线谱实现方式一致)相加与白噪声调制出来的宽带谱信号,是白噪声信号与调制谱信号运算的结果。合频信号是多根线谱信号与宽带谱信号相加的结果。

因为单根线谱、调制谱信号均为16位有符号数,5根线谱、调制谱信号相加有溢出的可能,为了避免数据溢出,将16位有符号数转换为19位有符号数,然后将 5根线谱、调制谱分别相加得到线谱合信号s_sum,调制谱合信号 t_sum。根据有符号数移位方法,正数溢出取最大值,负数溢出取最小值,将调制谱合频信号转换为16位有符号数t_sum_buf[6]。

将(t_sum_buf+16’h8000)的16位无符号数调制谱合频信号与16位有符号数白噪声noise_buf相乘,根据有符号乘法运算方法,根据noise_buf的符号位来分别进行无符号数乘法运算,结果为32位有符号数t1_noise。然后换算为16位有符号数,得到用于中频、高频通道输出的宽带噪声信号t_noise,然后将线谱s_sum与t_noise相加,并转换为16位有符号数便得到用于低频通道输出的合频信号。

3.4 均衡滤波的实现

均衡滤波的目的是为了弥补发射系统不同频带发射响应的不一致性,尽量使发射系统发射响应一致,逼近真实的潜艇噪声情况。均衡滤波的实现即在 FPGA内部实现与发射系统相匹配的数字滤波器。根据单位冲激响应函数的时域特性,数字滤波器可分为IIR滤波器和FIR滤波器,这里使用具有线性相位的FIR滤波[7]。

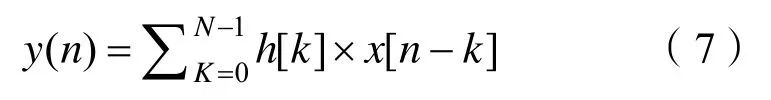

FIR有限脉冲响应滤波器的特点是单位脉冲响应是一个有限长序列,其数学表达式为

式中:N表示FIR滤波器的抽头数;y(n) 表示第n时刻的输出样本;h(k) 表示FIR滤波器的第k级抽头系数;x [n-k]表示延时k个抽头的输入信号。用加法器和乘法器不难实现这种结构的FIR滤波器,传给每个乘法器的操作数就是一个FIR系数。所需乘法次数是N,加法次数是N-1。

数字滤波设计中最关键的部分为 FIR滤波器的实现和滤波器系数的设计。FIR Megacore 是ALTERA公司针对其主流 FPGA推出的一款商业化的数字滤波器IP核,可直接生成HDL代码,同时其结构针对ALTERA自己的FPGA做了各种优化。FIR Megacore提供了滤波器系数导入功能,可以使用第三方工具生成的系数,这使得我们能够通过FIR Megacore调用计算出来的滤波器系数快速实现均衡滤波。

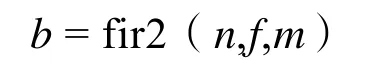

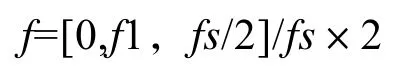

滤波器系数需要根据发射系统实际的发射响应来设计、调整。根据系统发射相应数据我们可以使用Matlab fir2函数来快速设计滤波器系数:

式中:n代表生产的滤波器阶数;f为归一化的频率向量;m为与f对应的归一化幅度向量;b即为根据频率向量、幅度向量对应的幅频特性所生成的n阶滤波器系数[8]。假设滤波器采样频率定义为fs,实测数据的频率向量为 f1,与之对应的幅度向量为m1(dB),那么归一化的频率向量为

归一化的幅度向量的转换应先找到最小幅度值m1_min,计算各频点将到最低幅度值的衰减量:

按频率向量长度补齐幅度衰减量向量:

最后将幅度衰减量向量值换算为增益倍数值,即得到归一化的幅度向量

滤波器阶数 n的确定与均衡滤波的性能直接相关。滤波器频率分辨率为fs/n,滤波器阶数越高,频率分辨率越小,但滤波器系数数据量也越大,占用更多FPGA资源。所以滤波器阶数需要根据实际应用情况来决定,既要保证均衡滤波效果,又不浪费过多FPGA逻辑资源。本设计中,采样频率fs=20 kHz,滤波器阶数n=1 023,滤波器频率分辨率接近20 Hz,可以满足均衡滤波需求。

4 试验结果

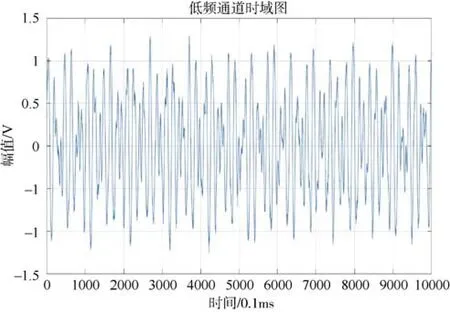

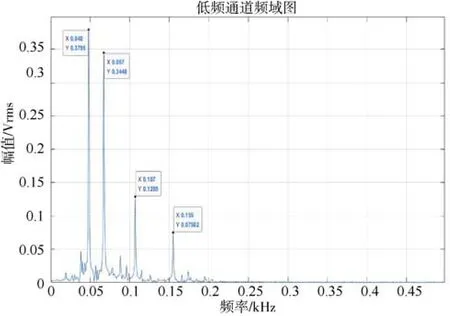

上位机软件参数设置为:通道 1开启、增益-6 dB;白噪声开启、增益-6 dB;线谱1开启、频率48 Hz、增益-3 dB;线谱2开启、频率67 Hz、增益-6 dB;线谱3开启、频率107 Hz、增益-9 dB;线谱4开启、频率155 Hz、增益-12 dB。使用示波器测量低频输出通道,设置示波器采样率为10 kHz,信号稳定后抓取1 s的数据通过网口上传到上位机,使用MATLAB对数据解析,信号时域波形如图3所示。

对采样数据做FFT分析,将低频段展开后如图4所示(纵坐标为有效值)。线谱的频率分别为48 Hz、67 Hz、107 Hz、155 Hz与设置参数值吻合,并且信号幅度依次变小,与增益设置值相符,由于信号经过匹配滤波,所以幅度与设置增益值有一定差别。

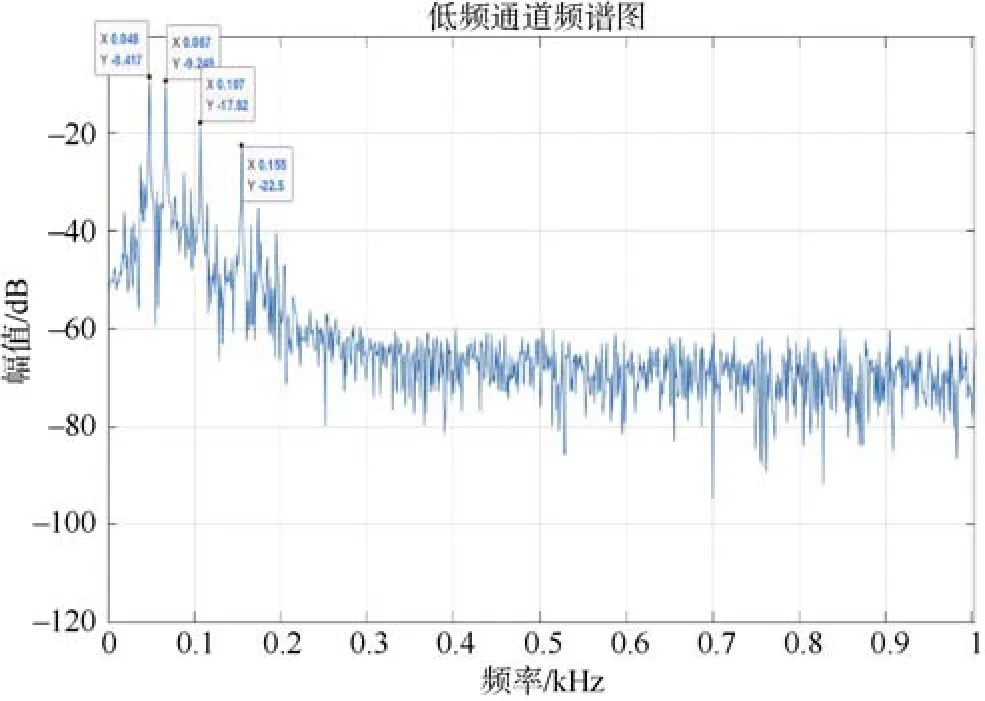

信号频谱图如图5所示(纵坐标为dB),可以看到设置的4个线谱,20~200 Hz的带通滤波器及带内均衡滤波造成的频谱起伏。

图3 时域波形Fig.3 Time domain waveform

图4 低频段频谱图Fig.4 Low frequency spectrum

5 结束语

该信号产生模块实现了声特征谱信号生成算法,降低了水声支援干扰系统的复杂度,缩短了项目周期,提高了水声支援干扰系统的适装性,已成功应用到多个预研课题,并顺利完成湖上试验。应用该信号产生模块,能为项目前期方案验证和效能评估提供便捷,同时该模块预留网络接口,可以与信号处理机连接,实现更复杂的模拟目标声特征谱信号产生。

图5 全频段频谱图Fig.5 Full-band spectrogram