基于DDS技术的LFM信号产生与FPGA实现

陆 聪杨维明卫春芳

(1.湖北大学 计算机与信息工程学院,武汉 430062;2.湖北大学 知行学院,武汉 430011)

0 引言

在通信与雷达系统中,为同时提高系统的探测距离和距离分辨率,通常对发射信号进行调制,一般采用脉内调制,脉内调制的方法包括线性调频、非线性调频及相位编码,线性调频信号(LFM,Linear frequency modulation signal)具有稳定性好和易于产生和实现的优点,因而得到广泛应用。现有的线性调频信号的产生主要基于频率合成等相关技术方法,在这些方法里面,直接数字频率合成(DDS,Direct Digtal Synthesis)方法解决了模拟频率合成的瓶颈问题,根据“相位”的角度考虑来实现频率的合成。DDS能够输出多种频率和初始相位不一样的正弦波,除此以外还能够输出多样化的波形,有着相位角度广、频率解析率高、频率切换时间短和优良的可复制性能等优势,正因以上优势使其成为现代频率合成技术的首要选择。

已经具备的DDS方法一般以特定的芯片来进行设计,如高集成器件AD9854等,但是这种方法会增加硬件研发费用,此外会让设计方案丧失一定的灵活性。当今集成芯片飞速发展和微电子制造工艺的迅猛提升,使得FPGA芯片的晶体管集成度以及运行频率不断上升,片内逻辑单元更加充足,此外FPGA的可编程特性让信号发生器的硬件方案设计更加方便快捷。本文侧重于分析线性调频信号的DDS实现技术与采用FPGA实现DDS的设计方案。

1 基于DDS技术的LFM信号产生理论

1.1 LFM信号分析

LFM信号凭借多普勒频移不敏感的优势被应用于大量设计案例,在信号被处理时,若回波信号有着较强的多普勒频移效应,通过预先设计的匹配滤波器依旧能够输出较理想的脉冲压缩信号,故有效避免了信号被处理时候的绝大多数问题。

LFM的信号频率对时间的求导结果为常数:

(1)

式(1)中f(t)代表信号的瞬时频率,u代表信号的调频斜率,与此相对应的瞬时相位函数表示如下:

(2)

时间宽度T的复数信号函数表示如下:

s(t)=u(t)exp(j2πf0t)=

(3)

式(3)中u(t)是信号的复包络,u=B/T表示频率的变化速度,B表示信号的频带宽度,T表示信号的时间范围,f0表示中心频率。假设f0为0,此时表示零中频信号,也就是基带信号,此外复信号的实部与虚部对应两种不同的正交信号。

(4)

由LFM信号的相位调制表达式可推出相位与时钟两者之间的关系。若时钟频率设置为50 MHz,也就是时钟周期为20 ns,LFM信号的带宽20 MHz,脉冲宽度为T=10 μs,此时频率的变化速度u=B/T=2×1012,瞬时相位对应表示为:

θ=πμt2=6.28×1012×t2

(5)

若时间t进行离散化:t=n×20ns,n=0,1,2,3… 代表时钟周期次数,可得:

θn=2512×n2×10-6

(6)

在FPGA芯片上通过Verilog编程语言来完成相位调制时,可采取有符号数的乘法器来快速实现。

若LFM信号带宽B设置为10 MHz、时宽T设置为2.5 μs,其相应的LFM信号波形图和频谱图如图1。图1中可知,LFM信号频率呈现出线性增加的趋势,此外时间带宽积越大时,信号幅度谱更加呈现出矩形的趋势。

图1 LFM信号的幅频特性

1.2 LFM信号的DDS产生理论

1.2.1 DDS基本原理

DDS为最近几年用于输出稳定LFM信号的便捷设计方案,采用DDS设计的频率合成器具备全数字化的特点。通过正弦波例子来分析DDS原理,首先把需要输出的波形数据提前存放在ROM(或RAM)里面,再根据系统时钟(CLK)频率,采取顺序读数从ROM(或RAM)里面获取波形数据,最后通过D/A转换后能够接收到特定频率的输出波形。正弦波单个周期360°的范围中,依据相位将其等分为若干份Δφ,并把这些相位相对应的振幅A转换为二进制进格式后存放到ROM,若Δφ=6°,单个周期等分成60份。鉴于正弦波单个周期中的对称特性,故ROM仅需要存放0~90°的幅值即可。假设Δφ=6°,则 0°~90°可以等分为15份,波形对应的幅值存放于ROM中占用16位地址,采用4位长度的地址码来进行ROM表寻址,幅值码表示为5位的编码,正弦波单个周期0°~90°的编码数据如表1。

表1 正弦信号相位与幅度的关系表

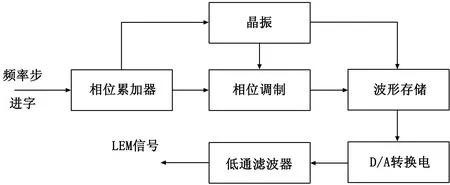

结合以上原理,设计生成DDS信号的结构图如图2,主要由相位累加器、晶振、相位调制、波形数据存放、D/A转换电路和低通滤波器等模块构成,其中晶振用于为FPGA系统提供稳定的时钟信号,保障其他模块的有效性。

图2 DDS信号产生原理框图

1.2.2 信号的频率关系分析

取fc为信号的频率,在时钟信号CLK的驱动下,依据表1的地址编码顺序依次读出ROM中存放的幅值编码数据,此时正弦信号的频率记为fo1。若间隔一个地址编码依次获取数据,此时频率记为fo2,信号频率满足fo2 =2fo1。根据此规律可完成直接频率合成器输出频率可变的设计。

以上设想可基于控制电路完成,通过控制电路的输出结果来选取ROM地址(对应为正弦波的相位)。输出信号波形是通过相位依次累加而得到的,即DDS实现方案中的非常重要的一部分——相位累加器。在图2中,若设置频率步进字FW为1,即单次累加输出的增加量为1,也就是按照地址码顺序从ROM中获取信号数据;当FW取2,表示间隔一个ROM地址获取数据;依次可得,FW反映出相位步进速度,设置越大速度越快,得到得信号波形频率就更高。

当CLK频率固定时,得到信号的最高频率可达到何值?换言之,在n位寻常的ROM范围中,K值最大该取何值?n位地址存在2n个ROM地址,一个正弦波里取2n个数据。设置FW为2n时候,即相位步进值是2n,但是单个周期信号中仅取一个数据无法表示一个正弦波,故取FW=2n不合理;取FW=2n-1,一个正弦波存在两个取样数据时满足取样定理,但是这种方案很难实现。通常取FW≤2n-2,此时一个波形最少存在4个采样数据,通过D/A变换后相当于4级阶梯波。然后在后续低通滤波器的处理下,能够输出比较好的正弦波。若FW取最小值,则有2n个样点得到平滑的正弦波。

相位调制模块可以设置输出信号的初始相位,对于上变频或下变频模式的信号发生器,初始相位可以为零,相位调制器取累加器的高M位作为波形存储器的查找表地址(M与存储器的大小有关),完成由相位到振幅的转换。波形存储器首先将正弦波一个周期内的数据进行采样、量化、存储和格式转换(.mif文件),然后将产生的.mif文件中的数据存储在ROM中,通过查找表寻址方式完成由相位寻址到波幅的转变,输出信号经过D/A转换,变换为模拟信号,最终经过低通滤波器得到的频率源信号。其中,当步进字FW为常数时,输出频率不变的正弦信号,而当FW变化值,则产生变频信号。

假设DDS输出正弦信号,则:

(u)t=sin2πf0t=sinw(t)

(7)

式(7)中时间t是连续的,采样周期为Tclk,采样频率表示为fclk,并对采样后的数据进行离散化处理,设频率控制字为FW,则连续两次采样的相位差为:

(8)

N表示相位累加器的位宽,则频率控制字与输出频率的关系为:

(9)

fout为DDS的输出频率,由上式可以看出,输出信号的频率主要取决于频率控制字FW。FW为常数时,DDS输出的时具有固定频率的正弦信号;而当FW线性增加时,则输出信号的频率也是线性增加的。此时有:

(10)

f(t)为瞬时频率,γ为常数,正弦信号的相位w(t)是f(t)关于时间t的积分。则输出信号表示为:

(11)

f0为初始频率,则关于相位w(t)的LFM信号表达式为:

s(t)=ejw(t)=cos(w(t))+jsin(w(t))

(12)

2 基于FPGA设计LFM信号发生器

2.1 基于FPGA的LFM信号设计原理

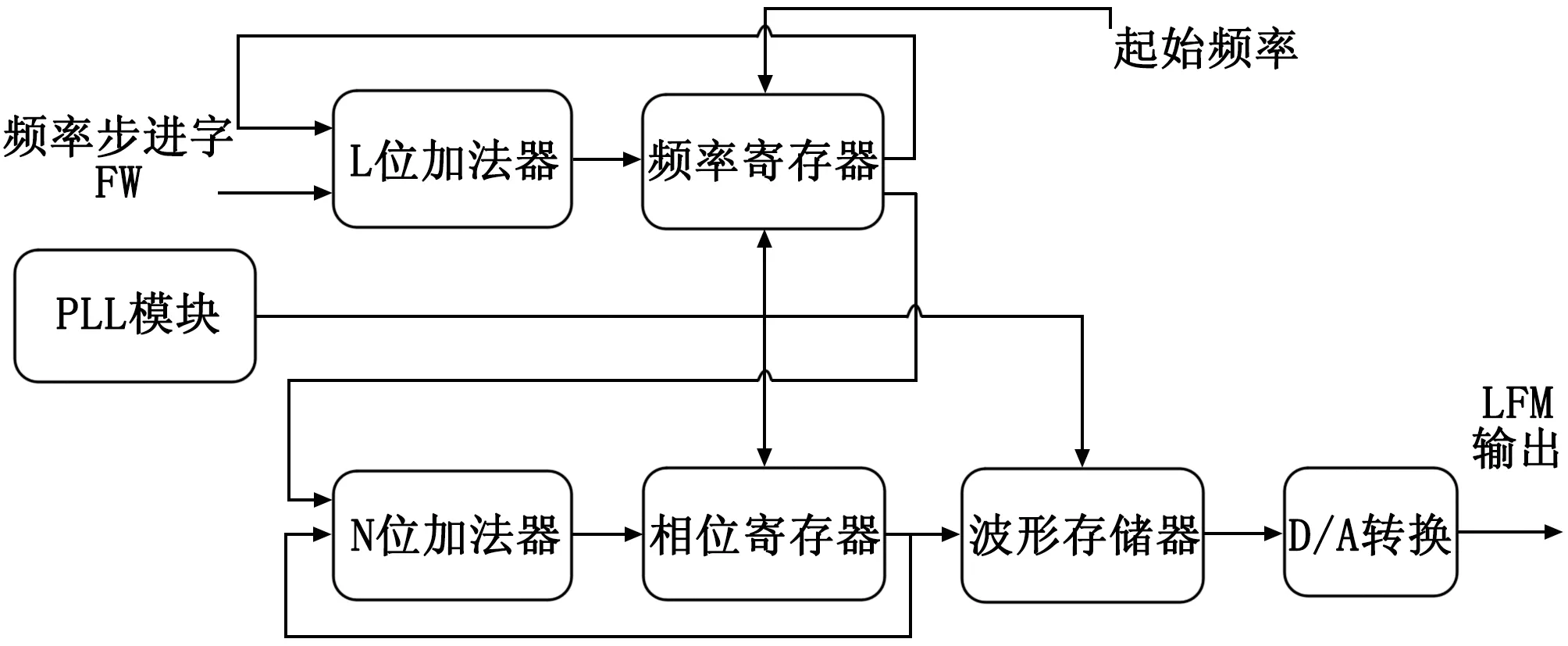

本文选择ALTERA公司的Cyclone II系列的EP2C70F896C6FPGA芯片进行设计实现,该芯片内部未集成具有DDS功能的IP核,但FPGA内嵌丰富的存储器资源,基于查表的快速运算方式,采用FPGA芯片设计并实现DDS功能是完全可行的。基于FPGA产生LFM信号的设计框图如图3所示。

图3 LFM信号发生器设计框图

由上图可以看出,LFM信号发生器包含频率累加器、相位累加器、波形存储器及D/A转换模块,其中位长L、N由LFM脉冲信号的时宽决定。该电路工作过程:频率累加器对步进字求积分,获得线性增加的瞬时频率,并作为相位累加器的一个输入,通过相位累加器完成积分,得到瞬时相位,并取累加器的高M位的值作为波形存储器的寻址(M由ROM波形存储器一个周期的采样多少决定),此过程完成相位到幅值的转换,得到频率线性增加的输出信号。LFM信号分实部和虚部,故需要设计两个信号发生器,如图4所示。

图4 LFM信号设计框图

假设芯片通过PLL模块产生稳定的时钟频率fclk,输出信号的起始频率为f0,步进频率为ft,信号设计参数:带宽为B,时宽为T,则由式(8)、(9)得到频率累加器的初始值fstart和频率步进字FW为:

(13)

(14)

当采用上变频或者下变频设计LFM信号时,输出信号的初始频率、初始相位可以设置为零,即f0=fstart=0。首先将正弦信号和余弦信号一个周期的数据进行采样、量化后存储在波形存储器ROM中,然后根据LFM信号的设计参数,即带宽、时宽,通过式(14)计算频率步进字FW,编写激励文件对设计电路进行初始化,并作为频率累加器的一个固定输入端,每一个有效时钟脉冲到来时,程序控制累加器完成其反馈值与FW完成一次累加求和,得到信号的瞬时频率,且频率值是线性增加的;而相位累加器通过加法器对其反馈值与瞬时频率求和,得到信号的瞬时相位,最后取相位累加器输出相位的高M为作为正弦波和余弦波存储器的寻址,存储器进行查表输出,并经过数模转换电路、低通滤波电路得到平滑的线性调频信号。

2.2 FPGA实现

DDS的核心部分相位累加器设计可以采用两种方法:① 使用VHDL/Verilog程序设计的方法;② 使用参数可设置的LPM兆功能块调用的方式进行设计。为提高设计效率,本文采用调用LPM兆功能块进行设计,并结合MATLAB程序设计产生信号的采样数据,存取到ROM功能块中。系统设计时,稳定可靠的时钟是保证系统可靠工作的重要条件,所以选择时钟也非常重要。在简单电路设计中,采用软件编程的方式产生时钟输入;但是电路设计复杂时,对输入时钟的稳定性要求比较高,此时需要FPGA芯片集成的锁相环(PLL)模块产生稳定的时钟信号。

首先通过MATLAB工具对正弦波、余弦波一个周期的波形进行采样、量化和格式转换(.mif);接着调用FPGA芯片集成的锁相环(PLL)模块,可以通过设置倍频和分频因子改变PLL的输出频率,产生稳定的时钟输入;然后设计电路产生LFM信号的实部和虚部;最后用Modelsim工具对电路输出数据进行模拟仿真,观察LFM信号的数字波形。参数设置如下:

1)对正弦波、余弦波的一个周期进行采样产生的1 024个6位数据分别存储在cos.mif、sin.mif文件中,打开quartus II 仿真软件下的MegaWizard Plug-In Manger,选择ROM:1-PORT,设置输出位宽6 bit、1024word。

2)打开quartus II工具菜单下的MegaWizard Plug-In Manger选项,找到altpLL模块,设置倍频因子为2,分频因子为1,产生100 MHz的输出时钟信号。

3)LFM信号的参数:带宽B=10 MHz,时宽T=2.5 μs,起始频率为零,加法寄存器字长设置为20 bit。根据式(14)计算,得到初始频率字0和频率步进字为419。

LFM信号发生器的实现框图如图5所示。

图5 LFM信号产生器的FPGA设计框图

从图5可以看出,取相位寄存器的高10位作为寻址数据,输出LFM信号实部I和虚部Q的波形。与采用专用DDS芯片相比,节约了成本,简化了电路设计。

3 实验结果与分析

3.1 实验方法

为简化仿真实验过程,提高实验效率,本文采用第三方仿真软件Modelsim 10.1进行仿真实验,相对于Quartus II自带的仿真软件,Modelsim 10.1功能更全面、运算速度更快。

本实验选择ALTERA公司的Cyclone II系列的EP2C70F896C6 FPGA芯片完成LFM信号的FPGA实现,实验平台采用Quartus II 11.0、Modelsim 10.1c和MATLAB三种仿真工具。基于Quartus II采用软件编程方式完成LFM信号的FPGA产生,基于MATLAB工具完成数据的计算、存储、并转换成Quartus II可识别文件(.mif),采用第三方仿真软件Modelsim 10.1完成LFM信号的波形显示与观察。

3.2 实验步骤

1)采用FPGA软件编程方式设计LFM信号发生器。频率累加器和相位累加器都是采用20位字长,计算频率步进字FW=419,初始频率字设置为零,则可以产生带宽为10 MHz的LFM信号。基于Quartus II平台设计出的逻辑电路组成原理图如图6所示。

图6 LFM信号发生器的硬件电路

2)对LFM信号实部和虚部进行采样、量化。电路运行时取adp[19:10]传输给波形存储器的address[9:0],对存储数据进行查表,输出LFM信号的实部d_out1、虚部d_out2分别存储在ROM_cos、ROM_sin中,其存储1024个数据,输出数据字长为6bit。

3)编写Test Bench文件,对电路进行初始化和驱动硬件电路工作。

4)利用信号发生器的Quartus II仿真输出数据,调用Modelsim仿真工具对电路进行功能仿真,观察输出信号的波形。

3.3 实验效果

图7为带宽为10 MHz的LFM信号波形。从图可以看出LFM信号实部和虚部都是线性变化的,而且波形相似,基于FPGA产生的LFM信号波形与图2中MATLAB仿真结果基本吻合。但图2仿真波形中实部与虚部相位相差90度,而图7中基于FPGA产生的LFM信号的实部和虚部波形相位差小于90度,即存在一定的正交误差,这主要是由于ROM存储器输出采用6 bit量化而产生的量化误差造成的,此外FPGA器件的延时也在一定程度上影响了LFM宽带信号的正交度。采用DDS结合数字调制技术可望减小实部与虚部的正交误差。

图7 基于FPGA产生的LFM信号的实部和虚部波形

4 结论

本文研究分析了LFM信号的特性以及产生方法,重点研究了基于ROM查找表的DDS 技术产生法,采用 FPGA 对LFM信号进行了设计与验证。论文采用 QUARTUSII系统提供的 PLL 锁相环 IP 核设计系统时钟,虽然保证了系统的稳定可靠,但带有 PLL IP核的 FPGA 价格明显提高,增加了产品的成本;另一方面,基于ROM查找表的DDS信号产生法虽然电路实现简单,但与基于 CORDIC 算法的DDS产生法相比,占用的 FPGA存储器ROM资源较多;研究结果还表明,单一的DDS合成方式产生的LFM信号实部和虚部波形存在正交度误差,采用DDS结合数字调制技术或数字校正技术可进一步减小实部与虚部的正交误差,获得更加理想的LFM信号。