面向太赫兹辐射计应用的宽带接收机芯片

张 健,吴倩文,孙朋飞

(杭州电子科技大学,浙江 杭州 310018)

0 引言

毫米波及太赫兹频段与红外等光波相比,可以穿透衣物等遮蔽物,对烟雾灰尘具有更好的穿透性,受天气影响小,可全天候工作;相比传统微波频段,具有更高的分辨率,抗干扰能力更强,在站开式检测等安检安防系统领域具有广阔的前景和应用[1-4]。毫米波及太赫兹辐射计具有无辐射、低功耗等特性,符合安检设备无发射、无感知的需求,在安防成像等领域受到越来越多的关注和研究[5-6]。

近年,毫米波太赫兹辐射计国内外陆续有一些报道[7-14],在辐射计的实现方式上,逐渐由波导混合集成方式向单片集成方式演进。文献[7]报道了世界上首款采用标准65 nm CMOS工艺实现的W-band辐射计芯片,芯片内部集成滤波器、单刀双掷开关、低噪声放大器和平方率检波器,文献[9]采用0.13 μm SiGe BiCMOS工艺设计一款Dicke辐射计芯片,并成功应用于室内二维成像样机中。国内对毫米波辐射计研究起步较晚,在毫米波及太赫兹频段核心芯片研发不成熟,核心芯片和器件需要从国外OMMIC和VDI等公司采购,同时在集成方式上也以混合集成为主。文献[9]报道了一款工作在W波段辐射计基于分立器件外部混合集成方式,集成度不高且一致性难以保证;文献[11]报道了一款用于静止轨道探测的V波段辐射计芯片,包含了正交混频和本振倍频部分,关键的低噪声放大器部分需要外部混合集成,增加了辐射计实现的复杂度。考虑到高灵敏度辐射计的需求,本文设计了一款集成低噪声放大器、镜像抑制混频器及本振倍频链的W波段辐射计SOC芯片,流片实现了射频端的电路全单片化,极大降低了辐射计系统的复杂度和成本。

1 电路设计

芯片采用商用0.1 μm栅长的GaAs pHEMT[15]工艺加工。晶体管的ft,fmax分别达到180,300 GHz。

辐射计SOC芯片框图如图1所示,由低噪声放大器、镜像抑制混频器和本振倍频链路组成。镜像抑制混频器包含一对电阻型混频器,晶体管尺寸为2 μm×30 μm。本振信号经过Lange耦合器之后,分成正交两路加载在晶体管的栅极上,射频信号和中频信号加载在晶体管的漏极。

图1 辐射计SOC芯片框图

电阻型混频器的原理如下:场效应管的沟道电阻在非常低的源漏电压下,可以近似为一个线性电阻[16-17]。这个线性的沟道电阻使用加在栅上的本振信号调制,当栅压低于阈值电压时,沟道近似为开路;当栅压接近最大值时,沟道电阻降低到几欧姆。在小信号驱动的状态时,施加在晶体管栅极上的本振电压改变了耗尽层的厚度,因此沟道电阻和本振电压线性相关。

本振功率加在栅上,通常需要加一个直流栅压,射频和中频信号加在漏端,在射频和中频之间也需要设计相应的滤波器来隔离射频和中频信号。因为源漏之间是无直流偏置电压的,栅漏电容Cgd要比传统的应用(如放大器)大,本振信号会泄漏到漏端,所以在漏端需要滤波器来抑制本振信号的泄漏。

混频器的Ku波段本振信号通过一个6倍频器馈入到混频器的栅极,为混频器提供足够的驱动,同时降低外部本振信号频率要求。6倍频器由一个2倍频器和3倍频器级联而成,避免了直接6倍频损耗过大的问题,同时在末级级联一个驱动放大器,使得倍频输出功率足够大,保证混频器有较低的变频损耗。射频放大部分由一个低噪声放大器实现,考虑到工作频率接近晶体管的截至频率,因此采用了4级级联的结构,提供大约20 dB的增益。

2 电路性能

2.1 6倍频器

为了精确地评估6倍频器的性能,加工了一款独立的6倍频器电路,芯片照片如图2所示,芯片尺寸1.0 mm×1.5 mm。

图2 6倍频器芯片照片

图3为6次谐波分量的输出功率。结果显示,射频输入频率为14.20~18.33 GHz时,对应的射频输出频率为85~110 GHz,带宽为25.6%,功率在8~10 dBm之间,完全可以满足后级基波混频器的本振功率大于7 dBm的功率需求。在目前已报道的倍频器芯片中,在输出功率和带宽方面表现优异。

图3 6倍频器输出功率与输入频率关系(Pin=6 dBm)

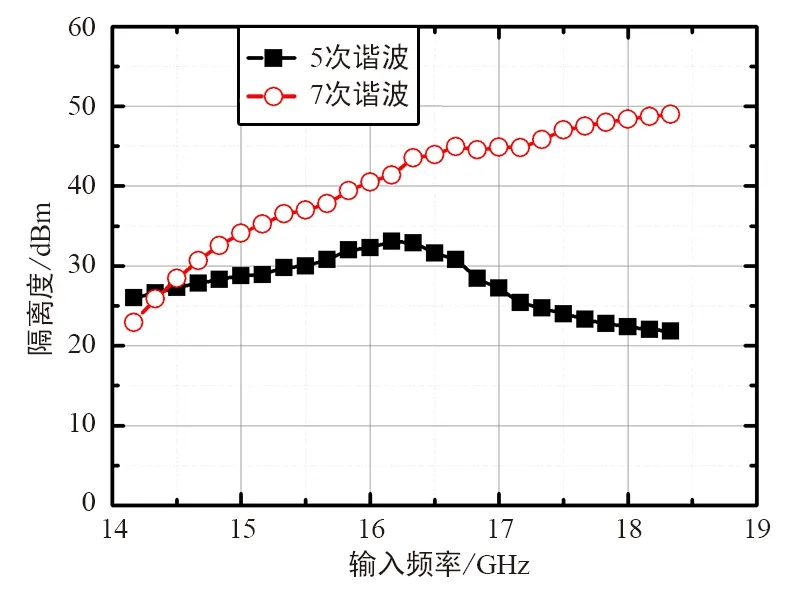

图4为电路的输出频率6次谐波对各次谐波分量的抑制特性,测试结果显示,电路的谐波抑制度优于20 dBc,输出频谱较纯净,能有效抑制后级混频电路的中频输出杂散。

图5为倍频器的功率特性曲线,电路的饱和输出功率接近10 dBm。输入功率为6 dBm时,射频输出功率约为8.5 dBm,与图3的测试数据一致。

图4 5次及7次谐波抑制与输入频率关系

图5 6次谐波分量与输入功率关系(@16 GHz/6 dBm)

2.2 低噪声放大器

图6为低噪声放大器的芯片照片。电路的测量结果如图7所示。

图6 低噪声放大器照片

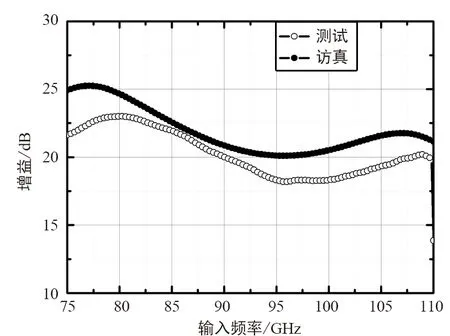

图7为低噪声放大器的增益仿真和测试结果的对比,小信号放大增益测试结果和仿真结果吻合较好,在整个W-band增益大于18 dB。

图7 低噪声放大器增益仿真与测试结果对比

2.3 辐射计电路

图8为辐射计芯片的照片。芯片尺寸为2 mm×2 mm,供电引脚比较多,为便于测试及使用,对辐射计电路进行了封装测试。

图8 辐射计芯片照片

辐射计芯片封装装盒的照片,封装模块各个端口标识如图9所示。整个模块尺寸为73 mm×26 mm×9 mm。考虑到模块的小型化,芯片的本振输入端、中频输出端,均采用小尺寸的SMP接头。

图9 辐射计芯片封装模块效果图

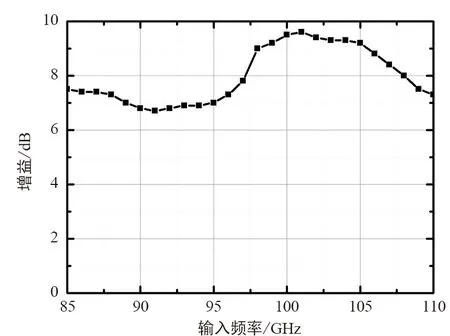

图10为2路中频正交合成后总的增益曲线,2路中频信号通过SMP外接Lange耦合器实现正交合成。在85~110 GHz频带范围内,模块的整体增益大于7 dB,在98~105 GHz范围内,增益大于9 dB,平坦度小于±0.5 dB。

图10 辐射计模块增益曲线(@IF=5 GHz)

通过图11可以看出,辐射计的镜像抑制度大于35 dBc,有效抑制了镜像信号对系统的干扰。

图11 辐射计模块镜像抑制度曲线

本文设计的W-band辐射计与其他报道的辐射计对比如表1所示,工作频率为85~110 GHz,有效带宽25 GHz,尺寸与硅基工艺一个量级,远小于混合集成方式。

表1 W-band辐射计比较

参考文献频率/GHz带宽/GHz工艺LNA增益/dB面积/mm2文献[7]81^931265 nm CMOS270.41文献[8]80^921265 nm CMOS153.00文献[9]80^100200.13 μm SiGe353.42文献[14]90^10010混合集成21N/A本文85^110250.1 μm GaAs184.00

3 结束语

设计了一款工作在W波段的辐射计SOC芯片,经查阅文献,这是目前国内公开报道的第一款100 GHz辐射计SOC芯片。相比于国内目前主流的采购国外芯片或者二极管混合集成的方法,本文的单片SOC电路在体积、集成度以及一致性等方面有明显优势,对国内毫米波太赫兹频段单片集成电路发展有很好的推动作用。