多功能直接数字频率合成器设计

马子轩

摘 要:本文使用QuartusII9软件对SmartSOPC试验箱中的FPGA进行编程,使FPGA实现直接数字频率合成器(DDS)的核心功能。DDS的核心器件包括分频器、频率调节预置电路、累加器、波形储存器等模块。在后期的扩展功能设计中加入了开关按键、LED数码管、测频电路、显示控制电路、波形选择电路等模块,实现了输出频率与相位可控和可视化、输出多种波形、频率可测等功能的多功能直接数字频率合成器。

关键词:直接频率合成器 FPGA

中图分类号:TN 74 文献标识码:A 文章编号:1674-098X(2019)05(b)-0006-02

1 设计原理

1.1 DDS系统组成

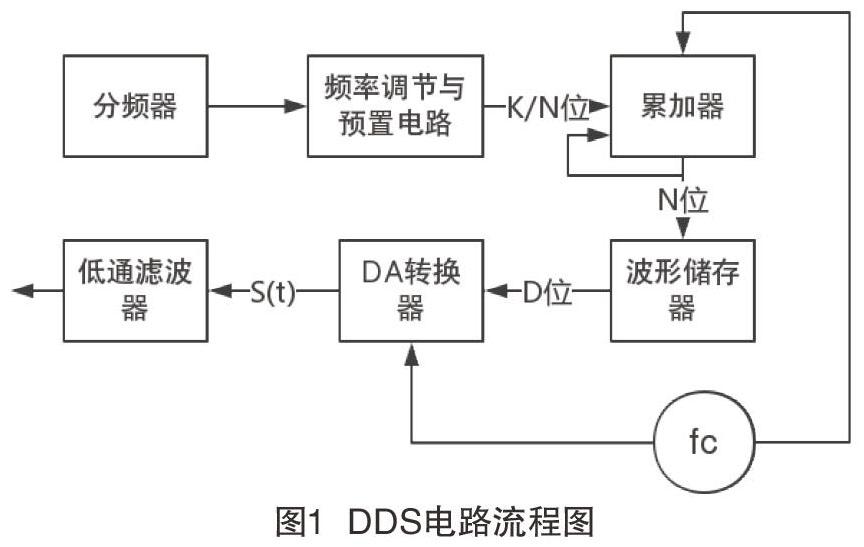

DDS系统核心由分频器、频率调节与预置电路、累加器、波形存储器构成。频率预置电路负责调节频率设定位(K)和相位设定位(P),其中K即为读取ROM表时的步长,P即为读取ROM表时的开始位置。由此可得其输出的频率为Kfc/N,其中fc为DA转换器的采样频率,N为ROM表的长度。根据奈奎斯特采样定理可知,K最大为N/2。

累加器由n位加法器+n位寄存器组成,负责在激励信号的作用下,累加相位,然后将相位信息输出到波形储存器中读出波形幅值信息,将幅值信息输送到DA转换器中,经过低通滤波器后得到输出波形。

1.2 DDS的电路组成

整体的DDS电路由四大部分组成,图1所示的低通滤波器和DA转换器由SmartSOPC试验箱提供。分频器电路对开发板提供的稳定48MHz信号进行了分频,以提供给各个电路模块使用,如表1所示。

频率预置电路用于调节K和P,其中K和P的调节范围均设置为1~1024,我们提供了两种调节速率(快调和慢调),分别使用2Hz和10Hz的调节脉冲信号作为激励。

累加器由三片7483四位加法器实现,将加法计算出的结果输送给D触发器寄存,等待下一个上升沿到来后将这个数发送到加法器的输入端,实现累加。这里接入的是1MHz的脉冲信号,这个脉冲的频率需要和ROM的读取频率相同。

波形储存器为12位寻址,相当于将一个周期的正弦信号离散成样值序列,将每个样值对应的幅值以10位二进制输入到ROM中。在ROM的输入端加入使能引脚,命令电路只读取已经使能的ROM,这样可以节省电路的性能损耗,同时也给波形选择带来了极大的方便。

为防止用户在操作时的抖动,加入除颤电路。利用一个集成的D触发器进行除颤,除颤电路的频率是10Hz。

2 附加功能

在设计完基础的DDS功能之后,为了实现与客户的友好交互,继续设计了波形选择,测频等。

2.1 波形选择

DDS需要输出多种波形,需要通设计一个ROM选择电路来实现不同波形的切换。

波形选择模块主要由74160模十计数器、74138译码器、两个8选1的总线选择器构成。74160用来计数从而选择波形;74138将计数的结果译码,来选择哪个ROM被读取;8选1总线选择器用来将从ROM中读取的数据选择出来,送到DA转换器转换。

2.2 测频功能

此功能用于测量此时输出的波形的频率,并将其输出在数码管上。其基本原理是讀取ROM中的数据的峰值出现的时刻,当峰值出现时计数器就+1,在T=1s的范围内,计数器的值即为输出信号的频率。

3 仿真

下面罗列出各个模块的仿真情况。其中分频电路和波形存储电路因仿真时间较长,在这里不提供仿真结果。

4 示波器测试结果

由于测试结果较多,在这里仅提供两种示波器的结果。一种是基本的三角函数信号,一种是经过设计的一箭穿心图样,如图4、5所示。

参考文献

[1] 王静.基于FPGA直接数字频率合成器DDS的设计[J].科技信息,2012(23):113-114.

[2] 蒋立平,姜萍,谭雪琴,等.数字逻辑电路与系统设计[M].北京:电子工业出版社,2013.

[3] 郑燕,郝建国,党剑华.基于VHDL语言与Quartus II软件的可编程逻辑器件应用与开发[M].北京:国防工业出版社,2007.

[4] 杨东霞,巨永锋.基于FPGA和DDS的数字调制信号发生器设计与实现[J].电子设计工程,2013,21(6):90-93.