高速小回滞双向SCR的ESD防护器件设计

顾晓峰 彭宏伟 梁海莲 董树荣 刘湖云

摘 要:針对可控硅(SCR)结构的静电放电(ESD)防护器件触发电压高、电压回滞幅度大以及开启速度慢等问题,设计了一种RC触发内嵌PMOS DDSCR (DUT3)器件. 基于0.35 μm Bipolar-CMOS-DMOS工艺制备了传统DDSCR (DUT1)、内嵌PMOS DDSCR (DUT2)和DUT3三种器件,利用传输线脉冲系统测试了它们的ESD特性.实验结果表明:与DUT1相比,DUT2触发电压从31.3 V下降至5.46 V,维持电压从3.59 V上升至4.65 V,具有窄小的电压回滞幅度.但是,由于DUT2内嵌PMOS常处于开态,导致DUT2器件漏电流高达10-2 A量级,不适用于ESD防护.通过在DUT2内嵌的PMOS栅上引入RC触发电路,提供固定栅压,获得的DUT3不仅进一步减小了电压回滞幅度,同时具有12.6 ns极短的器件开启时间,与DUT1相比,DUT3开启速度提高了约71.5%,漏电流稳定在10-10 A量级.优化的DUT3器件适用于高速小回滞窄ESD设计窗口低压集成电路的ESD防护.

关键词:静电放电;双向可控硅;触发电压;开启速度;漏电流

中图分类号:TN342 文献标志码:A

Design of ESD Protection Device for High Speed

and Very Small Snapback DDSCR

GU Xiaofeng1,PENG Hongwei1,LIANG Hailian?覮,DONG Shurong2,LIU Huyun1

(1. Engineering Research Center of IoT Technology Applications (Ministry of Education),

Department of Electronic Engineering,Jiangnan University,Wuxi 214122,China;

2. Institute of Microelectronics and Optoelectronics,Zhejiang University,Hangzhou 310027,China)

Abstract:In order to solve the problems such as large trigger voltage, large voltage snapback margin and slow turn-on speed of Electrostatic Discharge(ESD) protection devices based on the Silicon Controlled Rectifier(SCR) structure, a dual-directional SCR(DDSCR) device embedded with PMOS and triggered by the RC circuit(DUT3) was designed. Three types of devices including the conventional DDSCR(DUT1),DDSCR embedded with PMOS (DUT2) and DUT3 were fabricated in a 0.35 μm Bipolar-CMOS-DMOS process. Their ESD characteristics were measured by the transmission line pulse system. The test results show that, compared with DUT1, the DUT2 trigger voltage decreases from 31.3 V to 5.46 V, the holding voltage increases from 3.59 V to 4.65 V,and the voltage snapback margin of DUT3 is very small, but the high leakage current up to 10-2 A makes it unsuitable for ESD protection. By introducing an RC circuit to provide a fixed gate voltage for the embedded PMOS in the DUT2, the modified DUT3 shows not only a further reduced voltage snapback margin but also a shorter response time of only 12.6 ns. Compared with DUT1, the turn-on speed of DUT3 increases by about 71.5%, and the leakage current can be stabilized at the order of 10-10 A. This optimized DUT3 is suitable for ESD protection in the low-voltage integrated circuits with requirements of high-speed, small snapback margin and narrow ESD design windows.

Key words:Electrostatic Discharge(ESD);dual-directional silicon controlled rectifier;trigger voltage;turn-on speed;leakage current

在集成电路(IC)静电放电(ESD)防护中,可控硅(SCR)因具有单位面积ESD鲁棒性强、导通电阻小等优势而备受关注[1-2].但是,SCR器件在ESD应力作用下存在电压深回滞、易闩锁等缺点[3-5],使其在实际应用中受到很大限制.针对SCR结构的电学特性及被保护电路的ESD防护需求,国内外研究人员在提高单向SCR、双向SCR (DDSCR)及相关改进型器件的ESD防护性能方面已取得了一定的进展与突破[6-11]. Dong等[6]通过在N型改进型SCR结构中引入齐纳二极管,降低了器件的触发电压.然而,针对中高压IC的ESD防护小回滞窗口需求,该方法还需进一步增大SCR维持电压.Huang[7]等通过在SCR中内嵌三极管或Dong[8]等增加浮空Nwell区

域,提高了器件的维持电压.Wang[9]等引用MOS辅助触发SCR,或通过在SCR中内嵌PMOS等设计方法[10],减小了器件的电压回滞幅度,但都难以满足ESD强鲁棒性需求.Chen[11]等通过在漏极端嵌入N+注入区的设计方法,增强了ESD鲁棒性,但器件响应速度较慢,易因防护器件不能及时开启而导致内部被保护电路产生栅氧击穿或功能故障.因此,设计具有低触发电压、高维持电压、强ESD鲁棒性以及高开启速度的ESD防护器件,已成为IC片上ESD防护的主要研究方向.

本文基于0.35 μm Bipolar-CMOS-DMOS (BCD)工艺,在传统DDSCR (DUT1)的基础上,设计并制备了内嵌PMOS DDSCR (DUT2)和RC触发内嵌PMOS DDSCR (DUT3)等器件. 通过传输线脉冲(TLP)测试,研究并分析了新型ESD防护器件的工作特性及电学机理,相关的器件结构设计及优化方法可为低压IC的ESD防护器件设计提供有益的参考.

1 器件結构设计

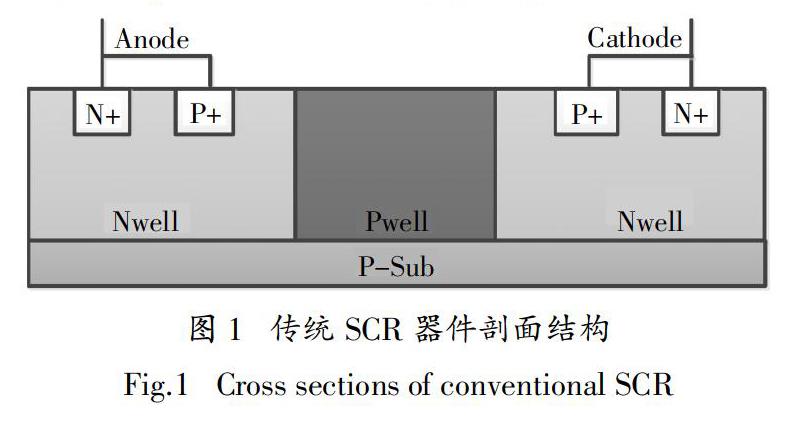

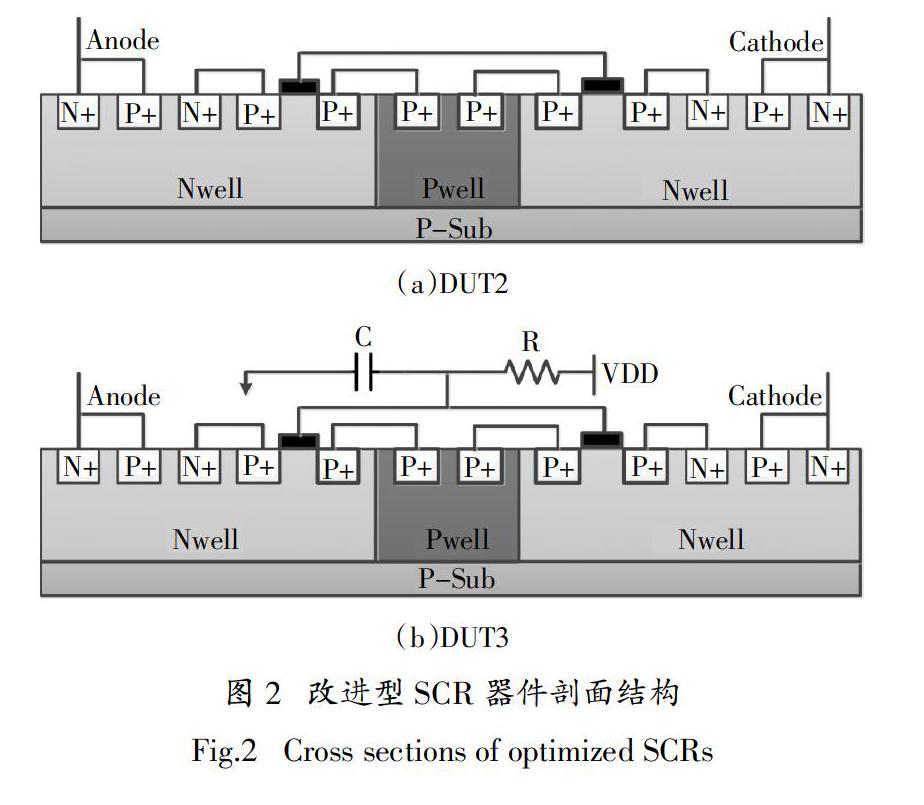

DUT1器件的剖面结构如图1所示.为降低器件的触发电压,在两侧Nwell中各内嵌一个PMOS,上述两PMOS通过在Pwell中引入的两个高掺杂P+相连接,可优化得到DUT2,其剖面结构如图2(a)所示.

由于DUT2中PMOS的栅压电压具有一定的不确定性,器件可能存在大漏电流问题.因此,根据被保护电路的工作频率,设计了一个合适的RC辅助触发电路,确保PMOS具有一定的栅阈值电压,使器件能正常开启,由此获得改进的DUT3,其剖面结构如图2(b)所示.

与DUT1相比,DUT2中引入的PMOS结构不仅有助于降低器件的触发电压,还因其具有电压无回滞特点,有助于提高维持电压.然而,DUT2的内嵌PMOS栅压可能会随ESD脉冲大小发生变化,导致PMOS开启状态不稳定,产生较大的漏电流. 与DUT2相比,DUT3的内嵌PMOS栅压则由外部引入的RC辅助触发电路控制,栅压固定,能使器件处于关断状态,可避免漏电流增大. 上述器件在ESD脉冲触发开启后,内部均主要呈现SCR泄流路径,导通电阻均较小,具有较强的ESD鲁棒性.

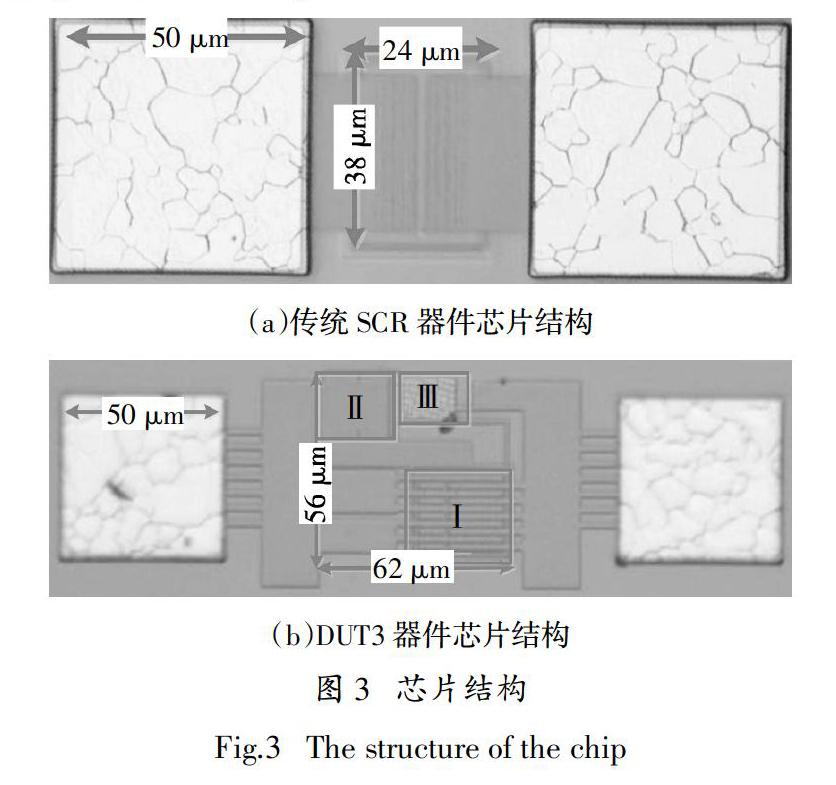

上述实验流片版图如图3所示,图中金属电极焊盘面积均为50 μm × 50 μm. 除金属电极焊盘外,图3(a)中传统SCR器件面积约为宽 × 长 = 38 μm × 24 μm = 912 μm2. DUT3的器件流片版图如图3(b)所示.区域Ⅰ为除RC外器件部分,区域Ⅱ为电容,区域Ⅲ为电阻. DUT3面积约为宽×长=56 μm × 62 μm = 3 472 μm2. 区域Ⅰ面积约为宽×长=36 μm × 31 μm =1 116 μm2.与DUT2相比,除RC触发电路外,其他器件面积均相同.DUT2与DUT3相同部分的器件面积约为1 116 μm2.

2 器件ESD工作特性及电学测试

基于0.35 μm BCD工艺制备了前述3种实验器件,利用Barth 4002型TLP测试系统获得其特性曲线,如图4所示. 同一器件在瞬态ESD应力作用下的电流-电压(I-V)和直流偏置下的电流-漏电流(I-IL)关系分别用相同形状的实心和空心符号曲线分别表示.

由图4可知,器件的触发电压随着结构的改进与优化,呈下降趋势,这是由于引入PMOS结构均能有效地降低触发电压(Vt1).并且,与DUT1相比,DUT2和DUT3电压回滞幅度大幅缩小,但DUT2的漏电流较大.与DUT2相比,DUT3中的RC触发电路有效地钳制了内嵌PMOS的栅压,避免了器件

漏电流增大的现象,使漏电流从10-2 A量级降至

10-10 A量级.

在TLP应力作用下器件的主要特性参数如表1所示.与DUT1相比,DUT2和DUT3的维持电压(Vh)较大,这是由于PMOS管的无回滞电压输出特性作用. 在器件导通之后,上述实验器件的二次失效电流(It2)均大于4.5 A,呈现出较强的ESD鲁棒性,测试结果与前文对不同结构的工作原理分析相吻合.结合器件的ESD性能参数和所消耗芯片面积,衡量ESD防护器件的效能比,该效能比通常称为品质因子(FOM),定义如下:

式中:S为器件面积,除去漏电流较大的DUT2以外,由计算可知,DUT1和DUT3品质因子分别为0.59和1.03. 因此,DUT3仍具有较高的ESD防护效能.同时,与最近国际期刊报道的PMOS辅助触发SCR(SSSCR)[10]器件相比,DUT3的Vt1较小,且电压回滞幅度较窄,更适用于低压ESD防护设计窗口.

为进一步研究器件的ESD防护性能,对DUT2和DUT3进行了正反向TLP测试,结果如图5所示.由于DUT3比DUT2多一RC辅助触发电路,在正向ESD脉冲测试中,DUT3因RC辅助触发作用,器件低压触发,且ESD鲁棒性较强.DUT2中的浮空PMOS产生的漏电流,辅助触发SCR,导致DUT2呈现出与DUT3相似的正向ESD特性.在反向ESD脉冲测试中,DUT2因器件结构完全对称,其反向ESD特性与正向脉冲测试的ESD特性相同.然而,因RC触发电路未起作用,DUT3中内嵌PMOS的栅压处于高电位,此时PMOS处于关断状态,器件内部在导通状态下呈现为较大阱电阻性质,ESD鲁棒性较弱.由测试可知,反向ESD应力作用下DUT3的It2约为

1.83 A,根据Barth 4002 TLP测试系统特征,在人体模型(HBM)下,该器件可承受的ESD电压鲁棒性可折算为:It2 × 1 500 V.由此可得,DUT3器件的反向ESD电压鲁棒性可近似等于2 745 V.与当前电子产品行业普遍认可的HBM模型2 000 V的ESD防护等级相比,DUT3器件仍可满足反向ESD应力下的ESD防护需求.

3 器件开启速度测试分析

当上升沿为10 ns,周期为100 ns的ESD脉冲信号作用于器件时,器件端电压随时间变化的关系曲线如图6所示.电压从0快速上升至一峰值(Vos),随后减小并降至一相对稳定的电压值(Vave).将电压随时间变化并下降至Vos的90%时刻,记为器件触发开启过程起点;将器件电压下降至Vave的110%时刻,记为器件触发开启过程终点;将上述起点与终点之间的时间间隔,定义为器件触发开启的响应时间(Ton). Ton越长,器件的开启速度越慢.

根据上述定义,实验器件触发开启的响应区域如图6中的虚线框所示.将DUT2和DUT3响应区域放大,如图6中右上方内插图所示.可以发现,与DUT1相比,DUT2和DUT3的Ton明显较短,器件开启速度快.从图6中提取的关键开启特性参数列于表2.与DUT1相比,由于DUT2和DUT3中內嵌PMOS结构的辅助触发,Ton分别大幅缩小至13.4 ns和12.6 ns.与DUT1相比,DUT3的开启速度提高了约71.5%.此外,虽然DUT3与SSSCR的Ton相接近,但是,DUT3的过击穿电压较低,且导通电阻较小,因此具有更好的ESD防护功能.

4 结 论

通过引入PMOS结构,改进型DDSCR器件的电压回滞幅度得以大幅缩小. 但器件DUT2中PMOS栅电位不稳定,存在大漏电流问题. 通过引入RC外部辅助电路钳制PMOS的栅压,器件漏电流可稳定在10-10 A量级. 此外,器件的开启特性证明:PMOS可有效降低器件的Ton. 与DUT1相比,DUT3开启速度提高了约71.5%.对于较低Vt1和较小电压回滞幅度的DUT3器件,倘若根据纳米工艺的制备特征,调节器件中的相关特征尺寸参数,或进一步优化部分结构,使其具有更优良的开关特性,本实验方案也可以为纳米工艺条件下电路的ESD防护设计提供参考.

参考文献

[1] CHEN J T,LIN C Y,KER M D. On-chip ESD protection device for high-speed I/O applications in CMOS technology[J]. IEEE Transactions on Electron Devices,2017,64(10):3979—3985.

[2] 陈迪平,刘杏,何龙,等.一种片上低触发电压高耐压NMOS ESD防护结构设计[J]. 湖南大学学报(自然科学版),2016,43(2):115—118.

CHEN D P,LIU X,HE L,et al. An on-chip NMOS ESD protection circuit with low trigger voltage and high ESD robustness [J]. Journal of Hunan University (Natural Sciences),2016,43(2):115—118. (In Chinese)

[3] LIANG H L,GU X F,DONG S R,et al. RC-embedded LDMOS-SCR with high holding current for high-voltage I/O ESD protection[J]. IEEE Transactions on Device and Materials Reliability,2015,15(4):495—499.

[4] HUANG X Z,LIOU J J,LIU Z W,et al. A new high holding voltage dual-direction SCR with optimized segmented topology[J]. IEEE Electron Device Letters,2016,37(10):1311—1313.

[5] 黄龙,梁海莲,顾晓峰,等. 多晶硅栅对LDMOS-SCR器件ESD防护性能的影响[J]. 浙江大学学报(工学版),2015,49(2):366—370.

HUANG L,LIANG H L,GU X F,et al. Effect of poly-silicon gate on ESD protection performance of LDMOS-SCR devices [J]. Journal of Zhejiang University (Engineering Science),2015,49(2):366—370. (In Chinese)

[6] DONG S R,ZHONG L,ZENG J,et al. Stacked zener trigger SCR for HV IC ESD protection[J]. Microelectronics Reliability,2014,54(6/7):1160—1162.

[7] HUANG X Z,LIU Z W,LIU F,et al. High holding voltage SCR with shunt-transistors to avoid the latch-up effect[C]// Nanoelectronics Conference. Chengdu:IEEE,2016:1—2.

[8] DONG S R,WU J,MIAO M,et al. High-holding-voltage silicon-controlled rectifier for ESD applications[J]. IEEE Electron Device Letters,2012,33(10):1345—1347.

[9] WANG Y,JIN X L,LIU Y,et al. Robust dual-direction SCR with low trigger voltage,tunable holding voltage for high-voltage ESD protection [J]. Microelectronics Reliability,2015,55(3/4):520—526.

[10] WANG W H,JIN H,GUO W,et al. Very small snapback silicon-controlled rectifier for electrostatic discharge protection in 28 nm processing [J]. Microelectronics Reliability,2016,61(6):106—110.

[11] CHEN S L,YANG C H,YEN C Y,et al. Novel parasitic-SCR impacts on ESD robustness in the 60 V power pLDMOS devices[C]//IEEE International Conference on Consumer Electronics. Taiwan:IEEE,2017:381—382.