基于BSC9132芯片的DSP设计方法研究马田香

黄承波

摘 要:文章提出了一种基于BSC9132芯片的DSP软件设计方法,在芯片的DSP核心SC3850上进行软件开发设计,针对核间交互、算法优化等方面给出详细介绍,为在此平台上进行DSP软件开发提供参考。

关键词:BSC9132芯片;SC3850;异步交互

1 BSC9132芯片研发背景

BSC9132芯片是Freescale公司专为Small Cell定制的芯片,为高性能、低功耗、高密度的集成器件,可用于实现无线收发传输信号的基带处理,现阶段主要用于微基站解决方案。在BSC9132芯片上开发软件前,首先,需对该芯片的架构,各个核心的资源、处理性能等方面进行研究,同时,作为基带芯片,需充分研究其对射频、时序等的控制,为实现系统设计提供支持。

2 BSC9132芯片介绍

BSC9132芯片集成4个核心,两个SC3850的DSP核心,两个e500的CPU核心。另外,协处理器MAPLE集成LTE物理层上下行处理单元,实时性好,功能强大。协处理器版本为MAPLE-B2P,是Multi-Accelerator Platform Engine Baseband 2 for Pico的缩写,其是专门为Pico Cell基带设计的多加速平台引擎,可以实现信道编码/译码、傅里叶变换、通用移动通信系统(Universal Mobile Telecommunications System,UMTS)码片速率处理、通用移动通信技术的长期演进(Long Term Evolution,LTE)上行信道处理、循环冗余校核(Cyclic Redundancy Check,CRC)检测等,由卷积、滤波、Turbo编码、Viterbi译码、码片速率处理和MIMO各模块处理器组成。

BSC9132芯片的射频相关接口可分为两大类:串口、并口。串口主要为通用公共无线电接口(Common Public Radio Interface,CPRI),可实现将基带处理单元基带处理单元(Building Base band Unit,BBU)与射频处理单元射频拉远单元(Remote Radio Unit,RRU)的通信。并口主要为模拟接口电路(Analog Interface Circuit,AIC)射频接口,可以和ADI AD9631无缝连接,并且可以直接通过直接存贮器访问(Direct Memory Access,DMA)访问MAPLE-B2P协处理器。在此仅简要介绍CPRI的使用。

BSC9132芯片支持CPRI V4.0版本协议,Cpri基本帧长:1 chip=1/3.84 MHz= 260.416 667 ns。一个基本帧包含16个字:W=0∶15,字長T依赖于比特率,BSC9132芯片支持的CPRI线速较好。

3 DSP多核使用

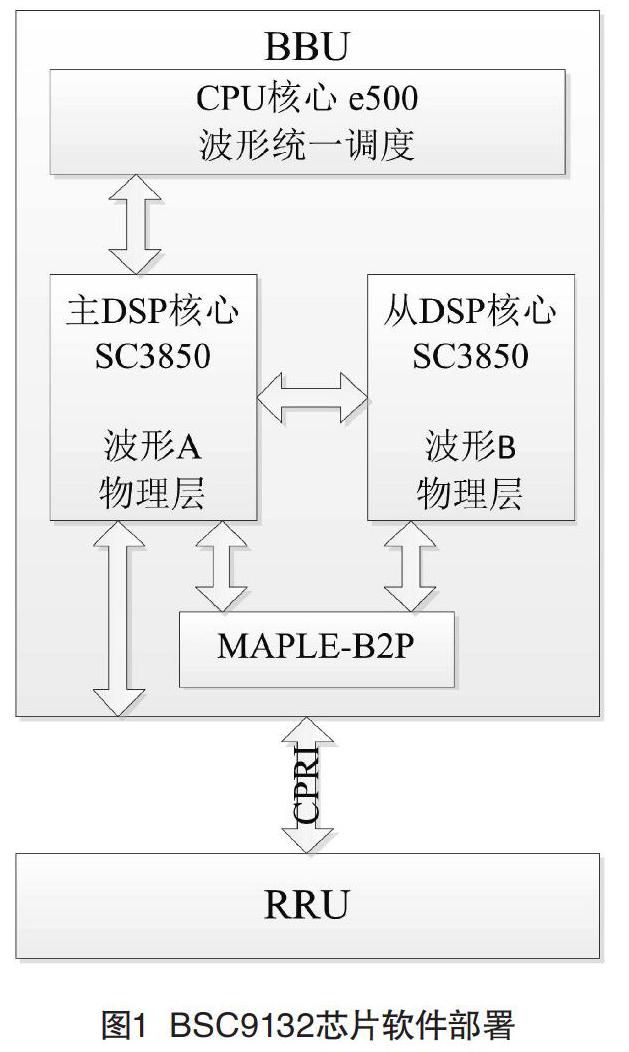

BSC9132芯片集成了两个SC3850的DSP核心,两个核心间一般作为同步模式使用,但针对特殊波形的处理,可考虑将两个核心作为异步使用,同时,进行两个通信波形物理层的开发设计,而两个波形的接入控制等在CPU核心中进行统一调度,由此BSC9132芯片上的软件部署如图1所示。

BSC9132芯片是针对微基站设计的,其协处理器是针对公网协议进行的匹配,若想在此芯片上实现特殊波形(协议自定)的开发设计,需对芯片进行更深一步的了解,可使用协处理器中的通用部分,如傅里叶变换、Turbo编解码等。另外,对于通信波形的物理层处理,尤其是算法模块部分,需在DSP核心上进行处理,由此DSP核心的运算能力就显得尤为重要,在进行芯片选择时一定要针对波形的运算量及芯片的能力来综合决定。

3.1 核间交互

BSC9132芯片CPU核心与DSP核心之间的交互可采用逐级交互机制,即CPU核心与主DSP核心交互,主DSP核心与从DSP核心交互,交互方式可分为两类:一类是共享内存加中断触发的方式,另一类是使用IPC接口的方式。共享内存分为上下行信令交互区和数据交互区,交互区可定义在共享内存M3或外部存储空间双倍速率(Double Data Rate,DDR)上,并且可通过DMA来进行数据存取,中断触发用于通知核心进行信令解析及数据使用。IPC接口由两个交互的核心共同维护,底层触发方式有两种,一是中断,二是轮询。波形开发时可根据具体的需求来选择合适的核间交互方式。

在开发波形时,需根据波形的协议及功能模块的部署来决定交互方式。波形的协议及功能模块的部署决定了核间交互的数据量及交互频率,开发波形前需进行详细验证,以确保能够满足开发需求。

3.2 DSP核开发

SC3850 DSP核心开发环境使用CodeWarrior IDE v10.7.2,开发时对存储空间的规划在链接器命令文件(Linker Command File,LCF)中,文件后缀为l3k。值得注意的是LCF文件中可对共享内存M3和外部存储空间双倍速率内存定义为两种类型,一种是私有类型,使用关键字private限定;另一种是共享类型,使用关键字shared限定。通过简单的运算测试发现,数据存储在片上M2,私有M3,储存在私有DDR内存上时,运算速度相当。数据存储在共享M3上的运行速度快于数据存储在共享DDR上,但都比片上M2上慢[1]。

波形开发时,使用两个核心为异步工作模式,则不同的核需定义不同的变量和函数,但在初始化时需使用相同的变量名和函数名。若各个核心的处理不同,需放置在私有空间,两个核心都为其开辟空间,此时需编译的变量或函数虚拟地址相同,否则编译会提示错误。各个核心单独使用的变量和函数需在LCF中进行特殊限定。

基带模块与射频模块交互使用CPRI协议,此种交互的优点是交互统一,可将BBU与RRU模块分离,缺点是波形开发灵活性差、控制时序严格。CPRI使用的难点在于收发双方时钟的对齐。

3.3 算法实现优化

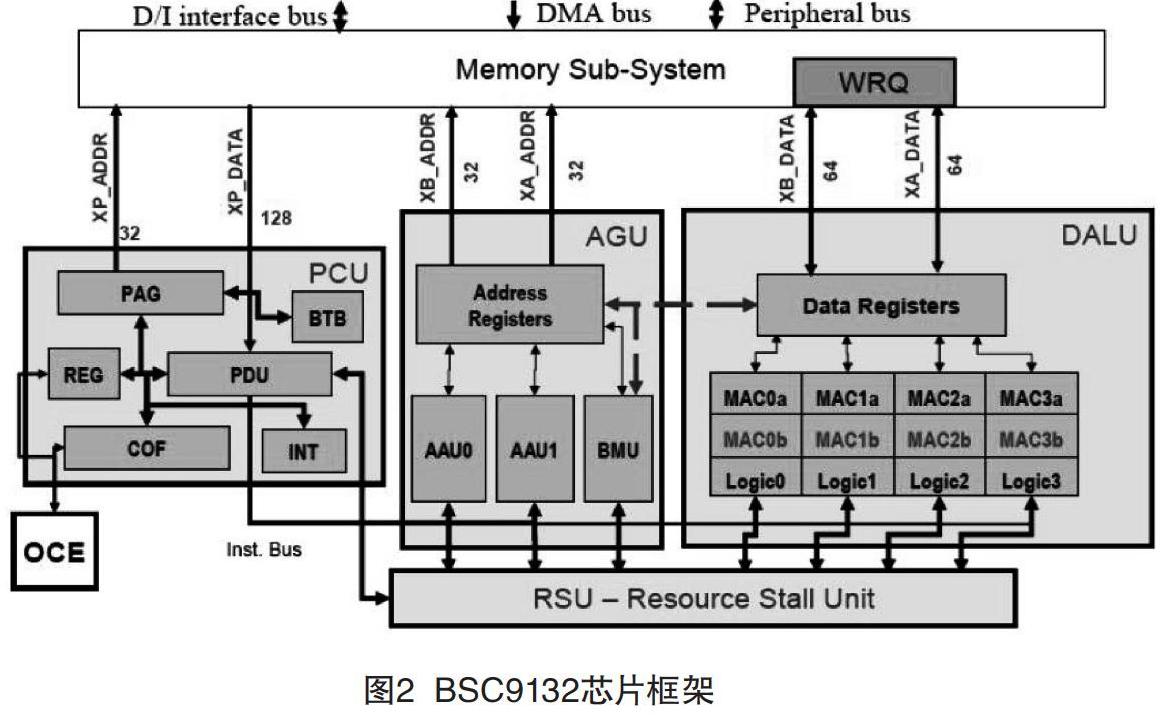

BSC9132芯片上有两个DSP核心SC3850,SC3850有4种单元,数据算术逻辑单元(Data Arithmetic and Logic Unit,DALU),地址产成单元(Address Generation Unit,AGU),程序控制单元(Program Control Unit,PCU),资源暂停单元(Resource Stall Unit,RSU)。DALU包括4个并行的算术逻辑单元(Arithmetic Logic Units,ALU),在此单元上处理算术及逻辑运算,每个ALU的每cycle可执行2个16 bit数据的乘累加操作;有两个64 bit的数据总线。AGU包括2个地址算术单元(Address Arithmetic Units,AAU),可进行有效的地址计算[2]。

从图2中可以看出当同时使用2AGU+4DALU时,可以达到芯片所能处理的最大能力。若想同时使用4个DALU,则数据取用时需按64 bit进行,即数据存储的首地址按8 Byte对齐。

在波形实现过程中,一般需进行数据接收与已知序列的相关运算,接收数据存储格式为16 bit实部、16 bit虚部,由此在运算时无法同步使用2AGU+4DALU,从而无法发挥芯片最大的运算能力,在进行波形开发时需根据数據的特点及芯片的能力将波形功能模块进行优化,从而满足使用需求。

4 结语

Freescale公司的BSC9132芯片主要应用于微型基站,本文简要介绍芯片组成,并从DSP核心SC3850出发,讨论核间交互方法、SC3850核心的开发使用、编程性能优化等,为在此芯片上开发特殊波形提供DSP方面的参考。

[参考文献]

[1]赵景涛,朱宇霞.基于BSC9132的PRACH检测DSP优化实现[J].电子设计工程,2018(1):121-125.

[2]BSC9132.QorIQ qonverge multicore baseband processor reference manual[J].Review,2012(6):223-225.