基于FPGA 的图像实时压缩系统设计*

刘勇良,沈三民,李建军,刘文倩

(中北大学仪器科学与动态测试教育部重点实验室,太原 030051)

0 引言

随着多媒体技术、互联网和无线通信的发展,人们对图像在质量和应用适应性方面提出了更高的要求,不仅要保证图像数据存储与传输在现有的条件下顺利进行,还要确保图像数据基本无损地接收[1-2]。如将采集到的大量图像数据不经过任何处理而直接进行存储的话,将会耗费大量的存储资源,将采集到的图像数据在满足要求的前提下进行压缩是有必要的,也是图像测试系统的必然环节。

系统选用FPGA 和专用图像压缩编码芯片ADV212 相结合的图像压缩方案,将JPEG2000 压缩码流通过数据传输接口输出至上位机进行存储。该系统在硬件模块划分和算法选择时充分考虑各个芯片的硬件结构特点,从而极大程度地激发芯片性能,提高了系统灵活性,满足系统实时性的要求。

1 系统总体设计

系统遵循模块化、高集成和高可靠性的指导思想开展设计,以FPGA 为核心,系统由图像采集模块,FPGA 逻辑控制模块,图像压缩模块,图像缓存模块和图像传输模块5 部分组成,系统整体框图如图1 所示。首先信号采集端接收CCD 摄像头接收图像信息并输出标准PAL 制式信号,经专有解码转换芯片转换为8 bit 标准格式的数字信号,之后传入到系统中枢FPGA 中进行数据预处理,图像数据发送到后续模块进行数据压缩处理,压缩完成后输出JPEG2000 标准格式码流送入FPGA 内部FIFO 进行缓存,然后通过传输接口输出至上位机存储。

图1 系统整体框图

2 系统硬件设计

2.1 图像采集模块

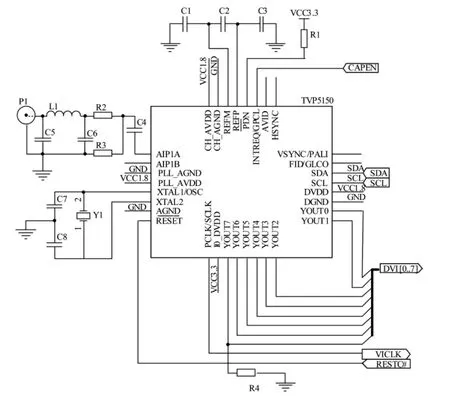

设计前端采集接口电路采用灵敏度高、抗干扰能力强、高速率等特点的CCD 摄像头,型号为PNT-698,该型号模拟摄像头的信噪比大于48 dB,摄像头输出标准的PAL 制式视频信号传输到视频解码芯片,转换为标准格式的数字信号。本系统采用配置灵活的TVP5150 系列视频解码芯片,该芯片可自动识别NTSC/PAL/SECAM 制式的模拟信号,同时支持外同步的YcbCr4∶2∶2 和内同步的ITU-R BT.656两种模式。在正常工作时,功耗仅仅115 mW,具有价格低、体积小、操作简便的特点,目前广泛应用于批量大、高质量和高性能的视频产品[3],如图2 所示。

本系统同时为防止频带外的杂波干扰,在采集前端添加了低通滤波器,系统通过模拟I2C 总线与TVP5150 自身串行接口进行通信,从而确保内部寄存器正确配置,通过拉低YOUT7/I2CSEL 引脚状态设定解码芯片地址为0xB8,图像数据以YCbCr4∶2∶2标准格式输出,芯片内部的PLL 由XTAL 引脚输出频率为14.318 18 M 的时钟信号驱动,同时为达到效果最佳,应保证参考时钟频率误差在+50 ppm 内。

图2 TVP5150 应用电路设计

2.2 数据压缩模块

ADV212 是TI 公司推出的一款可实现6 级小波分解的高精度小波变换处理器,相较于同类型芯片ADV202 功耗低了30%。作为系统图像压缩模块的核心,芯片内部DMA 引擎可提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输,在不可逆模式下其最大数据处理速率可达到65 Mb/s,而有效视频转化的输入数据速率约为124 Mb/s,这对于码流的分解和高速率数据的产生尤为重要[4]。由于单片ADV212 最大数据采样量为1.048 M,在PAL 视频格式下,YCbCr4∶2∶2 标准场精度NTSC 采样点个数小于1.048 M 个点,因此,系统采用单片ADV212 进行图像数据压缩,如图3 所示。

图3 ADV212 电路图

选取一种定制工作方式CS 模式为芯片图像压缩工作模式,该模式可以针对不同的系统制定特定的图像视频格式。系统采集图像数据预处理后,待压缩8 位图像数据经VDATA 总线进入时,表明输入数据的时钟确定,接收的数据进入芯片的小波变换模块,采用压缩速率可达80 Mbit/s 的标准算法JPEG2000,压缩码流从HDATA 输出,通过这种方式最大限度地提高系统的吞吐量,使未压缩的像素数据和压缩数据进行分离,有利于高流量场合应用。

2.3 图像缓存单元

图像缓存模块分为数据缓存和压缩数据FIFO缓存器两个部分。为解决系统各部分因时间上的不同步而导致图像数据混乱丢失和影响帧数据完整性的问题,系统采取在采集、FPGA 和压缩各个模块之间添加缓存模块。数据缓存部分选用两片SDRAM 存储芯片对FPGA 采集和处理的图像数据进行交替存储和读取,保证了数据传输的可靠性。设计选用两片ISSI 公司研发的IS42S86400B,该芯片存储容量为512 Mb,其最高时钟可达166 MHz,通过读写“乒乓”操作,可以对采集端输出图像数据流进行连续处理,并采用管道架构以达到高速数据传输速率。依靠强大缓存空间和传输速率,ADV212 进行上一帧图像压缩时,不影响下一帧图像数据的采集缓存,保证系统实时传输,将图像数据交替读出,数据严格有效地控制并输送给压缩模块进行编码。

为使各系统工作在自己的时钟频率下不需要互相握手就能进行数据交流[5],在FPGA 内部构建了结构稳定的FIFO 缓存器,该缓存器用以接收并缓存图像压缩模块传送的大量数据流,缓解处理器的负担,同时能够匹配不同传输速率的系统,从而提高系统性能。

2.4 图像输出模块

差分驱动器可直接与FPGA 通信,实现压缩数据快速传输。选用RS-422 接口采用差分传输方式,减少信号地线带来的共模干扰,采用DS26C31 和DS26C32 芯片实现上位机与图像采集、压缩电路之间控制命令下传和压缩图像数据上传,同时为尽可能匹配接收和发送端的阻抗,抑制发射干扰现象,在差分422 的接收端设计有120 Ω 的反射电阻。

3 系统逻辑设计

3.1 I2C 配置模块

系统选用的视频解码芯片通过I2C 总线接口进行初始化配置,使得解码芯片完成特定解码功能。I2C 总线是一种高性能芯片间串行同步通信传输的二进制总线,由串行数据线SDA 和串行时钟线SCL两根信号线构成,具有总线数量少、接口控制简单、数据传输率快等优点,其传输模式是双向通信,数据传输速率在100 kbit/s 到3.4 Mbit/s 之间[6-7],I2C总线时序逻辑图如图4 所示。利用FPGA 通过I/O口来模拟I2C 总线串行数据线和串行时钟线时序来发送配置数据,设置总线为标准模式,从而传输速率为100 kbit。I2C 虽然配置简单,但TVP5150 的I2C要求非常高,必须严格按照要求才能配置成功。开始信号、应答信号和结束信号作为I2C 总线传输协议的3 种信号,当SCL 保持高电平,SDA 出现下降沿时视为开始条件,则数据发送开始;当SCL 保持高电平,SDA 出现上升沿时为结束条件,标志数据发送结束。同时该总线数据传输以字节为单位,当数据线满足开始条件后,主机发送7 位地址寻址从器件,之后继续发送第8 位脉冲控制读或写操作表明数据流向,若从器件被寻址则SDA 被拉低电平,即为应答信号。本系统被寻址的前端解码芯片接收到一个字节后必须发送应答信号,告知控制中枢已收到数据,同时当FPGA 数据发送完成后,只能由FPGA 发出停止信号以结束发送。

图4 I2C 总线逻辑时序图

3.2 ADV212 初始化

图5 ADV212 初始化流程图

ADV212 作为压缩模块的核心,对其进行正确的初始化配置是保证系统正常工作的前提。在初始化固件中通过写寄存器的状态字来设定ADV212的工作模式,该芯片初始化流程图如图5 所示。ADV212 初始化首先进行上电复位操作,复位时间为25 us。依据特定的指令命令从直接存储器配置开始,当图像数据到来时,通过设置寄存器PLL_HI 和PLL_LO 配置芯片内部PLL,设计内部时钟后为确保PLL 成功锁定,系统应延迟20 us。本设计采用非加载主机模式设定BOOT,之后加载编码所需固件和配置编码固件参数,通过检查编码ID 是否为SWFLAG 标志寄存器的设定值,从而检测固件装载是否正确。若加载正确,则清除所有中断标记,表明初始化配置完成。

3.3 FPGA 逻辑控制

作为处理系统的中枢,FPGA 决定着系统各个模块协调工作的顺利进行,主要进行控制时序处理、数据处理和数据缓存转发。首先,FPGA 控制前端解码芯片的时钟和读取数据命令,完成视频数据采集到模数转换的控制,利用其强大的数据处理能力完成对ADV212 初始化,加载固件程序确定压缩芯片的编码模式,同时设置其编码参数并等待接收前端采集模块发送的图像数据进行预处理,将处理后的图像数据传送到外部SDRAM 进行缓存。当检测下一帧图像同步上升沿时,严格控制缓存模块的读写时序,读取并控制SDRAM 上一帧图像传送到ADV212 进行压缩处理,下一帧图像数据的采集和预处理不影响上一帧图像数据的压缩与传输,从而保证系统实时操作的要求,将压缩码流通过传输接口传输到上位机,同时FPGA 接收上位机指令来严格控制压缩、发送码流等操作的执行,对整个系统数据流控制及向外发送各工作状态的反馈信息等,逻辑流程图如图6 所示。

图6 FPGA 逻辑流程图

4 系统测试功能验证

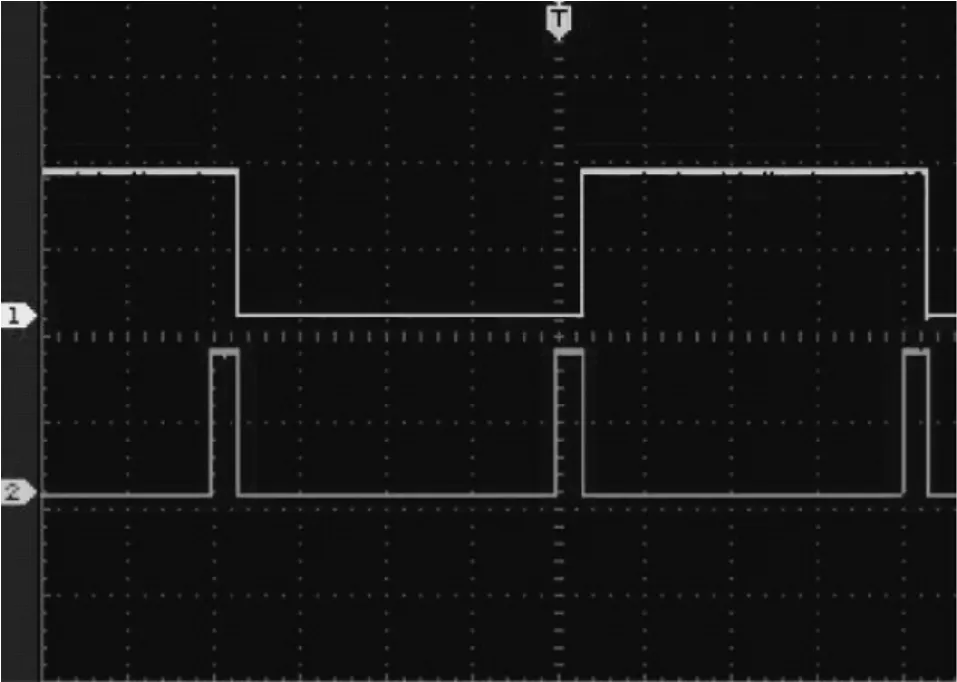

为验证系统总体性能,首先对前端采集模块进行配置测试,系统测试环境如图7。通过示波器测量解码芯片TVP5150 的输出同步信号,测试结果如图8,1 通道为FID(奇偶指示信号),2 通道为VS(场同步信号),奇偶指示信号在场同步信号下降沿处跳变,两者符合配置要求,表明TVP5150 配置成功。

其次,为对比压缩前后的图像质量,系统进行了总体环境试验测试。利用CCD 摄像头对图像进行获取,通过传输接口将原图像传输到上位机并显示。如图9 所示,原图像大小为1.18 MB。主机通过串口助手读取压缩图像数据,如第154 页图10 所示,压缩后的图像大小为50.8 kB。通过观察,虽然系统压缩后的图像部分细节有些模糊,但是总体而言满足了视觉要求,还保证了压缩数据传输的实时性。

图7 系统测试环境

图8 奇偶指示信号与场同步信号

图9 原图像

5 结论

全文介绍了一种采用FPGA 结合专有压缩芯片ADV212 构建的图像采集、压缩和传输为一体的实时系统。相较于传统FPGA 和DSP 相结合的图像压缩系统,利用编解码速度快、通用性强、效率高等特点的专用压缩芯片,实现了系统微体积、微功耗设计,提高系统的整体性能。利用稳定传输总线实现上位机控制命令的实时下达,提升了系统的工作效率。经测试实验表明,该设计方案较好解决了图像压缩实时性的要求,压缩比例达到24∶1,在性能和可靠性等方面达到了预期效果。

图10 压缩重建图像