基于FPGA的BP神经网络识别系统设计

李增刚 王正彦 毛菲菲

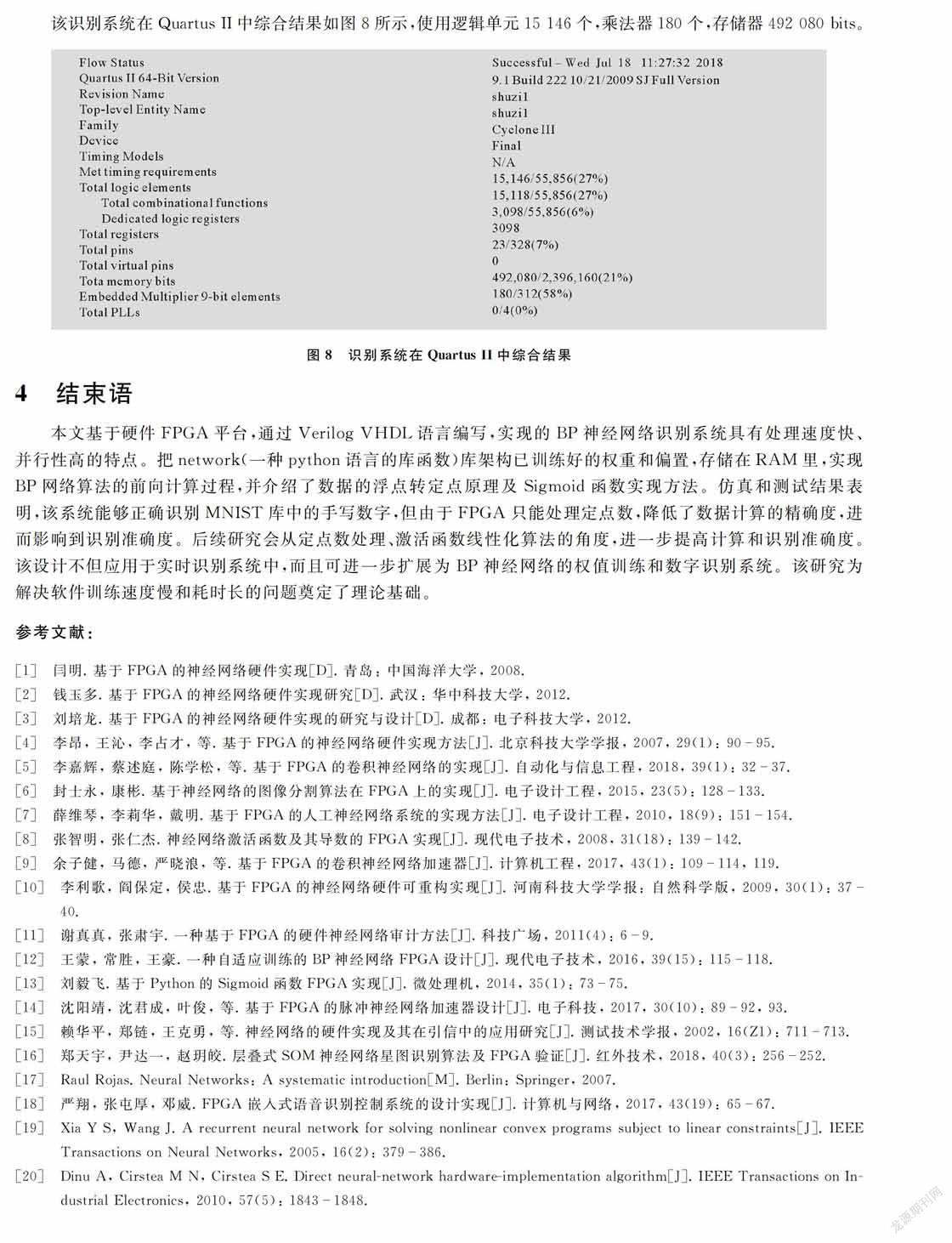

摘要: 针对神经网络算法通常采用软件编程实现所存在的缺点,本文主要对基于现场可编程门阵列(field programmable gate array,FPGA)的硬件BP神经网络识别算法实现进行研究。给出了BP神经网络原理,设计了一个识别MNIST手写数字的3层反向传播算法( back propagation,BP)神经网络识别系统。为测试该电路的识别准确率,选取MNIST数据集中的100个测试数据,采用Verilog语言设计,在FPGA开发平台Quartus II 13.0和Modelsim中,对该电路的识别准确率进行仿真测试。仿真结果表明,输出数字识别准确率约85%,可用于简单的模式识别系统中。该研究为进一步实现硬件神经网络训练系统奠定了理论基础。

关键词: BP神经网络; FPGA; 手写数字识别; 訓练数据; Verilog语言; S型激活函数

中图分类号: TP183; TP391.41 文献标识码: A

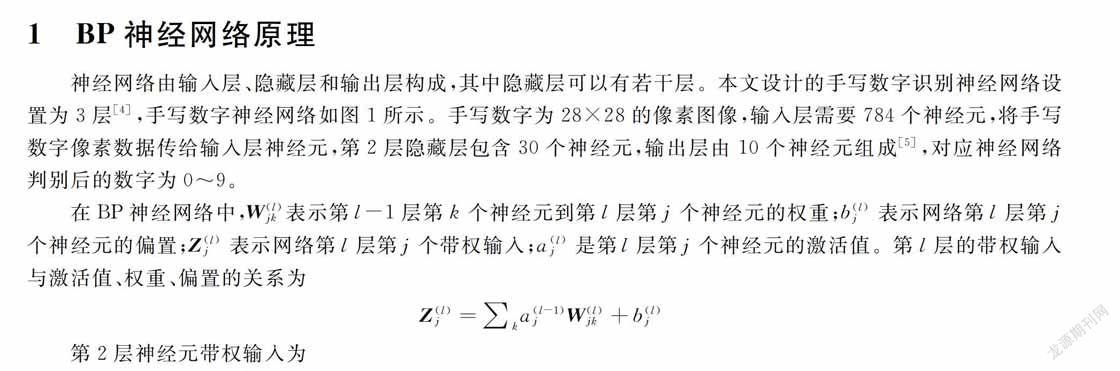

20世纪40年代,神经网络诞生,它是人工智能的一个重要领域。20世纪90年代,随着数学、物理学、计算机的发展和理论的深化及推广,人工神经网络研究步入新的发展期。神经网络通常采用软件的方法实现,但因为神经网络的并行处理特性,硬件实现能提高网络的处理速度[1]。近年来,各位学者和专家提出了FPGA和神经芯片等神经网络硬件实现方法,由于神经芯片成本较高,不适合工业应用,而FPGA是一种功耗低的可编程逻辑器件,内嵌丰富的硬核乘法器及存储器资源,具有的并行计算能力及可重复配置的特点,成为研究神经网络硬件实现的一种理想器件[2]。神经网络硬件实现中的非线性激活函数及其导数是设计的难点之一,闫明[1]叙述了在FPGA上用STAM算法对tans函数的高精度实现,并利用FPGA多次重复配置(可重构性)的特点,充分利用FPGA的逻辑资源;钱玉多[2]结合查找表和线性近似方法,提出了表驱动线性插值法,实现激励函数及其导数,用较少的硬件资源,实现高精度的激励函数及其导数;刘培龙[3]研究了具体实现可重构的脉动体系结构中BP网络映射算法的问题,其方法灵活,硬件实现价值高。神经网络通过模拟人脑神经元获取信息的能力,具有精度高、学习能力较强的优点,在医学图像、智能控制、模式识别、语音识别等多个领域广泛应用。基于此,本文主要对基于FPGA的BP神经网络识别系统进行设计,该设计具有处理速度快、并行性高的特点。该研究为解决软件训练速度慢和耗时长的问题奠定了理论基础。