重排滤波器的实现结构*

陈绍荣 ,何 为 ,刘郁林 ,王 开

(1.陆军工程大学通信士官学校,重庆 400035;2.重庆市经信委,重庆 400015)

0 引 言

在国内外《数字信号处理》教材及著作[1-2]中,从不同角度介绍了实现抽样频率转换的方法,归纳起来有三种实现抽样频率转换的方法:一是若原模拟信号fa(t)可以再生,或是已经记录下来,那么可以重新抽样;二是将f(n)通过D/A变换成模拟信号fa(t)后,对fa(t)经A/D再抽样;三是发展一套算法,对抽样后的数字信号f(n)在“数字域”作抽样率转换,以得到新的抽样。方法一有时不能实现,方法二要再一次受到D/A和A/D量化误差的干扰,方法三是最理想的方法。减少抽样率以去掉多余数据的过程称为序列的重排;增加抽样率以增加数据的过程,称为序列的插值[3-4]。本文只讨论有关重排滤波器的实现方法。

1 序列的重排

以均匀间隔T对连续时间信号fa(t)抽样,得到序列f(n)=fa(nT),若希望将抽样率fs减小M倍,即变成fs/M,则最简单的方法是对f(n)重排,用符号表示,即:

式(1)表明,对序列f(n)重排,等价于将连续时间信号fa(t)的抽样间隔变成MT,即抽样率变成fs/M。

2 重排滤波器

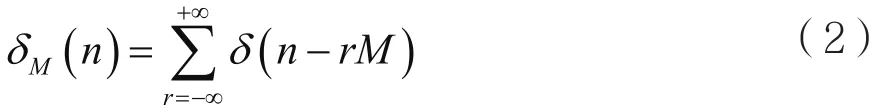

设周期为M的周期冲激序列为:

考虑到式(2),则有:

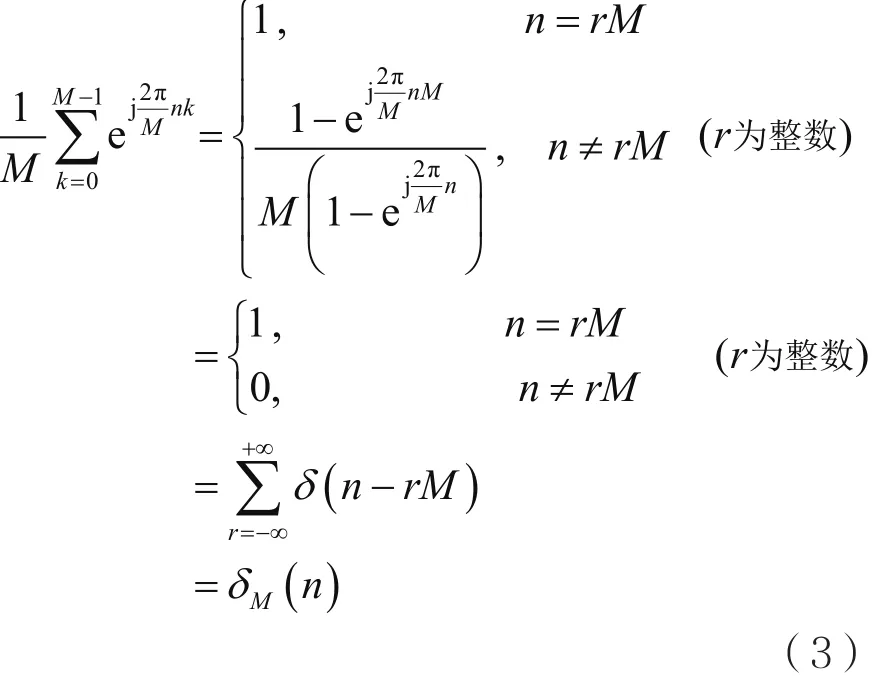

考虑到式(3),对式(1)两边取DTFT,可得重排序列y(n)的频谱,即:

考虑到式(4),则有:

式(5)表明,重排序列y(n)的频谱Y(ejω)仍然是周期为2π的周期函数。

由式(4)可知,重排序列y(n)的频谱Y(ejω)是序列f(n)的频谱F(ejω)先作M的扩展,再将ω轴上每隔 2π的频移F(ej(ω-2πk)/M)叠加除以M。即重排序列y(n)的频谱Y(ejω),在一周期2π内的谱图是由M个F(ej(ω-2πk)/M)(k=0,1,2,…,M-1)叠加除以M构成的,因此Y(ejω)中存在频谱重叠。

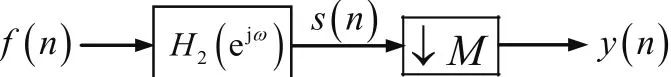

为使重排序列y(n)的频谱Y(ejω)不出现重叠,一种有效的方法是将序列f(n)的频谱F(ejω)位于主值区间[-π,π]上的部分限制在子区间之内,可以利用前置数字低通滤波器H2(ejω)来完成这一任务,如图1所示,其中前置数字低通滤波器的频率特性为:

式中:

其中,ε(ω)为单位阶跃函数。

图1 重排前的滤波

在图1所示的重排滤波中,设频率特性为H2(ejω)的数字低通滤波器的单位冲激响应为h2(n),则有:

由于序列f(n)的频谱F(ejω)是周期为2π的周期函数。对式(8)两边取DTFT,并注意到式(6),可得前置数字低通滤波器的输出序列s(n)的频谱,即:

考虑到式(4)及式(9),则重排序列y(n)的频谱为:

式中:

由式(11)可知,Y0(ejω)的最高频率不超过π,因此,按式(10)对Y0(ejω)作周期2π延拓时,重排序列y(n)的频谱Y(ejω)将不会出现重叠。

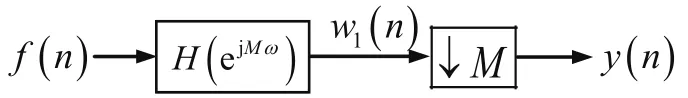

3 基于减抽样的等价系统

基于减抽样的系统Ⅰ,如图2所示。

图2 基于减抽样的系统Ⅰ

在图2中,有:

考虑到:

对式(13)两边取DTFT,并注意到式(4),则有:

将式(12)代入式(14),可得:

式中:

由式(16)及式(15),可得其等价系统,如图图3所示。

图3 基于减抽样的系统Ⅱ

结论1:对比图3和图2可知,若重排器从后置变为前置,则系统的频率特性扩展M倍;反之,若重排器从前置变为后置,则系统的频率特性压缩M倍。这样才能够保证在相同输入序列f(n)作用下,级联系统有相同的输出序列y(n)。

4 重排滤波器的实现结构

在如图1所示的重排滤波中,由于已设数字低通滤波器H2(ejω)的单位冲激响应为h2(n),一般都用FIR数字低通滤波器来实现该数字低通滤波器。设h2(n)的长度为N,即h2(n)=h2(n)RN(n),并且满足N/L为正整数。RN(n)=ε(n)-ε(n-N),其中ε(n)为单位阶跃序列。

在实现如图1所示的重排滤波时,存在下述5种具体实现结构。

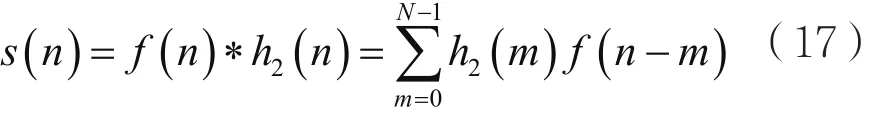

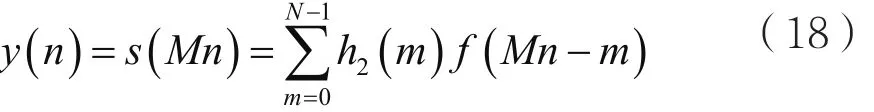

4.1 重排滤波器的直接实现结构

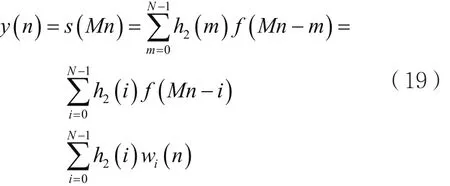

在如图1所示的重排滤波器中,有:

考虑到式(17),则有:

由式(17)及式(18)可知,如图1所示的重排滤波器可以用如图4所示的直接实现结构。

图4 重排滤波器的直接实现结构

若对fa(t)以fs的速率抽样获得f(n),则重排滤波器的直接实现结构有一个缺点,因为h2(n)工作在高抽样率(即fs)状态,序列f(n)的每一位的值都要和FIR数字低通滤波器h2(n)的系数相乘,再按式(17)相加得到序列s(n)。由于输出序列y(n)是将序列s(n)中相距M位的序列值抽取出来依次重新排列的。因此,有较多的乘法浪费。

4.2 减少乘法次数的重排滤波器的直接实现结构

其实,式(18)可写成:

式中:

其中:

式(21)表明,将输入序列f(n)延迟i位,得到序列pi(n);式(20)表明,对序列pi(n)作M倍重排,得到序列wi(n);式(19)表明,先将序列wi(n)与h2(i)相乘,再按该式求和,得到输出序列y(n),如图5所示。

图5 减少乘法次数的重排滤波器的直接实现结构

因此,与图4的重排滤波器的直接实现结构相对照,更合理的方法是用图5的结构来实现。在该图中,先对输入f(n)作延迟,得到序列pi(n)=f(n-i)(i=0,1,2,…,N-1), 并 对pi(n)分 别 作M倍 重 排,得 到序列wi(n)(i=0,1,2,…,N-1),然后wi(n)与h2(i)(i=0,1,2,…,N-1)对应相乘再相加,得到输出序列y(n)。图5所需要的乘法数只是图4重排滤波器直接实现结构的1/M。

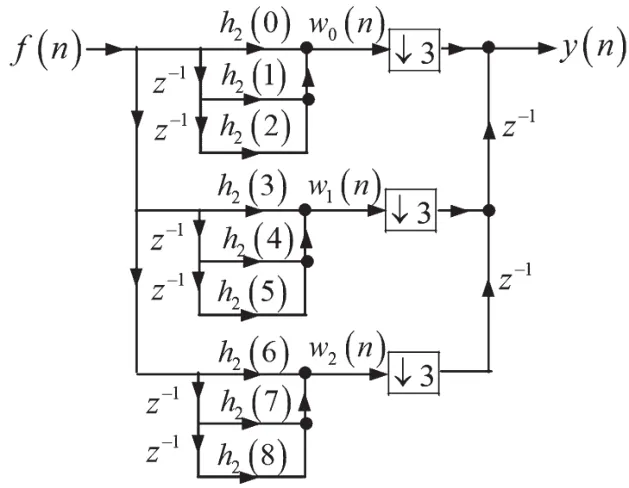

4.3 重排滤波器的分段实现结构

若定义M倍重排滤波器第j段的单位冲激响应为

式中,j=0,1,2,…,N/M-1,RM(n)为矩形窗,并且RM(n)=ε(n)-ε(n-M)。

由式(22)可知,利用pj(n)可将FIR数字低通滤波器h2(n)分成N/M个子FIR数字滤波器。考虑到式(18),则有:

式中,yj(n)可以表示为:

并且:

由式(23)、式(24)及式(25)可知,可以将图1的重排滤波器中的FIR数字低通滤波器h2(n)分成N/M段,其中,每一段是长度为M的子FIR数字低通滤波器,并且都具有相同结构。

若FIR数字低通滤波器h2(n)的长度N=9,取M=3,则三倍重排滤波器的分段实现结构,如图6所示。

图6 三倍重排滤波器的分段实现结构

4.4 减少单位延迟器的重排滤波器的分段实现结构

与重排滤波器的分段实现结构图6相对照,更合理的方法是利用图7的结构来实现。在该实现结构中,单位延迟器的数目减少了一半。

图7 减少单位延迟器的三倍重排滤波器的分段实现结构

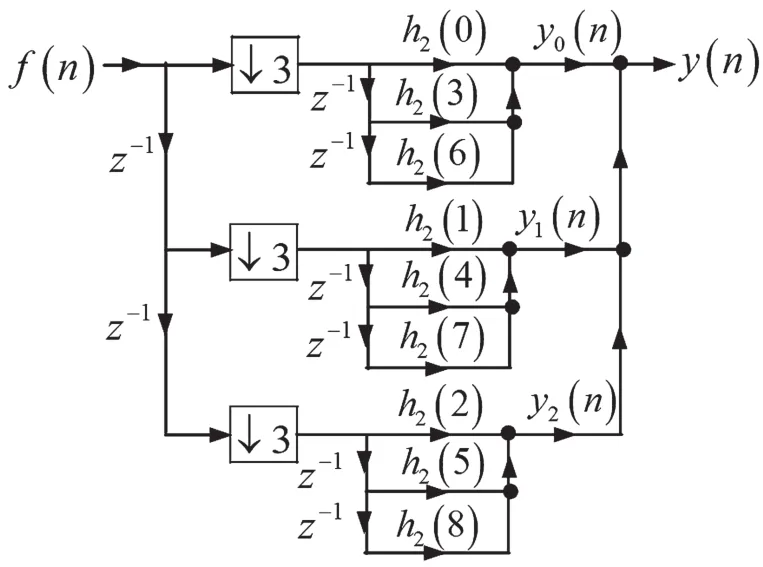

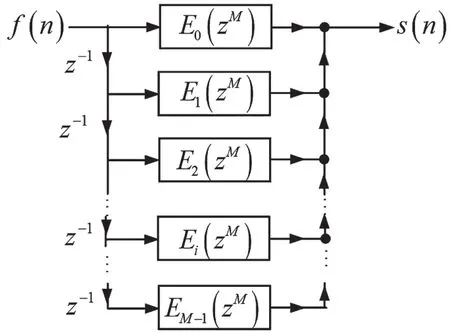

4.5 基于多相分解的重排滤波器的实现结构

考虑到图1所示的重排滤波器,则有:

式中,yi(n)可以表示为:

并且:

称ei(n)为h2(n)的第i个多相分量。

考虑到式(26)、式(27)及(28),则基于h2(n)多相分解的重排滤波器实现结构,如图8所示。

图8 基于h2(n)多相分解的重排滤波器实现结构

若h2(n)是N点的FIR数字低通滤波器,并且N=9,取M=3,则将h2(n)分成了M=3个子FIR数字滤波器,各子FIR数字滤波器的长度为N/M=3,并且具有相同结构。考虑到式(28)、式(27)及式(26),则基于h2(n)多相分解的重排滤波器实现结构,如图9所示。图9左边的两个单位延迟z-1如同一个和原抽样率同步的波段开关一样,将输入序列f(n)分成3组,每一组依次相差一个延迟。各组经M=3倍的重排后,再分配给每一个子FIR数字滤波器。图9中3个子FIR数字滤波器的结构相同,仅是滤波器的系数相差了M个延迟,因此称这些滤波器为多相数字滤波器。

图9 基于h2(n)多相分解的三倍重排滤波器实现结构

其实,可以通过下述方式获得基于h2(n)多相分解的重排滤波器的实现结构。

设:

一般称ei(n)为h2(n)的第i个多相分量。

令:

由于:

由式(31)和式(32),可得:

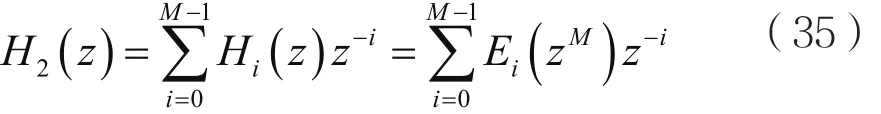

式(33)表明,数字低通滤波器h2(n)可以分解成多相分量ei(n)=h2(nM+i)(i=0,1,2,…,M-1)的M倍插值hi(n)(i=0,1,2,…,M-1)的延迟之和。

对式(31)两边取ZT,可得:

对式(33)两边取ZT,并注意到式(34),可得:

考虑到式(35),则可以得到基于h2(n)多相分解的实现结构,如图10及图11所示。

图10 基于h2(n)多相分解的实现结构Ⅰ

考虑到图10所示的基于h2(n)多相分解的实现结构,则图1的重排滤波器可用图12来表示。

由于和序列s(n)的M倍重排等价于各个序列M倍重排之和,因此,可将图12画成图13。

图11 基于h2(n)多相分解的实现结构Ⅱ

图12 基于h2(n)多相分解的重排滤波器的实现结构Ⅰ

图13 基于h2(n)多相分解的重排滤波器的实现结构Ⅱ

由结论1可知,将图13中的重排器从后置变为前置,则子系统的频率特性扩展M倍,即将子系统的转移函数Ei(zM)(i=1,2,…,M-1)变成转移函数Ei(z)(i=1,2,…,M-1)。这样就得到了与图8相同的基于数字低通滤波器h2(n)多相分解的重排滤波器的实现结构,如图14所示,只不过其中的子系统用z域描述而已。

图14 基于h2(n)多相分解的重排滤波器的实现结构Ⅲ

5 结 语

本文针对重排滤波器的实现问题,给出了重排滤波器的直接实现结构、减少乘法次数的重排滤波器的实现结构、重排滤波器的分段实现结构、减少单位延迟器的重排滤波器的分段实现结构及基于多相分解的重排滤波器的实现结构,并用一种新的思路和方法,导出了基于多相分解的重排滤波器的实现结构。