FPGA静态时序约束的策略研究及探讨*

刘 晟

(上海诺基亚贝尔股份有限公司,江苏 南京 210037)

0 引 言

随着半导体芯片和人工智能产业的发展,现场可编程门阵列(Field Programmable Gate Array,FPGA)逐渐受到重视。其灵活性和可定制性都是非常具有吸引力的特性。为解决系统设计问题,FPGA 越来越多地整合系统模块,同时进一步集成了重要控制功能。

随着FPGA的规模及速度的持续提高,被测试设计(Device Under Test,DUT)的时序验证及逻辑功能验证必须分开进行:寄存器传输级(Register Transfer Level,RTL)验证电路逻辑功能的正确性;静态时序分析(Static Timing Analysis,STA)验证电路时序的正确性[1]。STA工具通过给设计添加多个时序约束,实现控制逻辑的综合、映射及布局布线,以此来规范FPGA的设计时序,使设计达到满足全部的时序要求[2]。

1 时序约束的基本概念

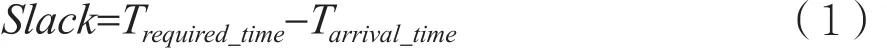

时序分析的方法是检查FPGA内部布局布线的延时,保证所有时序的有正时序裕量,即满足:

式中,Trequired_time表示所约束时长,Tarrival_time表示实际延时,Slack表示时间裕量,为正表示时序收敛。时序裕量的计算需要依据不同的时序路径,分析约束条件,得到设计频率最高值。STA工具将DUT上的时序路径分成4种:

(1)输入端口→触发器D端口(Pad-to-Setup);

(2)触发器CLK端口 → 触发器D端口(Clock-to-Setup);

(3)触发器CLK端口 → 输出端口(Clockto-Pad);

(4)输入端口 → 输出端口(Pad-to-Pad)。

时序分析数据传输路径的示意图如图1所示。任何复杂的时序电路基本都可以用该模型来表示。只有确保数据准确无误地在触发器之间传输,才能确定数据传输延时的区间。

图1 数据传输路径图

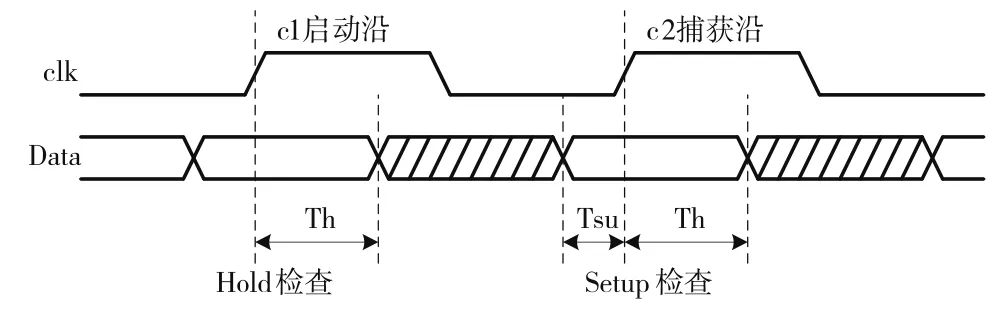

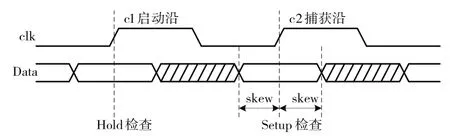

时钟沿到达前数据从不稳定状态过渡到稳定状态所经历的时间称为建立时间(Tsu)。数据在稳定后需要在时钟上升沿保持的时间称为保持时间(Th)。建立时间和保持时间是矛盾的两方面。图2为同一时钟下的建立时间与保持时间的关系。Tco为时钟上升沿到来后,触发器输出端口产生信号输出所需时间为触发器输出时间。

图2 同一时钟下的时间关系图

图2可以看作是图1的子集,是时序电路中的基本模块结构。其时序如图3所示。

建立时间和保持时间必须满足式(2)、式(3):

Tpd为时钟从源触发器(Source clk)到目标触发器(Destin clk)的路径延时。

图3 建立时间和保持时间时序图

2 时钟约束

FPGA所有的同步路径都基于时钟,如晶振产生的时钟、以太网恢复出的时钟、ADC/DAC的数据时钟等,称为主时钟(Primary Clock)。其他由主时钟产生的时钟,称为衍生时钟(Generated Clock)。

主时钟需要通过命令create_clock创建,如定义一个名为clk_in,周期为10ns,占空比50%,通过输入端口clk_in输入到FPGA的主时钟:

create_clock -name clk_in -period 10ns get_ports clk_in

创建主时钟后,STA工具自动确定该主时钟的起点为仿真时序的“零点”,在“零点”之前的路径延时都被忽略。如果主时钟是以差分对的形式输入FPGA,那么只需要约束差分的正相端口。

衍生时钟分为两种,一种由时钟管理单元创建,其约束由工具自动推导得出,不需要用户手动约束;另一种由用户通过寄存器或组合逻辑设计得到,通过命令create_generated_clock来创建约束。此外还需要考虑时钟的延时(latency)和抖动(jitter)等因素。由图2可以看出,由于存在时钟路径,到达REG1和REG2的时钟有先后,称为时钟延时,用set_clock_latency命令约束。外部器件输入时钟本身属性,或者电源噪声、电路板噪声等因素,都会导致输入时钟产生抖动,用set_system_jitter命令约束。

对于异步时钟,假设图2中的REG1和REG2的时钟异步,则要约束不同的时钟组,以避免路径的跨时钟域(Clock Domain Cross,CDC)错误。例如:

create_clock_groups -name asy_clk -asynchronous-group source_clk -group destin_clk

3 I/O约束

I/O数据传输方案根据不同的数据速率,对齐方式,时钟源等来做区分[4]。尽管场景不同,但都适用于相同的原则:分析FPGA与上下游设备的建立保持时间。

3.1 Input和 Output约束

约束设计中I/O约束的命令有以下几种[3]:

(1)set_max_delay;

(2)set_min_delay;

(3)set_input_delay -max <maxdelay> -min<mindelay>;

(4)set_output_delay -max <maxdelay> -min<mindelay>。

命令(1)和命令(2)用来约束异步组合逻辑接口。组合逻辑延时是不被任何时钟序列捕获的输入和输出FPGA的路径延时,传输路径如图4所示。

图4 组合逻辑的延时图

命令(3)和命令(4)用来约束时序逻辑接口。通过max和min参数设定最大/最小延时时间。

图5 同步逻辑输入电路

图5为Input约束。Input延时表示输入数据相对于输入时钟的时间差。

Input的最大和最小输入延时分别为:

图6为Output约束。Output延时表示输出数据相对于输入时钟的时间差。

Output的最大和最小输出延时分别为:

图6 同步逻辑输出电路

为保证约束的完整性,Input和Output的maxdelay和mindelay必须同时约束。Input的maxdelay描述的是setup相关的上游器件的延时;mindelay描述的是hold相关的上游器件的延时。Output的maxdelay描述的是setup相关的下游器件的延时;mindelay描述的是hold相关的下游器件的延时。

3.2 建立保持时序分析

STA是基于基本元素(Basic Element Logics,BELs)的。即使路径上有多个BEL封装在同一个切片(Slice)中,仍然需要对每个BEL进行时序特性描述。

setup检查下一个时钟周期之前传递完数据。第一个clock的上升沿发送,第二个clock的上升沿接收。当时钟连接到FPGA的port/pin/net时,检查包括时钟从连接到路径端点的传播。数据路径延时使用路径最长延时,而目标时钟延时使用路径最短延时。setup检查从起始点时钟的启动沿开始,到终结点时钟的捕获沿结束。

hold检查数据在接收端的时钟边沿后还仍然能稳定保持的时间。同一个时钟沿既是启动沿也是捕获沿。这就意味着当时钟发生跳变时,引起的时钟更改是否在相同的时钟边沿到达目标模块(通常是从同一个时钟的上升沿触发)之前传播到目标模块。其中最短延时被用于源时钟和数据路径的延时,最长延时被用于目标时钟的延时。

3.3 系统同步与源同步

I/O接口可以分为系统同步和源同步。前者是指FPGA和上下游器件之间仅传递数据,时钟通过系统板级同步;后者是指FPGA和上下游器件之间同时传递数据和时钟,用时钟同步数据。源同步基本不受传输线延时影响,时钟频率更高,约束也相对更复杂。

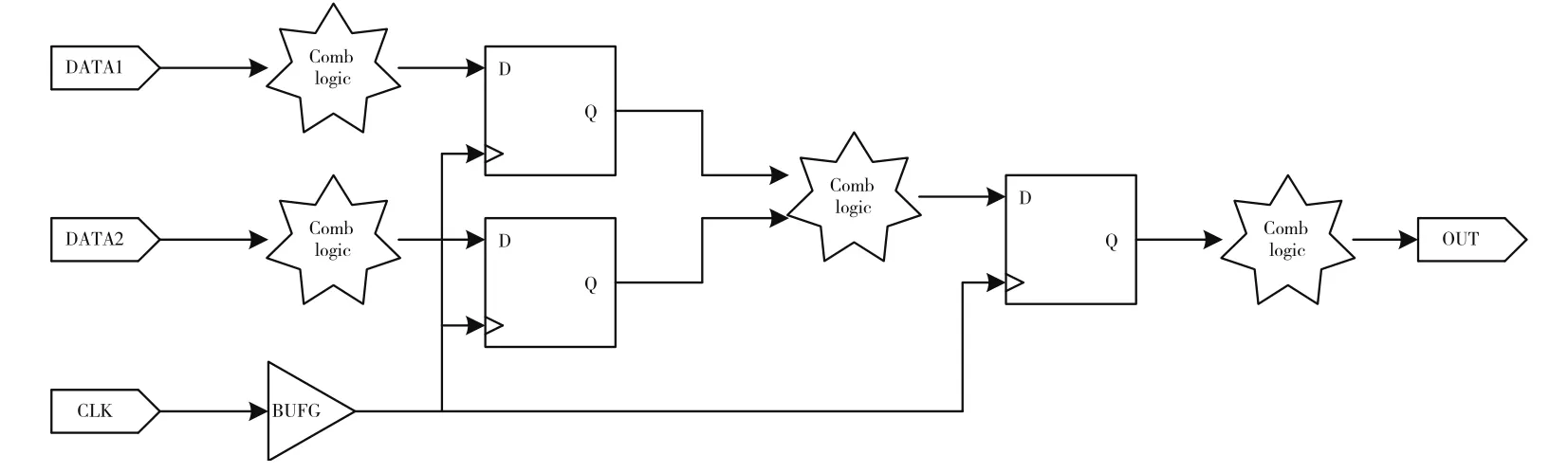

在系统同步模式下,仅需考虑FPGA上下游器件延时Tco及数据板级延时Tdata_PCB。I/O的启动与捕获如图7所示。启动沿对应上游器件时钟,捕获沿对应下游器件时钟。

图7 系统同步I/O时序图

在系统同步接口中,捕获数据的预期边沿是靠近数据窗口末尾的边沿。当Tco和Tdata_PCB已知时,可直接指定FPGA输入延时。由此可以导出FPGA接收到的实际有效数据在最大和最小情况下的通用数据窗口。每个捕获沿也是下一个数据的启动沿,可以用来做hold分析。相应约束为:

在源同步模式下,数据和随路时钟之间存在相位关系,接收端必须使用该时钟来锁存数据。源同步可划分为单数据率(Single Data Rate,SDR)和双数据率(Double Data Rate,DDR)、中心对齐和边沿对齐等多种方式。这里以中心对齐的SDR方式为例,I/O的启动与捕获如图8所示。

图8 源同步I/O时序图

在中心对齐的SDR方式下,FPGA捕获的波形数据不依赖于捕获沿。因此,最大和最小延时通常通过图中所示的无效数据(skew)来计算得到。当捕获沿时间早于使用负设置捕获的数据时,STA工具中的默认设置时间分析不能将前沿同时视为启动沿和捕获沿。相应约束为:

4 例外约束

如果分析不相关的时钟域信号,就会得到错误的结果。因此STA工具需要知道哪些路径要进行特殊的时序分析。主要有两种类型:多周期路径约束和假路径约束。

4.1 多周期路径约束

上文的I/O约束有一个基本的条件,就是数据在单个时钟周期内完成寄存器之间的传输。但是在实际的设计中,设计的复杂性会导致延时较大,往往数据在发送多个时钟周期之后才起作用[3],导致启动和捕获之间需要多个时钟周期。

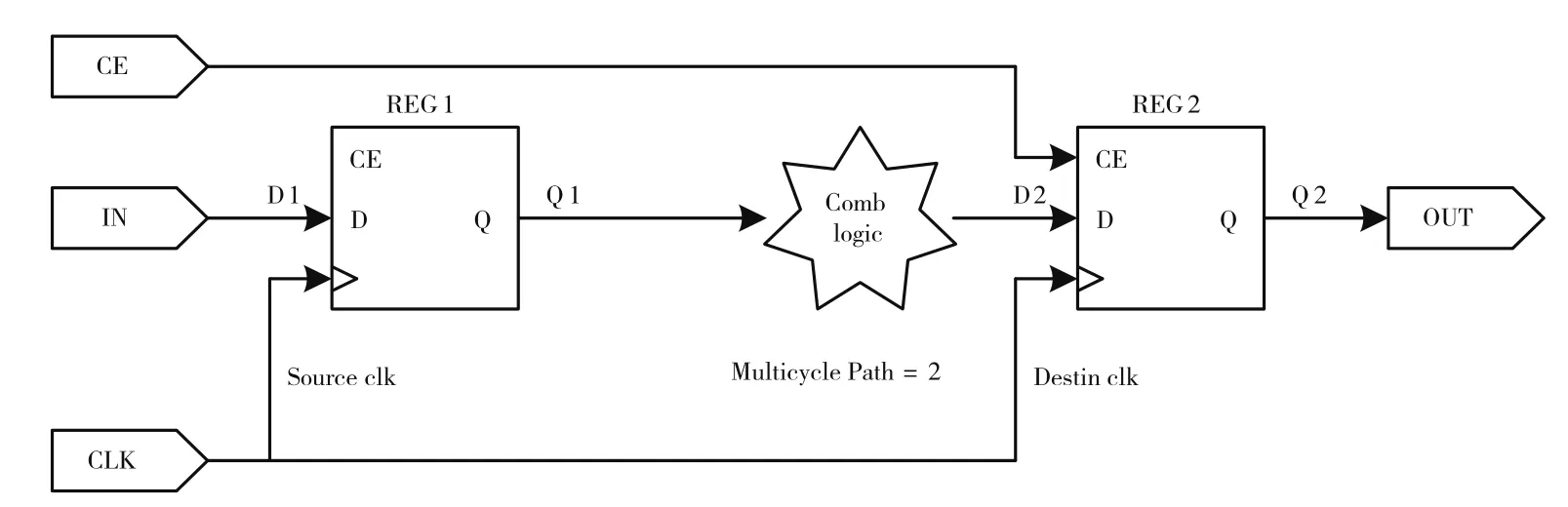

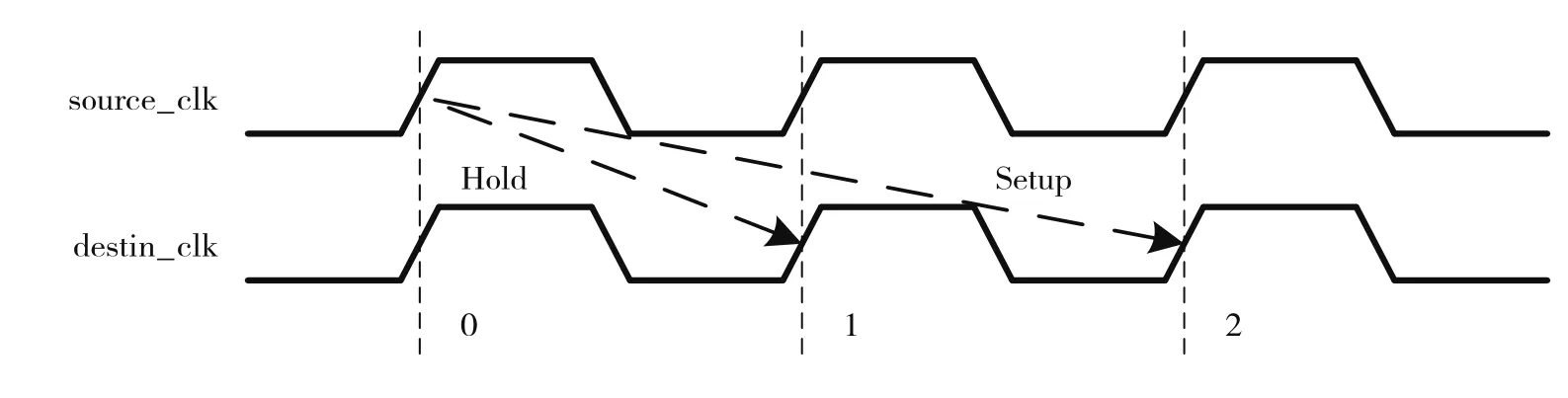

在上文的图2中,如果中间的组合逻辑模块延时较大,需要多个时钟周期来完成从REG1到REG2的数据传输,就称为多周期路径,如图9和图10所示。一个很好的解决方法是使用时钟使能信号,在N个时钟周期后读取数据。将数据率变为时钟频率的1/N。

图9 多周期路径约束原理

图10 多周期路径约束时序

如果不设置多周期路径约束,则STA工具会按照单周期路径来约束,会导致时序不满足,或者过分优化,造成过约束,侵占本该更高优先级的约束资源[3]。因此最好在模块描述中给出多周期路径的注释,并添加到约束文件中。相应的约束命令为:

其中N表示经过多周期路径的时钟数。

4.2 假路径约束

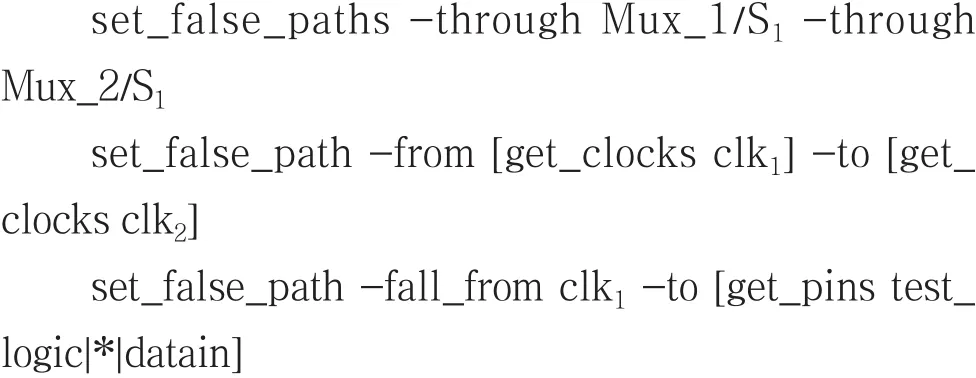

所谓“假路径”,是设计人员告诉STA工具那些不需要进行约束分析的路径。主要包括3种:(1)在逻辑函数中不存在的路径,比如多个主从总线通信、多路选择功能等;(2)多异步时钟域的路径,可以使用先进先出(First Input First Output,FIFO)模块进行通信;(3)测试功能逻辑路径,如内建自测(Built-in Self Test,BIST)、边界扫描测试等。以上情况设置假路径的约束命令分别为:

假路径的设置,可以确保定义的路径不做检查,提高STA效率。前提是要求设计人员对设计路径熟悉,同时也会增加约束文件的复杂度。如果判断不好约束的优先级,有时也会适得其反,因此需要谨慎操作。

5 结 语

本文探讨了几种FPGA的静态时序约束方法,分析了电路时序原理,介绍了相应的语句。FPGA时序约束越来越复杂,用好时序约束,对逻辑电路的设计能起到事半功倍的效果。然而时序约束不能一概而论,用固定的几种约束方法解决所有的时序问题。需要FPGA设计人员在实际的工作中积累经验,找准阻碍时序收敛的根本原因分析解决。