FPGA实现角膜变形信号峰值时刻检测的研究

杨成禹,王琦,毕伟权,肖作江

(1.长春理工大学 光电工程学院,长春 130022;2.吉林东光精密机械厂,长春 130013)

青光眼是我国当前重要致盲眼病之一,眼压升高是其主要致病机理。眼科界倡导以采用空气脉冲检测法的非接触式眼压检测取代接触式眼压检测[1],来避免产生眼部感染、减少患者痛苦[2]。在非接触式眼压检测系统中,角膜变形信号峰值时刻检测在整个系统中起着至关重要的作用,决定系统最终的测量精度以及时间分辨率[3]。目前普遍采用由比较器、DAC以及ARM组成的角膜峰值时刻检测系统,由DAC与输入信号经比较器进行比较,主控芯片负责DAC和比较器的电压输出控制以及峰值时刻判定,但由于程序顺序运行且器件自身具有一定延迟性产生延时,导致获得的峰值时刻不够精准。只有获得两次精准的峰值时刻,才能准确得到对应时刻下来自压力传感器的眼压压力信号,最终完成眼压检测。可见设计一套高精度的角膜变形信号寻峰系统对非接触式眼压检测技术具有重要意义。FPGA具有并行处理、逻辑资源丰富等优势[4],可减少延时误差且不需比较器及DAC电路部分便可完成峰值检测功能,可减少硬件电路的设计。因此,提出一种基于FPGA的非接触式角膜变形信号峰值时刻检测系统,选用Altera公司的Cyclone IV系列的EP4CE15F17C8N作为主控制器,通过FPGA状态机来实现阈值比较寻峰算法,达到了检测角膜变形信号峰值以及确定峰值精准发生时刻的效果。

1 检测系统总体结构

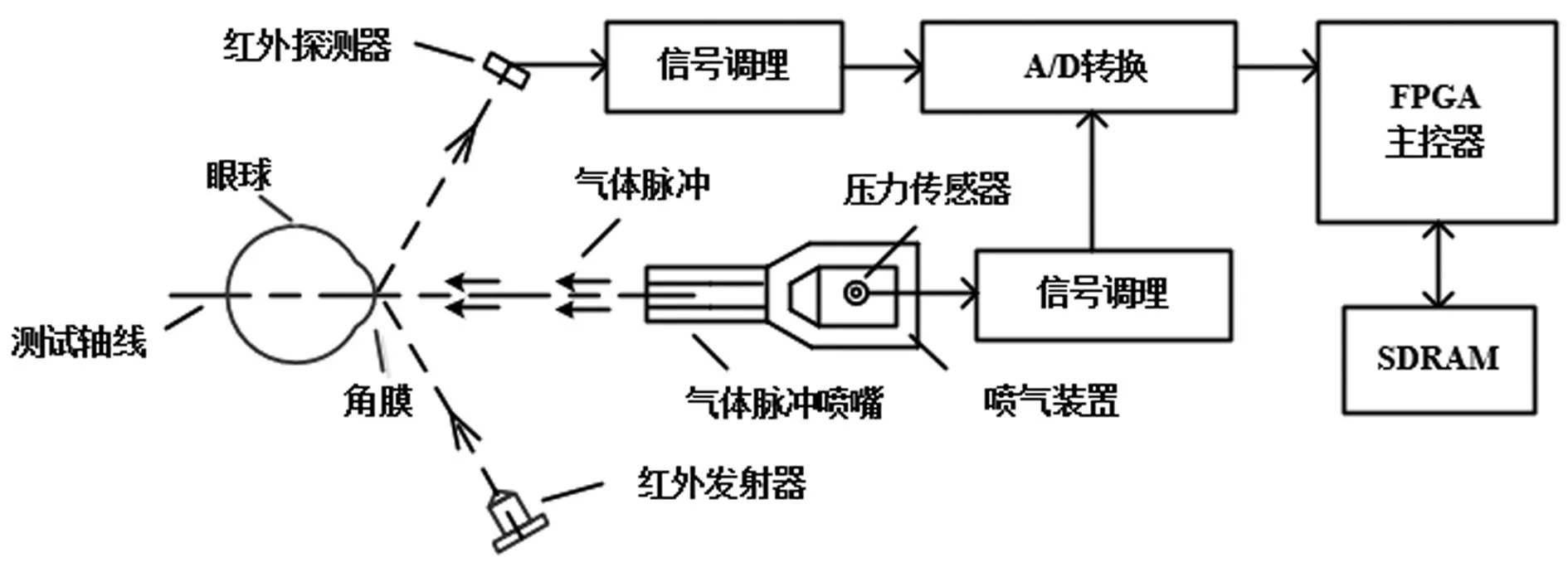

检测系统主要由FPGA主控器、红外发射器、红外探测器、压力传感器、A/D转换器以及SDRAM存储器构成。检测系统整体结构如图1所示,红外探测器放在红外发射器相对测试轴线的对称位置上,由气体脉冲喷嘴喷出的气体脉冲作用于角膜表面使角膜产生形变,发射器发出的光经不同形态下的角膜反射后,由探测器接收反射光信号并进行光电转换,得到角膜变形信号。

图1 检测系统整体结构

当角膜被压至平时,探测器输出角膜变形峰值信号,此时压力传感器测得气体脉冲将眼膜压平的眼压压力,即为眼内压值。对角膜变形信号与压力传感器输出的眼压压力信号进行信号调理后,经由A/D转换器,将两路转换后的信号送入FPGA主控器,由FPGA进行角膜变形信号的寻峰处理以及精准峰值时刻的确定,并由SDRAM完成相关数据存储。

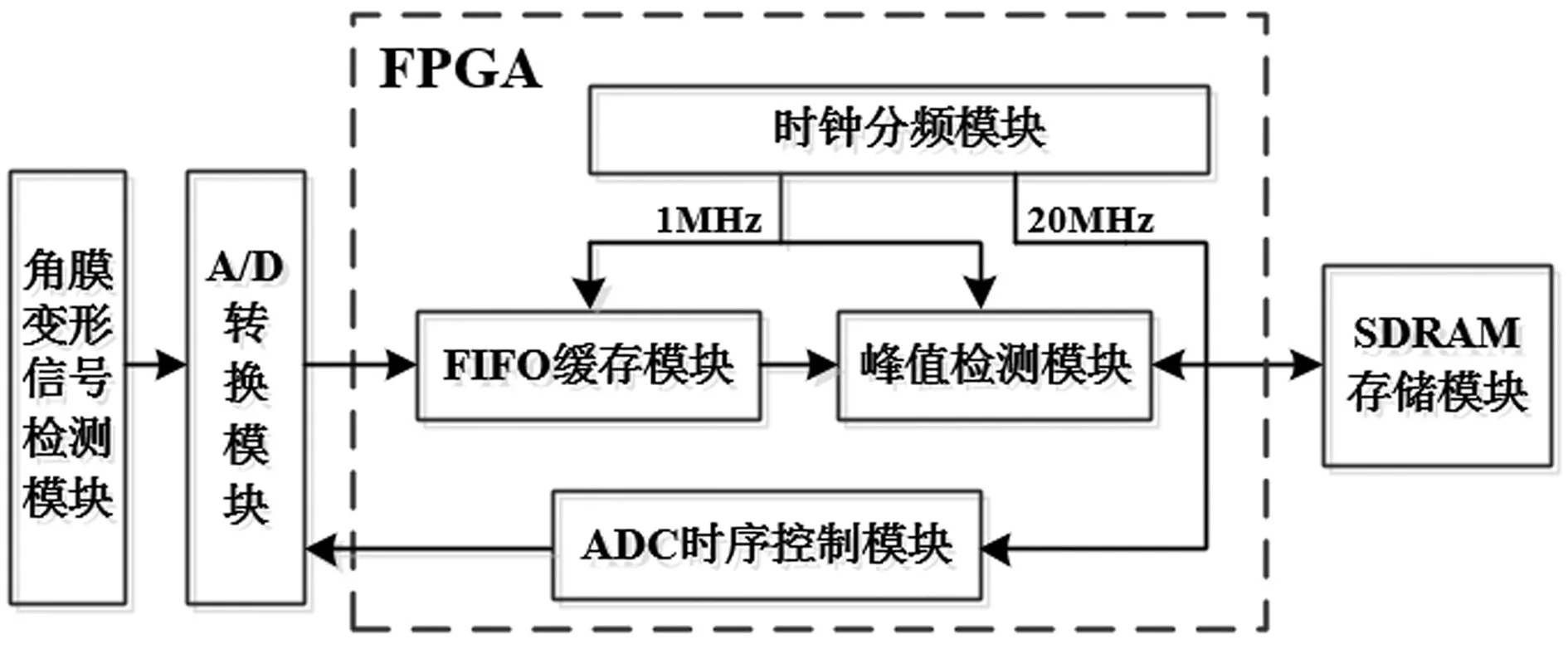

对基于FPGA非接触式角膜变形信号峰值时刻系统进行功能模块化的系统设计,图2为峰值时刻检测原理,如图2所示,系统主要分为角膜变形信号检测模块、A/D转换模块、FPGA主控模块以及SDRAM存储模块。

图2 峰值时刻检测原理

其中,FPGA主控模块采用了自顶向下的方法,依据功能划分为时钟分频模块、FIFO缓存模块、峰值检测模块以及ADC时序控制模块几部分。利用Verilog HDL语言对相关模块进行设计,采用Quartus II开发环境对各个模块集成的顶层设计文件进行综合,实现对信号的采集和处理等操作。

2 峰值时刻检测系统模块化设计

2.1 角膜变形信号检测模块

角膜变形信号检测模块由红外发射器、红外探测器和信号调理电路几部分组成。由于1550nm波长位于人眼安全激光波段且处于大气传输窗口是作为检测眼部信息的理想波长,故前端红外发射器和红外探测器分别采用SEALAND公司发射波长为1550nm的XL503320IRC以及接收波长范围在800-1750nm的XL2835PD13。前置运放采用ADI公司20MHZ轨到轨高输出电流放大器AD8616。角膜变形信号检测电路如图3所示,红外探测器与运放的连接方法属于电流放大型,两个输入端同极性相连,电阻R1作为反馈电阻。XL2835PD13的光电流Isc为22μA,R1=100kΩ,输出电压可满足A/D转换器模拟量输入范围。红外探测器工作在两端无偏压的光电池状态,此状态下红外探测器没有反向偏置电压,故暗电流非常小减小了输出噪声[5]。

图3 角膜变形信号检测电路

当气体脉冲喷嘴向角膜喷射气体时,红外探测器接收到的光信号强弱随角膜状态的改变而发生变化,图4为角膜变形过程。

图4 角膜变形过程

其中图4a)为初始状态角膜,此时来自发射器的基本准直光束在被弯曲的角膜表面反射后发散,使红外探测器接收到的信号相对较弱。随着空气脉冲的推进,角膜产生图4b)的第一压平状态,光束由曲率半径无限大的角膜表面反射后,使得更多的光到达红外探测器形成峰值。空气脉冲因惯性继续推进,角膜会向内凹陷形成图4c)状态,红外探测器接收到的光信号减弱。随着空气脉冲的消退,角膜恢复至图4d)的第二压平状态产生第二次峰值信号,最终恢复图4e)的角膜自然状态。故只有当角膜处于两次压平状态时,探测器输出电压值最大的峰值信号。

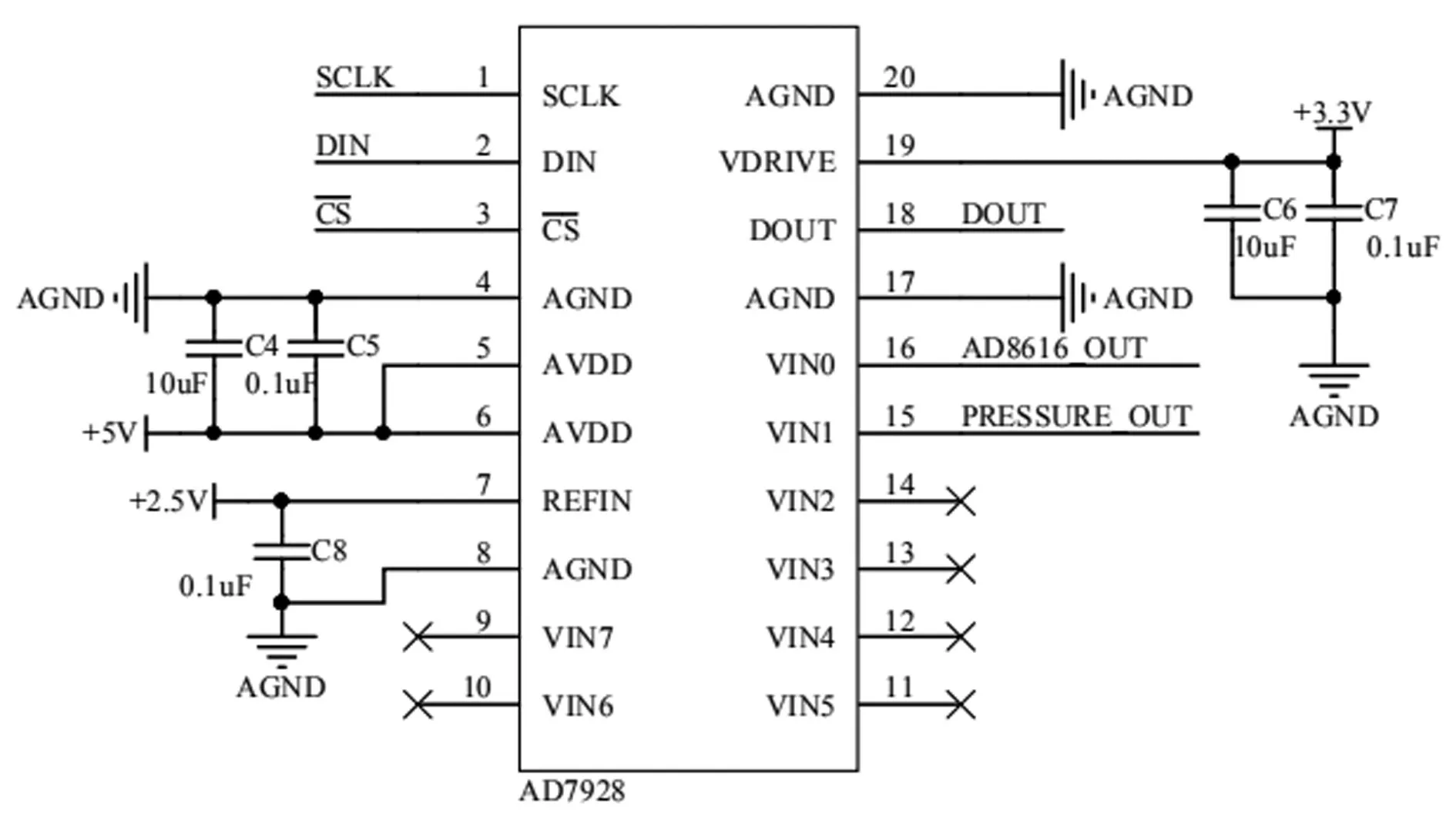

2.2 A/D转换模块

A/D转换芯片采用ADI公司12位逐次逼近型A/D转换器AD7928,最高采样速率为1Msps。AD7928转换模块如图5所示,先选通VIN0通道对角膜变形信号进行采集,再选通VIN1通道采集来自压力传感器的眼压压力信号。转换结果通过DOUT串行输出,采用标准SPI协议。系统采用12位ADC可达到1mv的测量精度,实现高精度角膜变形信号的转换。

图5 AD7928转换模块

2.3 FPGA主控模块

2.3.1 时钟分频模块

为确保ADC所采集到的数据能够被FPGA实时接收并处理,FPGA的各功能模块时钟频率和AD7928 1MHz的采样率应保持一致[6]。本模块设计了一个由时钟脉冲上升沿触发的50分频计数器,通过控制计数器循环计数来实现分频,为FPGA内部模块提供了1MHz的工作时钟;其次,由于AD7928需要20MHz的输入时钟源SCLK,通过调用FPGA内部IP核PLL对50MHZ时钟进行2倍频,再经5分频处理得到20MHz时钟为ADC提供访问器件数据所需的串行时钟以及转换过程的时钟源。

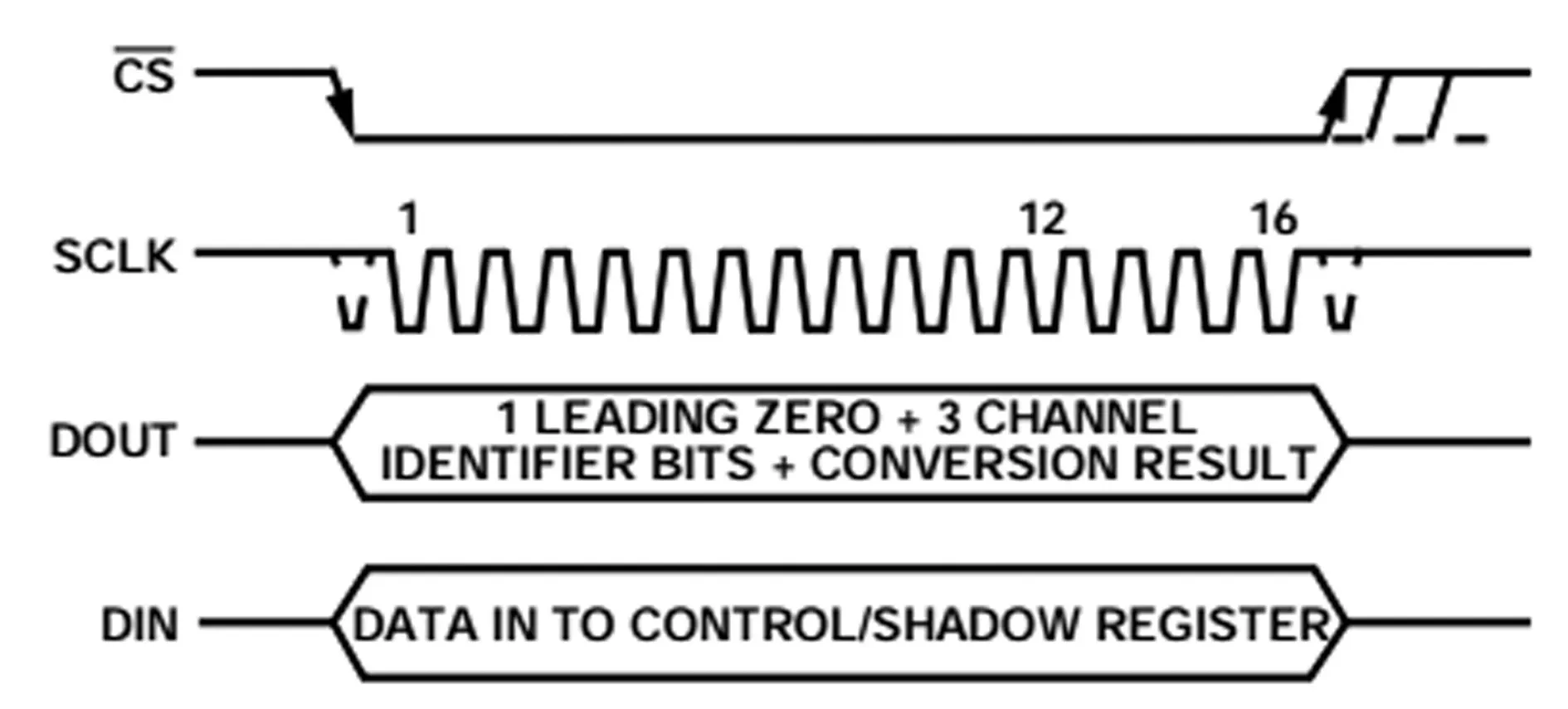

2.3.2 ADC时序控制模块

由FPGA对AD7928进行时序控制,协调FPGA控制A/D采样时序[7],AD7928工作时序如图6所示,A/D在通电后,首先FPGA需对AD7928的控制寄存器进行操作,完成输入通道选择、输入电压范围设置以及输出数据编码格式设置等,由时钟分频模块提供20MHz输入时钟源SCLK,数据在SCLK的下降沿从DIN引脚载入ADC,FPGA在转换和数据采集过程中对和串行时钟信号进行控制,输入信号在的下降沿进行采样,而转换同时在此处启动,无流水线延迟,数据转换一次需要16个周期,转换后的数据从DOUT引脚送入FIFO缓存模块。

图6 AD7928工作时序

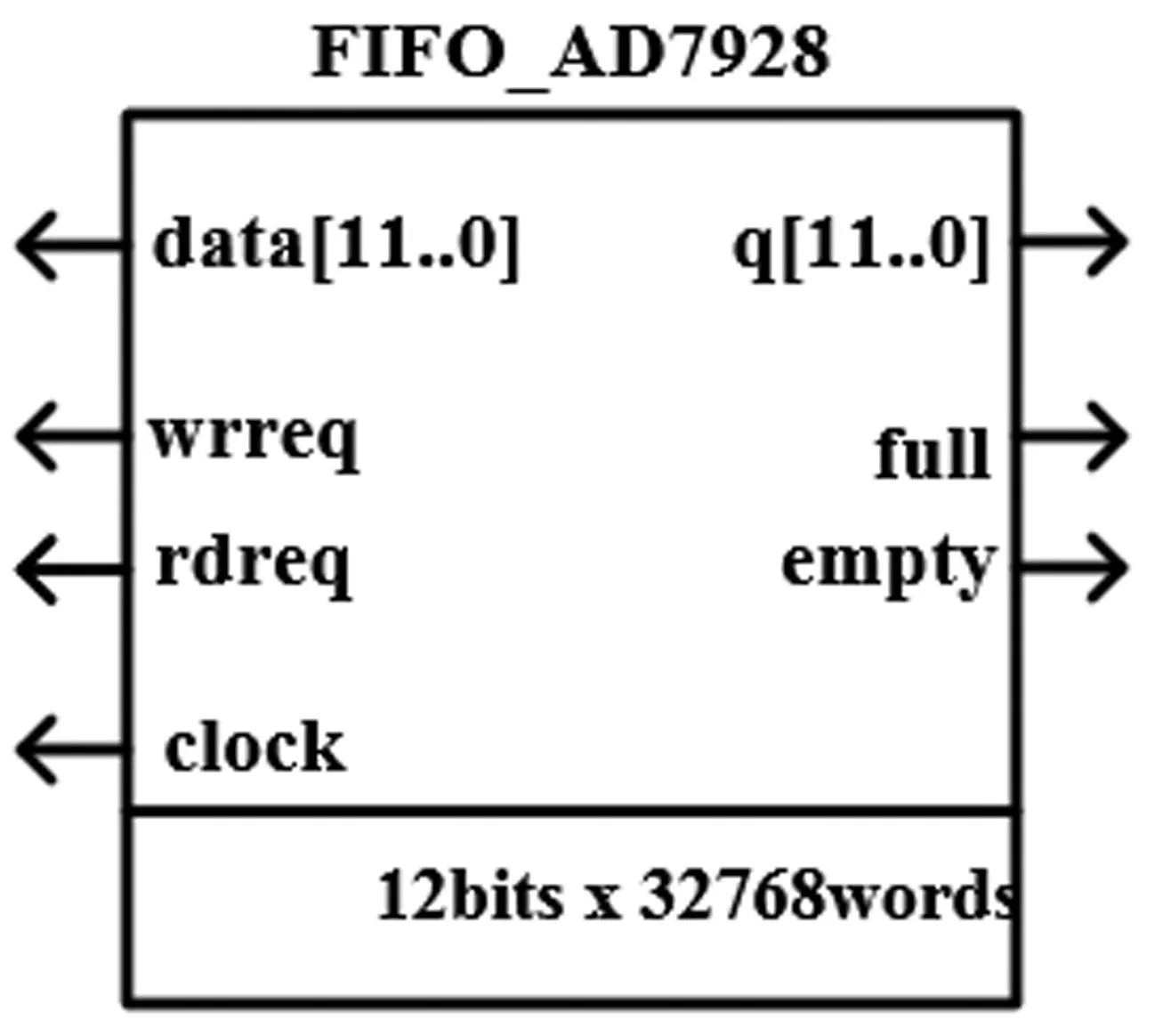

2.3.3 FIFO缓存模块

AD7928每1μs输出一个角膜变形信号,空气脉冲作用下角膜变形信号从产生到结束大概需要25ms,ADC输出约25000个数据量。为防止数据量大引发数据丢失、提高系统工作效率设计了本模块。通过配置FPGA内部的IP核FIFO,设置位数为12,深度为32768的同步FIFO,可满足25ms内连续的角膜变形信号数据流进行缓存,实现对数据先采集后处理的工作模式。图7为FIFO缓存结构,clock是FIFO的写/读时钟,与AD7928采样时钟一致,即为1MHz的工作时钟,由时钟分频模块提供该时钟。data为FIFO输入数据,即AD7928的输出数据。q为FIFO的输出数据,wrreq和rdreq分别为写使能和读使能,通过full/empty(满/空标志)控制数据的写入/读出。将写满的25ms数据送至峰值检测模块,由SDRAM存储模块完成FIFO输出数据的存储。

图7 FIFO缓存结构

2.3.4 峰值检测模块

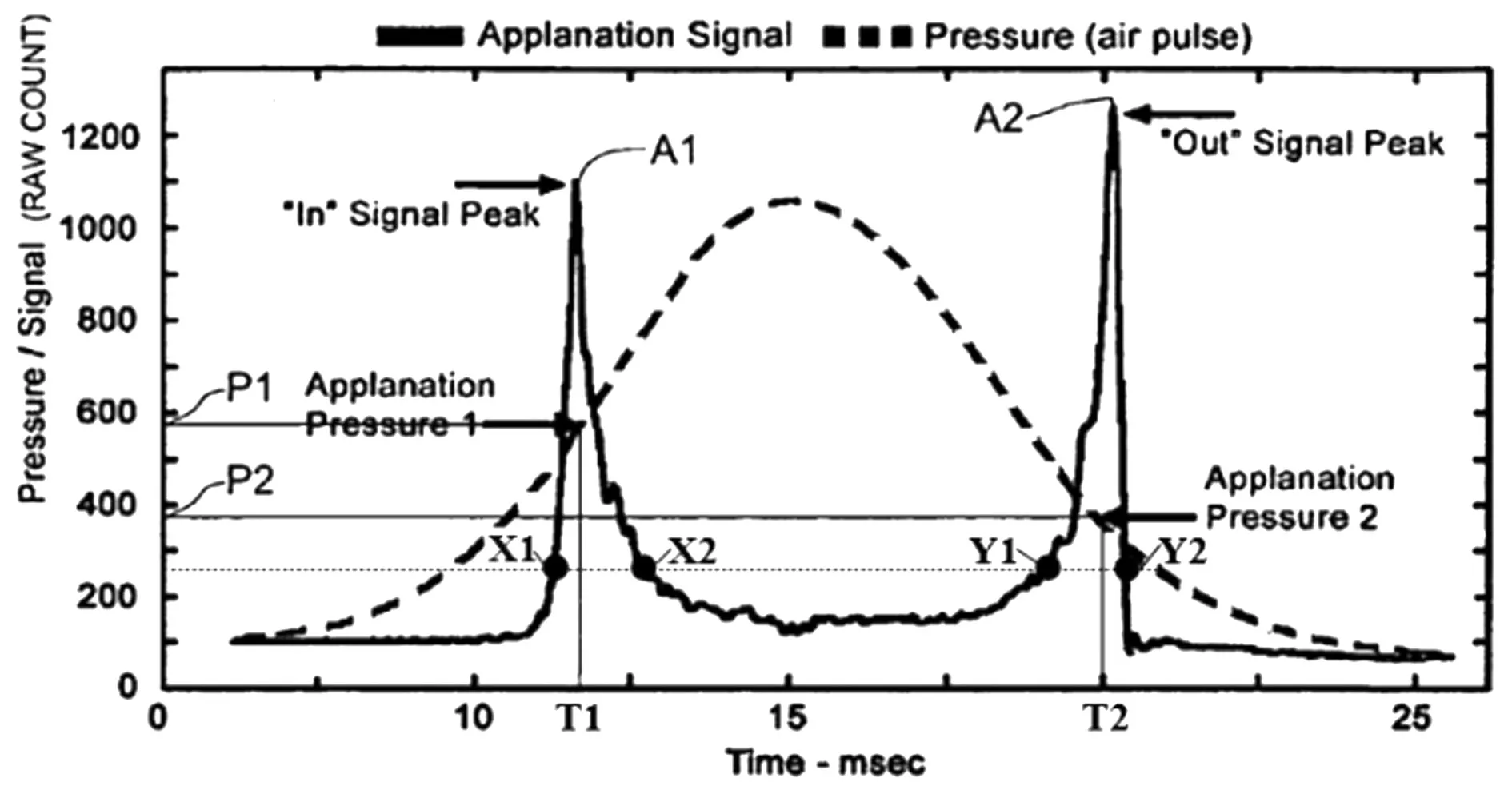

考虑到角膜变形信号在采集过程中会夹杂一定的信号噪声,可能产生“毛刺”或“假峰”影响寻峰精度[8],对FIFO缓存送入的数据通过数字滤波进行预处理,采用异常值判断滤波法,根据相邻两点数据无跳变的理论,比较相邻两次采样值如变化超过阈值,则说明为异常值,通过去除最近一个数据消除尖峰噪声对峰值检测的影响。图8为角膜变形信号峰值,将角膜变形信号和眼压压力信号拟合在同一坐标轴下,A1、A2为两次角膜变形信号的峰值,P1、P2为对应于两次峰值时刻TI、T2的眼压压力信号。如果直接进行寻峰检测数据量较大,而且大部分数据均为冗余数据[9],为减少FPGA处理数据量,提高处理速度,采用阈值比较寻峰算法排除掉离峰值电压较远的低电压浮动。

图8 角膜变形信号峰值

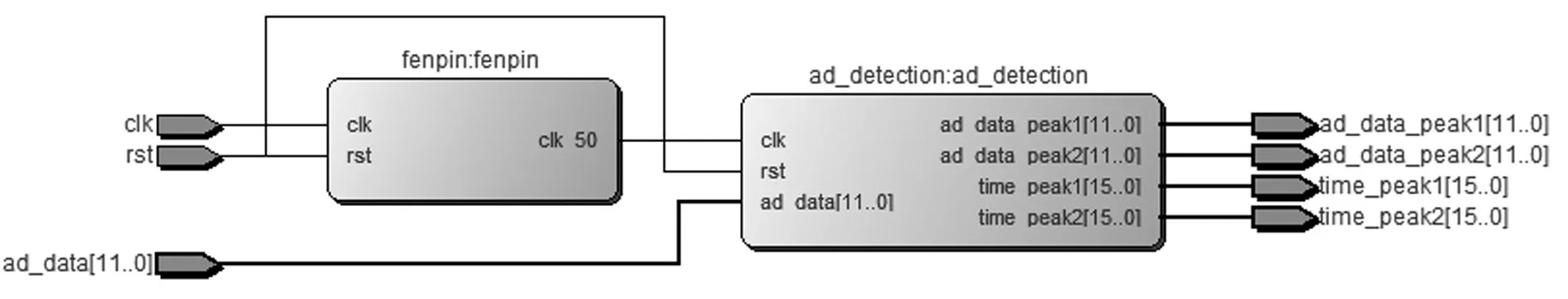

通过Verilog HDL编写状态机来实现峰值检测,图9为RTL峰值检测。在FPGA内部设置两个寄存器,分别存储两次角膜峰值信号。FIFO每1μs送入一个ad_adta,通过计数器对输入信号进行计数。首先对输入信号进行阈值比较,若大于所定阈值X1点的值时(如图7所示),则初始化第一峰值寄存器,进入峰值比较状态并将输入值存入该寄存器。若下个进入的值大于该寄存器值,则将该值更新为寄存器值,否则该寄存器值不变。

图9 RTL峰值检测

依次判断采集的信号值,直到输入信号值小于寄存器值时,判断当前寄存器值是否为有效峰值。如果此后到X2点之前的信号均呈下降状态,则该寄存器值为有效峰值;反之,由于有效峰值幅度较大,通过去掉幅值达不到要求的无效峰值得到ad_data_peak1,并通过计数器提取出峰值时刻time_peak1[10]。状态转移到对第二次峰值的检测,检测机制与第一峰值检测相同,将检测得到ad_data_peak2存入第二峰值寄存器,并得到峰值时刻time_peak2。将得到的角膜峰值时刻值送入SDRAM存储模块内进行存储。

对所获得的角膜峰值时刻进行误差分析,不仅要考虑角膜变形信号测量过程中的高斯噪声误差[11],还要考虑A/D量化误差所带来的影响。设角膜变形真实信号s1(t)叠加高斯噪声z1(t)后为:

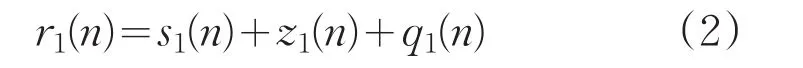

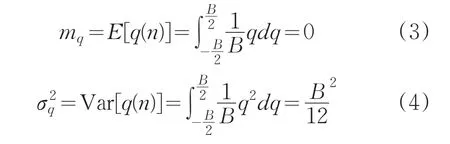

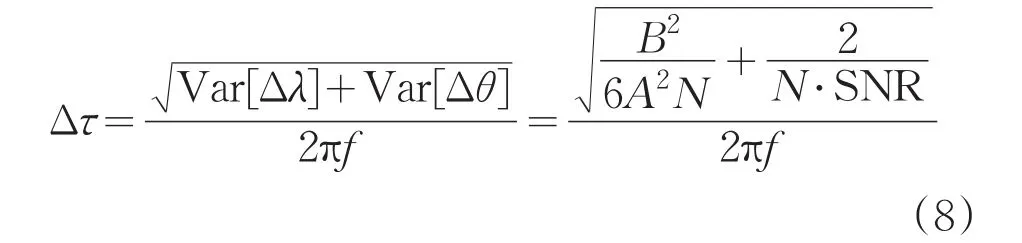

A/D量化误差与高斯噪声不相关,式(1)经A/D量化误差q1(n)叠加后为:

设AD7928位数为b位,量化宽度即为B=2-b,采用舍入处理,舍入量化噪声q(n)的均值与方差分别为:

用Δλ表示角膜变形接收信号r1(n)与角膜变形真实信号s1(n)在量化噪声引起的相位偏移。对s1(t)进行傅里叶变换得S(k)=x(k)+jy(k)。记在最大谱线对应的k为m,Δλ表达式为:

将信号的幅度记为A,由式(5)可以得到相位差的方差为:

记采样次数为N,高斯白噪声背景下角膜变形信号FFT相位差法估计误差的方差的下限为:

峰值时间误差Δτ可表示为:

角膜变形信号f为1MHz,AD7928的位数b=12,采样次数N=3,SNR=15dB时,得到角膜变形信号峰值时刻误差结果为0.157μs,可知角膜变形信号峰值时刻检测误差小于0.2μs。

2.4 SDRAM存储模块

采用Micron公司的32Bit MT48LC4M32B2P-6作为SDRAM存储芯片,SDRAM具有体积小、存储空间大等优点。通过FPGA对SDRAM状态控制器进行配置,SDRAM控制器针对SDRAM的指令操作特点,为SDRAM提供同步命令接口和时序逻辑控制,采用读、写FIFO和读写逻辑控制模块,优化接口封装[12]。SDRAM的每次写操作可将数据存储在指定位置,读操作根据需求读出指定位置的数据,完成角膜变形信号以及角膜峰值时刻的写入/读出以及存储。

3 系统仿真分析

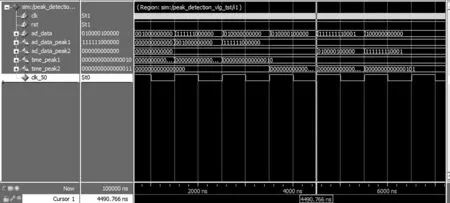

为了验证本系统能够完成对两次峰值信号的提取以及确定两次峰值时刻,使用Modelsim进行了仿真,峰值检测仿真结果如图10所示。其中,clk为外部时钟信号,rst为复位信号,clk_50为时钟分频模块产生的1MHz时钟,ad_adta为FIFO输入信号,ad_data_peak1和ad_data_peak2为两次峰值信号,time_peak1和time_peak2为两次峰值信号对应的峰值时刻。可见系统完成了从ad_data输入信号中提取出两次峰值信号,ad_data_peak1和ad_data_peak2最终输出为两次峰值信号,并由time_peak1和time_peak2输出了两次峰值信号对应的时刻。

图10 峰值检测仿真结果

4 结束语

通过理论分析与仿真验证,基于FPGA实现的角膜变形信号峰值时刻检测系统完成了对两次峰值时刻的检测,对产生25ms左右的角膜变形信号可达到1μs的峰值检测精度,且检测误差小于0.2μs,实现了对角膜变形信号峰值时刻精度较高的检测。与传统峰值时刻检测电路相比,本系统通过FPGA作为主控芯片,不需采用比较器及DAC电路部分,便实现了数据采集与峰值检测,减少了峰值检测硬件电路的设计,在时间精度和采样速率上均有提高,系统运行稳定可靠。