基于FPGA的高速ARINC429数据过滤设计

文/海灏 夏喜龙

1 技术需求

ARINC429规范由美国航空电子工程委员会(Airline Electronic Engineering Commission,AEEC) 制定,美国航空无线电公司(Aeronautical Radio Inc.,ARINC)出版的一种民用飞机机载总线规范。其全称为“数字信息传输系统”(Digital Information Transfer System,DITS),该标准数据资源丰富,数据精度高,在当代航空及其他设备中得到广泛应用。

ARINC429总线是一种串行标准,为面向接口型的单向广播式传输总线,调制方式采用双极型归零三态码方式。

ARINC429总线传输的基本单位是字,每个字由32位组成,1-8位是标号位(LABEL),标记出包括在这个传送字内的信息的类型。

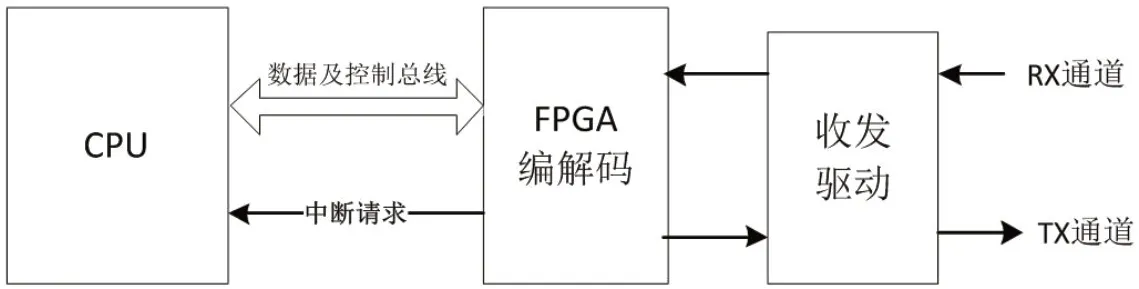

现有传统的ARINC429总线数据接收处理和发送传输的硬件实现方法如图1所示。CPU负责ARINC 429专用协议芯片的工作模式控制、提取接收数据、数据解析及发送数据设置;ARINC429专用协议芯片按照CPU设置将总线串行数据转换为并行数据,将来自CPU的数据进行编码发送;驱动组件主要功能将专用协议芯片的信号与总线之间进行电气隔离及转换;FPGA/CPLD一般用于逻辑控制,为可选项。

此外,还有一些类似的实现方式,将ARINC429总线数据转换功能用FPGA实现,数据处理灵活性及可扩展性上更便于数据交互。

图1:ARINC429总线数据处理传统硬件设计框图

图2:系统总体架构图

现有多种技术实现方法在低速、单LABEL号(每种LABEL对应一种数据类型)接收应用中问题不大,但在高速、多LABEL号特别是相邻数据间隔时间较小的情况下,容易造成数据丢失。此外,由于CPU需要依次接收处理总线数据,包括本机不需要的数据,因此造成处理资源的浪费。

2 设计方案

2.1 总体技术方案

FPGA技术发展迅速、资源丰富、使用方便,具有更大并行度、可定制、可重构等优势。本设计基于FPGA和CPU实现,利用FPGA并行处理、处理速度高的特点,实现硬件过滤、编解码等工作,利用CPU强大的运算能力实现数据解析。本设计系统总体框架如图2所示。

各模块功能如下:

(1)CPU:通过总线控制发射编码的通道、速率及发送信息;控制接收解码的速率、奇偶校验、LABEL号过滤,同时从总线上提取接收数据进行解析,设计选用STM32F746VGT6;

(2)FPGA编解码:按CPU设置进行编解码,进行LABEL硬件过滤,设计选用EP3C120F484I7N;

(3)接收驱动:将标准ARINC429信号转换为3.3VTTL信号,设计选用DEI1046;

(4)发送驱动:将3.3VTTL信号转换为标准ARINC429信号,设计选用4片DEI1070。

目前接收通道及发送通道都设计为4路,可根据需要进一步扩展。每路接收通道可设置为2种LABEL过滤。当有更多LABEL过滤需求时,可将多路合并,最多可过滤8个LABEL。同时也可以按照该架构进一步扩充通道及LABEL过滤,以满足更多需求。

当收到接收数据时:

(1)FPGA按照CPU设置的速率进行译码;

(2)提取译码结果的LABEL进行判断,是否为本通道接收数据,如果是,转入下一步;

(3)将数据存入增加字头、校验后存入FIFO。将数据指示标志写入接收中断状态寄存器,根据CPU设置是否将该标志与中断请求关联。

(4)CPU采用中断或查询方式采集中断状态寄存器状态,当发现有数据请求时,依据优先级读取相应通道信息并进行解析。

当需要发送数据时:

(1)CPU将需要发送的字头、通道、速率、数据内容及校验数据按地址依次发送给FPGA;

(2)FPGA按照设置要求编码并选择相应的通道发送。

2.2 核心单元技术方案

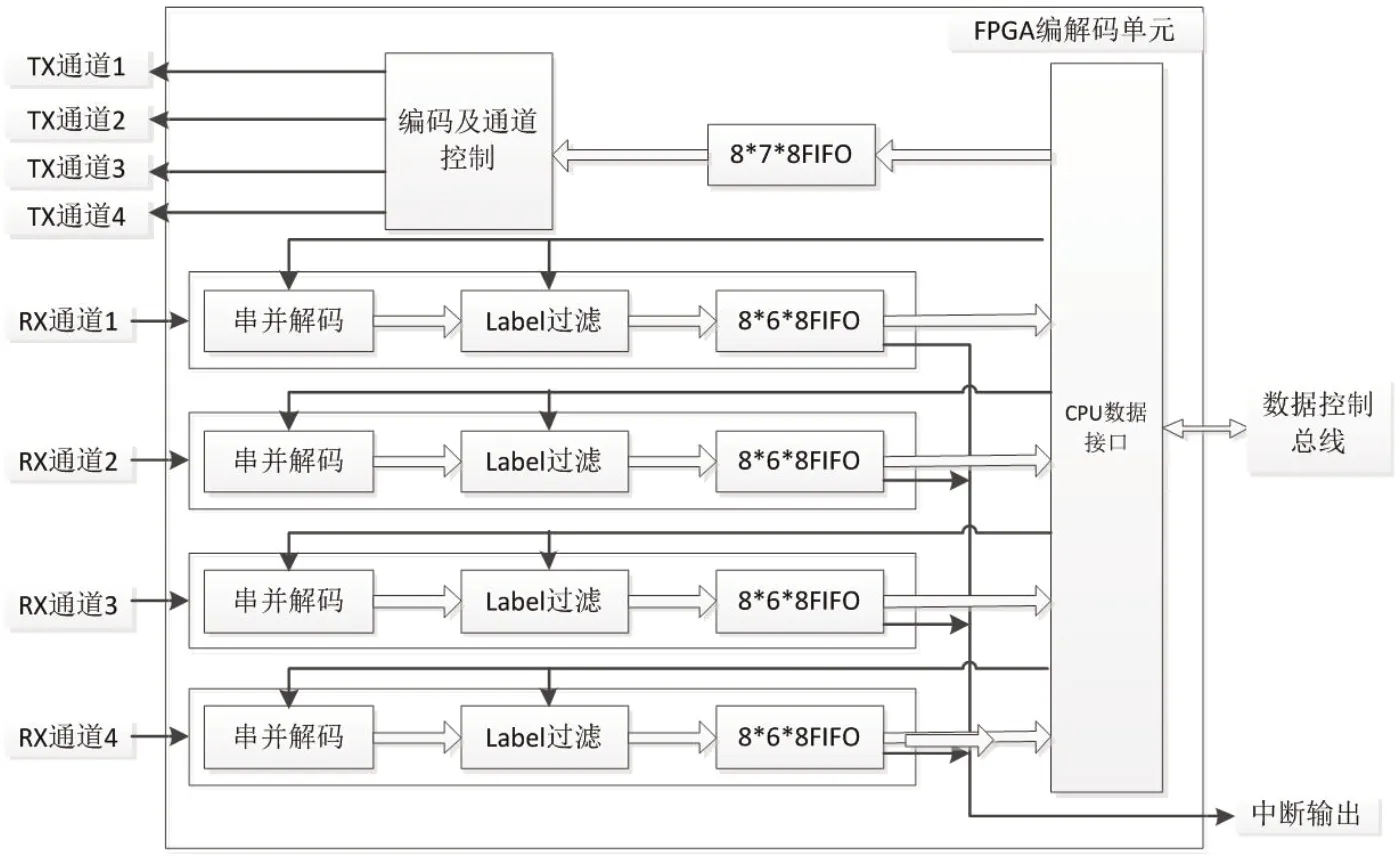

编解码单元为本系统的核心单元,本单元性能对系统性能有着重要的影响。

FPGA编解码单元功能框图如图3所示,共有4个接收通道和4个发射通道。

4个接收通道采用同样的结构,每个通道分为串并解码、LABEL过滤及FIFO缓存部分:

(1)串并解码:将串行数据按照接收速率转化为并行数据;

(2)LABEL过滤:将接收到的数据进行过滤,如果LABEL号匹配,则将数据传递到缓存;

(3)FIFO缓存:将接收数据进行缓存,设计为8级缓存,每级有6个字节,分别包含接收字头、接收数据及接收数据校验。

发射通道由8*7*8FIFO结构及编码及通道控制单元组成:

(1)FIFO缓存:将来自CPU的数据进行缓存,缓存有8级,每级有7个字节,分别包含发送字头、发送速率及通道选择、发送数据(4个字节)及数据校验;

(2)编码及通道控制单元:该单元按照FIFO数据将数据按速率配置及通道选择编码并选择相应通道发送。

3 分析验证

3.1 高速率多种类数据处理过程

本设计方案单个接收通道信号流及转换如图4所示,显示多个ARINC429高速信号依次到达(间隔40us)时,单个接收通道信号流及转换过程。到达的信号含有目标数据(LABEL号为207和244)及非目标数据(LABEL号为203和205),可以看出,经过LABEL过滤单元,滤除了第一组和第三组非目标数据,并且将目标数据缓存在FIFO中。

3.2 处理性能分析

按照ARINC429标准,计算参数设定如下:

(1)波特率:100K BPS;

(2)数据刷新率(以“A”表示):100ms=0.1s;

(3)数据间隔:4个时钟周期/40us;

(4)接收目标数据(以“B”表示):2个;

(5)单周期数据个数:≥8个;

(6)通道数目(以“C”表示):1个。

由于采用了LABEL过滤及接收FIFO技术,计算时可不考虑波特率、数据间隔、单周期数据个数。

CPU应在FIFO满前将数据读出,并处理完毕,则CPU处理速度要求由A、B、C及缓存级别决定(设计值为8),关系如下:

CPU处理速度=B*C/(A*8)=2*1/(0.1*8)=2.5次/S=400ms

在传统技术条件下,对CPU的处理要求的影响参数为波特率及数据间隔,CPU处理速度要求为36个时钟周期=360us。

处理要求差别为=400ms/360us=1111倍。

3.3 系统验证

该设计方案已应用于某型机载系统,通过使用该设计技术处理高速ARINC429高度数据,消除了原有的高度码跳变的故障,提升了系统性能。

图3:FPGA编解码单元功能框图

图4:单个接收通道信号流及转换示意图

4 结语

本文详述了一种基于FPGA的高速ARINC429数据处理方法,通过使用FPGA硬件过滤方法,结合FIFO结构,有效的降低了CPU负荷,消除了丢包现象,经计算,综合性能提升约1111倍。

该方法已成功应用至某型机载平台,提升了ARINC429接收性能,该方法可推广应用在高速ARINC429通讯的相关平台中。