基于FPGA的单周期MIPS处理器设计与实现

王雨桐 刘威 李林瑛

摘要: FPGA技术的迅速发展,其使的应用领域从最初的通讯扩展到诸多航空,医疗等诸多领域。Logisim作为一个数字逻辑电路的设计与仿真软件,具有开源免费、可二次开发、免安装、使用简单、结果直观等优点。国外已有院校利用Logisim软件完成了CPU的设计,但国内缺乏此方面的实践经验。本文将阐述如何利用Logisim设计数据通路并与Verilog结合对单周期CPU进行FPGA设计。

关键词: FPGA;MIPS CPU;单周期CPU;Verilog;计算机组成原理

中图分类号:TP332 文献标识码:A

文章编号:1009-3044(2019)17-0278-04

开放科学(资源服务)标识码(OSID):

Abstract: With its rapid development, the use of the FPGA technology has been extended from the communication industry to many other fields such as aviation and medical treatment. As a design and simulation software, Logisim has the advantages in secondary development, needless to installation, open source, most importantly, easy to use for a beginner. Compared to that of the foreign developed countries, the experience of designing a single CPU on Logisim in China is limited. This project will demonstrate how to use Logisim to design the data path of a single MIPS CPU and realize it via Verilog on Vivado.

Key words: FPGA; MIPS CPU; single MIPS CPU; Verilog; principles of computer composition

1 引言

本项目采用Logisim仿真平台对单周期MipsCPU进行设计并整合形成MIPS CPU数据通路图,构建数字电路系统,通过Vivado平台利用Verilog硬件描述语言对CPU进行实现,最后进行仿真。

2 Logisim实现数据通路设计

2.1 Logisim简介

LogiSim是一款开源的数字电路仿真软件。通过该软件,用户可以使用其提供的多种元件图仿真设计电路,并通过输入真值表自动生成电路,利用隧道对电路进行简化,同时可以对元件进行参数设定,并将电路进行封装,方便多个模块之间的联合。该软件还提供数据通路的错误检测,将出现的错误显示为设定的颜色。

2.2 基于Logisim的ALU设计

2.2.1 32位加法器

利用logisim构建加法器,需在构建数据通路之前,首先确定该加法器所实现的功能。本项目所构建的32位加法器的功能为:算术加、减、乘、除,逻辑与、或、非、異或运算,逻辑左移、逻辑右移,算术右移运算,支持常用程序状态标志(有符号溢出OF、无符号溢出CF,结果相等Equal)。

对于不同功能码,ALU将实现不同功能,功能码通过引脚ALU_OP传输。

ALU内的基本加法单元是:一位全加器,实现对3个一位的二进制数相加(操作数1,操作数2及进位),取得输出值和进位。

在Logisim输入真值表得到一位全加器进位模块。数据通路如图1。

加法模块符号位溢出的判断,分为有符号情况OF及无符号情况UOF。在UOF情况下,只需对两个输入值与结果值的分别进行比较。如果有至少一个输入值大于结果则必然存在溢出,因此可以用两个比较器将输出结果连接到一个与门上,输出的UOF 信号即为是否存在无符号溢出。在OF情况下,需单独设计一个“加法有符号溢出判断”单元。输入端X,Y表示两个输入值的最高位,S表示结果的最高位(此处利用分离器提前将三个值的最高位分离出再输入进判断模块)。

在Logisim输入逻辑真值表得到加法有符号溢出判断单元,进行封装后即可设计整体的加法模块。

整体的ADD加法模块数据通路如图5。

2.2.2 逻辑左移、逻辑右移和算术右移模块

Logisim自带的三种模块可实现ALU的逻辑左移、逻辑右移和算术右移功能。

三种位移模块的数据通路基本相同。以逻辑左移模块为例,该模块包含两个位宽为32位的输入端,其中X输入端为数据输入端,Y输入端为移位输入端。决定X引脚输入数据的移动位数时,由于X,Y输入引脚的数据位宽均为32位,因此通过分离器取Y引脚的低五位即可。

右移模块设计时,要注意将移位器的移位类型选择为所需的逻辑型或算术型。

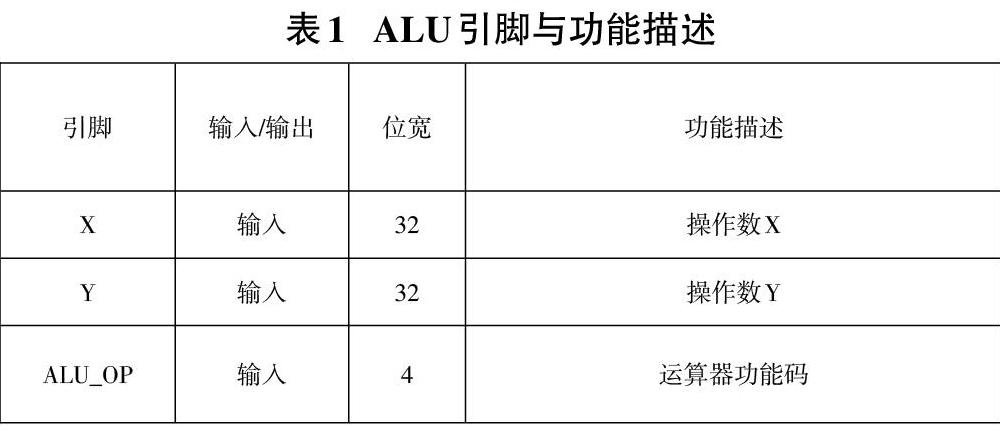

2.2.3 SUB减法模块

本模块利用之前设计好的32位加法器,对减数进行取补码操作,取补之后的减数与被减数相加得到结果。该模块同样需要判断有符号溢出和无符号溢出情况,原理和加法模块的溢出判断基本相同,在无符号溢出的判断直接比较被减数和结果大小即可判断是否溢出,有符号的判断需要利用之前设计的“加法器有符号溢出判断”模块。数据通路如图6。

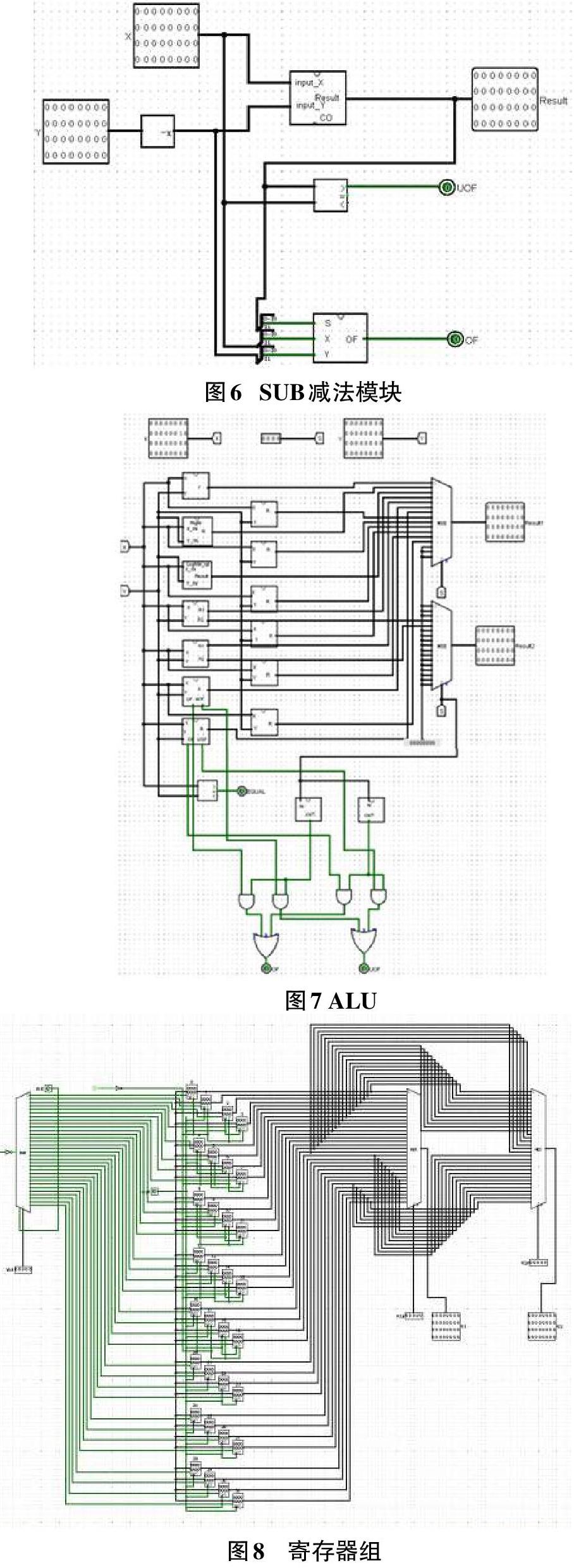

ALU运算器包含12个功能模块,数据通路功能码定为四位二进制。ALU的输出除了结果外还有OF和UOF的溢位判断和相等判断。在溢位判断中,分别建立加法溢位模块和减法溢位模块,通过检测ALU的操作码是加法还是减法的操作码后输出一个真值,与相应的加法模块或减法模块的溢出信号取与后输出,保证溢出信号的准确。

加法溢位判断模块和减法溢位判断模块的数据通路仅针对特定的操作码,不同的ALU加减法功能码不同,连接方式也不同。利用logisim的真值表可自动建立对应模块的电路。

ALU 整体数据通路图如图7所示:

2.3 寄存器组设计

考虑到MIPS CPU的指令结构中目的寄存器地址仅为5位,一组由32个32位寄存器单元组成的寄存器组(零号寄存器值要始终为零)即可满足功能要求。寄存器组中的每个寄存器单元(Logisim提供)包括五个引脚:数据输入端(当时钟触发时更新寄存器数据0),时钟端,使能端(当为0时忽略时钟输入),清空端(当为1时异步清空寄存器单元的值),输出端(输出寄存器单元的值)。各寄存器单元通过一个解复用器和两个数据选择器组合成寄存器组。解复用器的输入端输入常量1,并在使能端接入写使能WE信号,在选择引脚接入5位二进制用于选择寄存器单元。最后用两个数据选择器对输出数据的寄存器单元进行选择并输出数据。

寄存器组的数据通路图如图8所示。

2.4 单周期CPU数据通路整体设计

单周期MIPSCPU的指令类型分为R, I, J,三种指令,OP操作码字段为零的是R型指令,通过最后6个bit的功能码可以确定指令功能,其余指令直接通过OP的值可以唯一确定指令功能,因此MIPS的指令解析非常简洁。

在取指令的过程中,以PC为地址访问内存,将取出的指令字放入内存,由于要在一个时钟周期内完成整个指令的取值取操作数执行的过程,所以不能设置地址缓冲寄存器、数据缓冲寄存器以及指令寄存器,而是直接用PC访问指令存储器。而指令进行执行的过程中,取操作数和取指令都需要访问存储器,因此将指令存储器和数据存储器分开设计以防止器件的征用。同理为防止运算器的征用,还需要将PC的地址接入一个单独的加法器进行PC的累加运算。

当PC的指令地址输出后,通过一个分析模块(分离器即可)将32为的地址分离出RS,RT,RD,OP,FUNT,IMMEDIATE等字段,传输至寄存器堆及控制器的相应各个引脚,16位立即数通过位扩展模块进行扩展并输入至ALU,寄存器堆的数据输出后传输至ALU, ALU根据控制器输出的ALUop引脚的相应操作码进行计算并输出至数据存储器。

3 基于Verilog的单周期CPU设计

利用logisim设计单周期CPU的通路图可更直观了解CPU各个部件引脚之间的关系及信号的传递,完成数据通路设计后,即可进行基于Verilog的处理器设计。本实验利用VIVADO进行设计与modelsim仿真。

根据数据通路,分别设计各个子模块及CPU顶层模块。最后编写testbench文件进行单条指令仿真。

在进行FPGA下板时,由于自行编辑的指令存储器中的initial指令不可综合,因此需使用coe文件进行内存初始化。本实验用到开发板上的16个开关,并用16位LED进行输出显示,下载比特流文件至开发板后就可以进行CPU运算操作了。

4 结语

本项目利用FPGA设计了单周期MIPS处理器,采用Logisim仿真平臺对处理器设计方案进行验证,并扩展构建了相应的数字电路系统。该处理器支持自动和单步运行方式,能正确地执行存放在主存的程序功能,对主要的数据流和控制流通过LED和数码管进行实时显示,方便监控和调试。

本课题除电路设计方面的创新外,还是一项包含教学、科研和项目开发一体化的能力培训过程。教学方面体现能够综合应用《计算机组成原理》和《数字逻辑》中门电路、处理器、存储器、指令系统和CPU的知识,同时能培养学生对科研及项目研发过程的了解及熟悉。

参考文献:

[1] 王志英,周兴社,袁春风,等. 计算机专业学生系统能力培养和系统课程体系设置研究[J]. 计算机教育,2013(9):1-6.

[2] 吴继明,曾碧卿.一种高效的CPU设计方法及其在计算机组成原理课程中应用[J]. 实验室研究与探索,2018(9):147-153.

[3] 杨杨.基于FPGA的单周期CPU设计与实现[J].软件开发与设计,2011(22):25-28.

[4] 武杰,乔密,张俊杰. MIPS系统中北桥的FPGA设计[J].小型微型计算机系统,2004,25(11):2028-2031.

[5] 邹志斌.基于MIPS指令集的RISC微处理器控制模块的设计与实现[D].武汉:华中科技大学,2008.

[6] 胡世昌.用logisim改革数字电路实验[J] 沈阳师范大学学报(自然科学版)2015,33(2):3010-304.

[7] 吴容海.Logisim在“计算机组成原理”教学中的应用实践[J] 大理学院学报,2016,1(12):96-100.

[8] Burch C.Logisim: a graphical system for logic circuit design and simulation[J].Journal on Educational Resources in Computing( JERIC) ,2002,2(1):5-16.

【通联编辑:王力】