基于eMMC的64路无线数据存储系统设计

宋师军,吴宏斌,王存宝

(1.北京航天长征飞行器研究所,北京 100076;2.山西北方机械制造有限责任公司,山西 太原 030009)

0 引 言

随着无线通信技术的发展,无线传感网络因具有低功耗、安全性能高、灵活性好等优势被广泛应用在工业、日常家居控制等方面[1].其中ZigBee无线通信技术具有成本低、稳定性能好、可靠性高等特点被大量用于安防设备检测与控制、环境监测等方面[2],但该技术一般适用于短距离、传输数据量较小的网络[3],对接收数据量大的复杂环境,ZigBee无线通信受到了限制.针对ZigBee无线通信存在的弊端,设计了一种基于eMMC的64路无线数据存储系统,采用eMMC作为存储器件,具有传输速度快、操作简单、管理容易等优势[4],可实现设备对目标区域的长时间、大范围监测工作.设计64路数据采集,可应用于复杂的环境,实现对目标区域多影响因素的信号检测.该系统以实测所得的速变数据作为研究对象,采用Z-stack协议栈实现无线数据的传输,以现场可编程门阵列(Field Programmable Gate Array, FPGA)为主控模块实现终端节点电路的设计,对产生的多路数据进行编帧处理并存储至eMMC器件,可实现无线传感器网络终端节点大数据量的采集.结果表明该系统操作简单、工作稳定且可靠性高,具有广泛应用前景.

1 系统总体设计

本系统设计的无线传感网络节点电路主要由FPGA主控模块、ADC转换电路、eMMC存储电路、CC2530无线收发模块、电源管理模块等组成.系统框图如图 1 所示.

图 1 系统总体设计框图Fig.1 System design block diagram

整个电路的工作过程如下:在FPGA的控制下通过模拟多路复用器配合AD转换器完成64路模拟信号的采集,将数据传输给FPGA,由FPGA对数据进行FIFO缓存和编帧操作,通过控制eMMC完成对64路数据的存储,若外界发送请求信号有效,通过FPGA控制将eMMC中的数据读出到读FIFO中,最终将数据经过串口与CC2350无线收发模块进行通信,该模块通过Z-stack协议栈[5]完成芯片的配置与组网操作[6].

2 系统硬件电路设计

2.1 ADC数据采集模块

数据采集模块由模拟开关及ADC转换器组成,系统选用4片16通道模拟多路复用器ADG706,实现64路模拟信号的地址切换.该芯片具有导通电阻小、切换速度快等优点,能够满足系统精度的设计要求.ADC芯片选用AD7904,该器件采样率可达1 Msps,采样位数为8 bit,4通道的ADC芯片具有体积小,功耗低等优点,只需进行简单的配置便能满足不同的电路设计.ADC芯片控制寄存器设置为4通道循环采集工作模式,二进制格式编码.选用AD780芯片为AD7904提供2.5 V的基准电压源,保证模数转换的正确性.ADC转换芯片的4个通道分别接一片ADG706的输出端,通过FPGA对模拟开关地址选通.

系统正常工作时,FPGA通过对AD模数转换芯片设定和对模拟开关地址的切换控制,使其完成64路对应地址下的调理电路后电压信号的循环采集,将对应通道下的信号传至ADC进行采集、量化,并送至FPGA进行编帧处理.

2.2 eMMC电路设计

系统选用MTFC64GAKAEEY作为存储单元,容量为64 GB,芯片符合eMMC5.0[7]标准,最高支持HS400速度模式[8],该芯片的接口标准主要有时钟线CLK、复位线RST、命令线CMD、数据线DAT0-7、电源线VCC和VCCQ、地线VSS和VSSQ.其中命令线CMD为双向传输线,负责传输主机发往eMMC器件的命令以及反馈eMMC响应;复位线RST为eMMC的硬复位线;数据线DAT为双向端口,完成传输主机写入的eMMC的数据或读出eMMC的数据,在HS400模式下,理论写入峰值为400 MB/s,工程中持续写速率为100 MB/s.图 2 为单片eMMC芯片与FPGA的详细电路连接图.

图 2 eMMC存储模块电路Fig.2 eMMC memory module circuit

2.3 无线数据发送模块

无线发送模块主要实现无线数字化传感网络节点之间的数据传递,该模块包括终端设备发送设计、路由器节点设计及协调器节点设计.采用CC2530为核心作为传感节点,器件支持Z-stack协议,该ZigBee协议具有更好的交互操作性和节点密度管理、支持网状网络、低功耗且具有较高的安全可靠性,使得节点通信距离更远,组网性能稳定[9-10].该ZigBee模块通过串口完成与FPGA的数据交互,通过配置将其设置为终端节点数据发送模式,其与FPGA的硬件连接图如图 3 所示.

图 3 无线数据发送模块电路Fig.3 Wireless data transmitting module circuit

路由器节点负责完成设备终端节点数据的中转传输,使数据准确传输至协调器.协调器则负责将前端数据传输给上位机,该部分同样通过串口完成传输,波特率为115 200 bps.系统采用蛇形天线的方式保证ZigBee网络数据传输的准确性.

3 系统软件设计

3.1 信号的采集与处理

该模块主要负责模拟电路的时序电压信号采样处理与对应通道的数据判断,以便后续的数据编帧操作.具体工作过程如图 4 所示:系统准确开始工作,FPGA通过SPI总线对AD7904内部控制寄存器进行数据参数配置,本系统配置AD的工作模式为全功率模式,采用循环采集的方式[11],采集电压范围为0~2.5 V,使AD转换器不间断工作.然后进入等待触发状态,系统触发有效后,通过FPGA控制ADG706的地址线决定对应通道的电压时序信号传送给AD转换器,以便完成数据的采样、传输工作.

图 4 程序流程图Fig.4 Program flow chart

FPGA接收并处理ADC转换的64路时序电压数据,将采集到的数据发送至信号选择判断模块,并对数据进行编帧处理,将数据送至前端写FIFO,该FIFO输入数据位宽为8 bits,输出数据也为8 bits,FIFO深度为8 KB.

3.2 eMMC数据传输逻辑设计

根据JEDEC协议[12]要求,该eMMC器件应先进行初始化配置,分两部分完成,首先完成eMMC芯片的识别、地址的分配以及总线测试,其次完成工作模式的配置及HS400工作模式的采样调谐操作.然后系统对eMMC设备进行擦除操作,通过相应的命令完成对擦除起始地址、结束地址的设置,通过命令触发启动擦除操作至完成擦除,发出擦除完成信号.FPGA接收到擦除完成信号后,等待前端写FIFO传出的半满标志位有效,当标志位有效时,即外部写使能有效,启动eMMC数据写操作.FPGA首先发送相应的命令设置写块长度,本系统块长度为512字节,根据数据量的大小,发送数据写块数命令,然后发送命令设置数据写起始地址,等待响应正确的反馈信号有效,开始写操作并进行单块写完成的CRC16校验,以保证数据的正确性,同时FPGA可通过查询命令检测eMMC的编程状态,等待编程完成.

FPGA检测无线模块数据的发送请求信号,该信号有效时,可将eMMC数据根据读命令控制流程将数据发送至CC2530,进而通过无线网络发送至上位机进行数据分析处理.FPGA接收数据发送信号后,发送数据读命令等待eMMC正确响应,一方面eMMC通过CMD线响应FPGA发出的命令.FPGA发送命令设置一次读的块数,开始进行读操作,并发送读数据的读取地址.另一方面将数据块(含CRC16)由数据线DAT0-7传输给FPGA,直到数据传输完成,同时FPGA将数据进行校验比对,校验无误后,开始进行下一块的读取操作,FPGA将读取的数据进行组包操作,并发送至读FIFO进行数据缓存,等待半满标志有效后,控制数据通过串口传输至ZigBee控制发送模块,完成数据传输.

3.3 无线发送模块设计

为防止数据的冗余,FPGA设置的波特率为115 200 bps,通过ZigBee芯片CC2530上的UART0接收数据.同时为了使CC2530成功组网,实现网络通讯,使用Z-stack协议栈实现ZigBee网络开发,该协议栈具有半开源、开发简单、使用范围广的优势,主要完成对APP层、HAL层、MAC层(介质访问)、MT层、NWK层(网络层)、ZDO(对象层)的开发.

为实现无线网络组网,需要分别对协调器、路由器和终端节点设备进行构建.协调器负责网络的侦听以便其它节点的加入,协调器网络层给新节点分配地址,以对不同节点进行识别.由于本系统的无线传感网络为拓扑结构网状,故需要路由器节点完成网络搭建,路由器父节点为协调器,当路由器发送入网信号给父节点时,父节点发送连接成功的响应并分配地址给新加入的路由器.终端设备节点加入无线网络操作类似于路由器入网过程,以子节点的形式存在.终端节点在上电初始化后,搜寻并加入相应网络,负责将FPGA控制传输过来的数据通过无线网发送出去,路由器通过无线网接收终端节点发送过来的数据,同时将数据通过无线网络发送给协调器,协调器在接收数据之前先进行初始化,然后处于侦听状态,当有节点通过网络向协调器发送数据时,会触发协调器中的信息接收指令,随后协调器调用数据发送函数将接收到的数据通过串口发送至上位机进行后续分析.

4 系统测试及验证

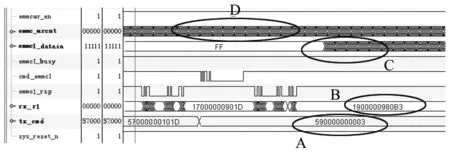

4.1 eMMC数据读写验证

首先进行数据写调试,调试结果波形如图 5 所示.标号A为FPGA发送的写命令,标号B表示eMMC接收响应正确,数据进入传输状态,标号C表示接收的递增数据,标号D为定义的32 bit 的时钟计数器,记录写完成所用的周期数,最后可计算得出在50 MHz时钟下的eMMC的数据写速度为20 MB/s.

图 5 eMMC数据写操作波形图Fig.5 eMMC data writing operation waveform

数据读测试波形结果如图 6 所示.标号C脉冲上升沿表示eMMC读使能有效,标号A表示设置数据一次读取块数,标号B表示读命令响应正确,标号D表示记录读命令发送至读完成所用的时钟周期数,经计算,一次读数据量为8 KB,时钟为50 MHz时,读速度可达24.07 MB/s,满足系统前端的带宽要求.

图 6 eMMC数据读操作波形图Fig.6 eMMC data read operation waveform

4.2 无线发送模块测试

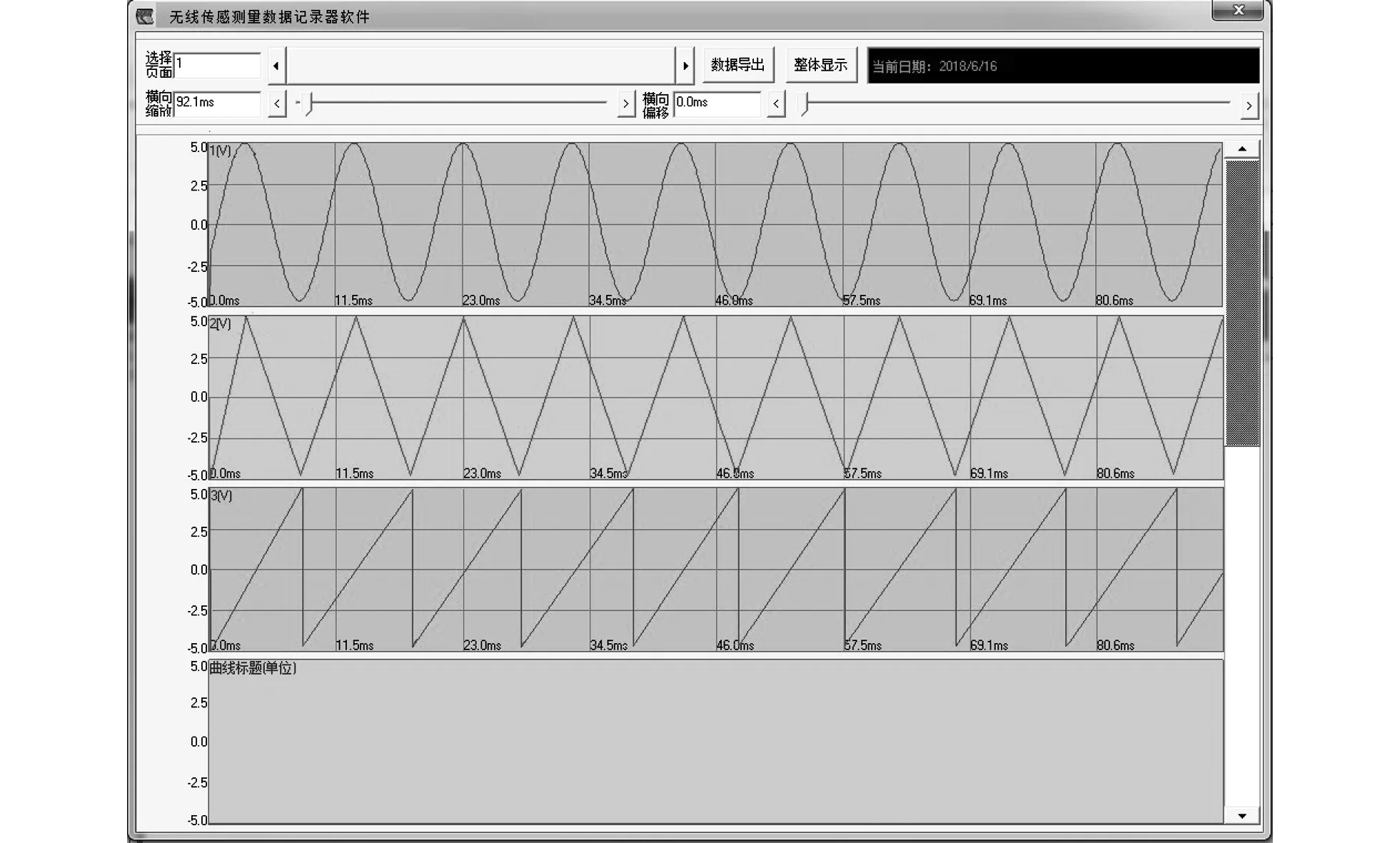

测试信号通过信号发生器产生,为了方便测试结果的分析,各路数据分别采用不同的波形,第一路数据为正弦波数据,第二路数据为锯齿波数据,第三路数据为三角波数据,波形周期为10 ms,幅值为5 V.

上位机发送指令给串口及协调器节点,经路由器中继传输给终端设备,终端节点将接收到的指令码通过CC2530上的相应串口发送至FPGA.FPGA通过对模拟开关相应地址的选通及AD转换器片选信号拉低,将通过调理电路的外界信号由ADC转换成数字信号并传输给FPGA.FPGA对采样量化后的数据进行编帧处理,传输至后端eMMC器件存储,一旦eMMC器件接收到读命令有效信号,在FPGA及时钟控制下将数据传输给CC2530无线发送模块,该发送模块在与路由器、协调器成功组网的前提下,将数据通过无线网络传输至协调器,再经由相应的串口发送给上位机,通过上位机软件对各节点数据进行分离与还原,得到相应波形如图 7 所示.可以看出,还原出来的信号波形稳定,无毛刺,波形周期为9.8 ms,幅值为5 V,说明本系统具有可靠的传输性能.

图 7 上位机波形Fig.7 Upper computer waveform

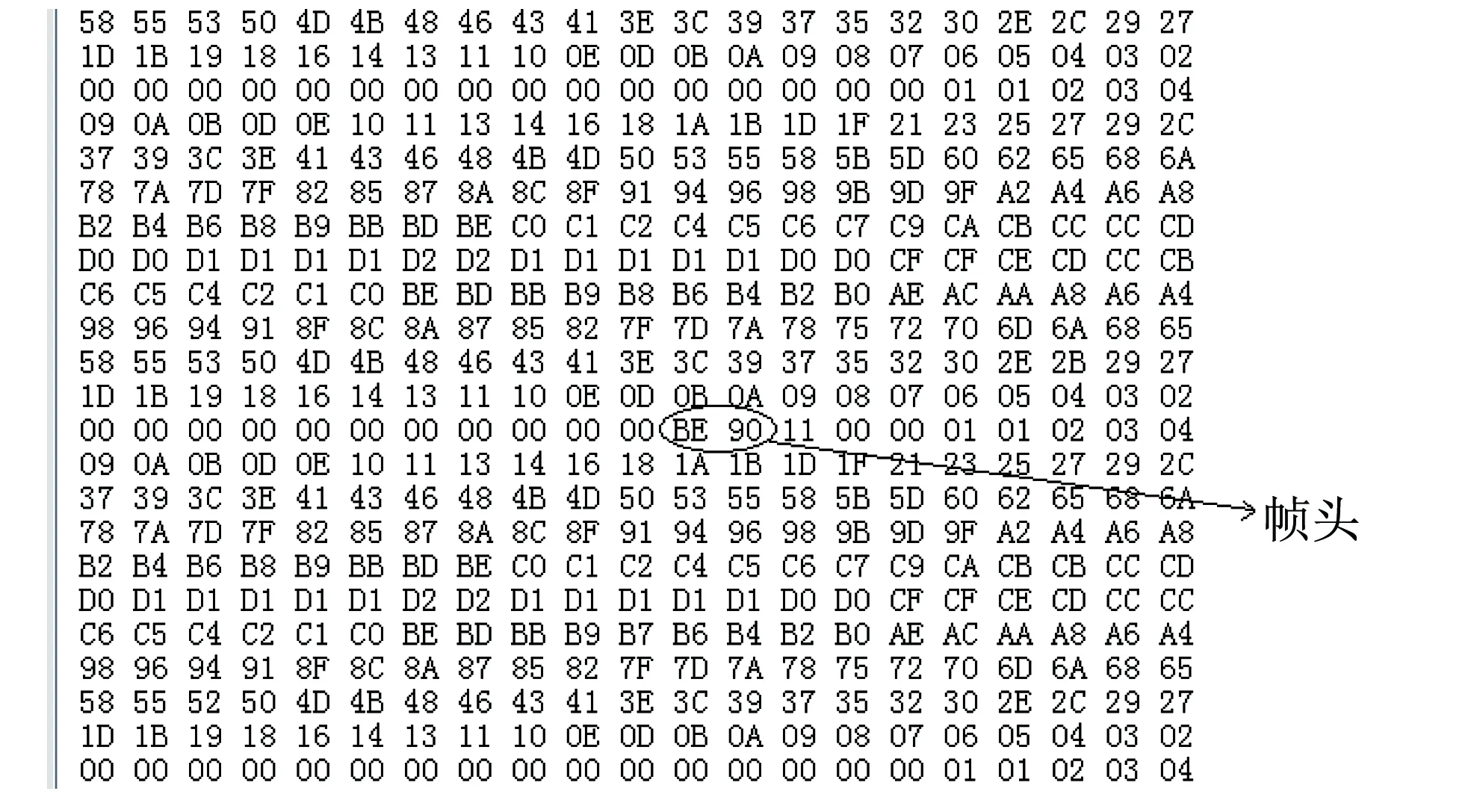

通过超级编辑器读取的数据如图 8 所示,经分析,数据帧格式正确,表明系统功能的可靠性.

图 8 上位机数据Fig.8 Upper computer data

5 结 论

根据特定的应用背景及工程需要,提出了一种基于eMMC的64路无线数据存储系统的设计,并通过在线逻辑分析仪对eMMC的数据传输单元进行调试验证,对前端输入信号进行回读测试.结果表明,eMMC的命令传输与读写速度满足系统设定要求,采用HS400的工作模式能够实现更高的数据带宽要求,同时通过上位机测试表明信号脉冲电压误差在0.5%范围内,达到了设计指标,在很大程度上提高了无线收发系统的可靠性.