IC版图闩锁预防

贺雪群

摘要:在版图设计当中,latch-up闩锁是比较常见的现象。电路设计上有可能自然形成,但版图设计中更容易形成这种结构。除了普通情况下形成的latch-up结构,我们还有可能碰到比较特殊的情况,比如管子的SUB为衬切的情况,这种情况下稍有不慎就会形成latch-up闩锁。

关键词:衬切;latch-up;衬切管

中图分类号:TN4 文献标识码:A 文章编号:1007-9416(2019)03-0109-01

1 普通情况下预防闩锁

在版图设计当中,闩锁是比较常见的现象。如图1所示,两个普通的CMOS管子的扩散区相互之间形成了寄生的VPNP和LNPN,它们与寄生电阻、构成了图1(B)中的结构。在非正常情况下,如果某一个寄生管开启,比如Q1,则流过Q1的电流会开启Q2,它们相互之间提供基极电流,并在Q1、Q2的放大倍数的情况下维持这个过程,直至切断电源。

一般情况下,我们可以通过以下几种方法来防止latch-up现象的发生:

(1)PMOS的SUB是确定的情况下,可以通过增大剖面图中S1、S2的值来降低LNPN的β,因为VPNP的β一般来说是固定的。

(2)在MOS周围的TAP多打孔,以减小Rn-和Rp-,这样VPNP和LNPN的Vbe结基本上处于短接的状态,BJT不能开启。

2 管子为衬切的时候预防闩锁

有时候,电路会碰到PMOS的SUB是衬切的情况,如图2。

在衬切的瞬间,电路上存在电源掉零的情况,对应latch-up结构中的VPNP的B会掉到零,那么VPNP的BE结会开启,VPNP开始工作,如果在画衬切PMOS的DNW中画有NMOS,那么就会导致latch-up结构开始工作,这个是我们不希望出现的。

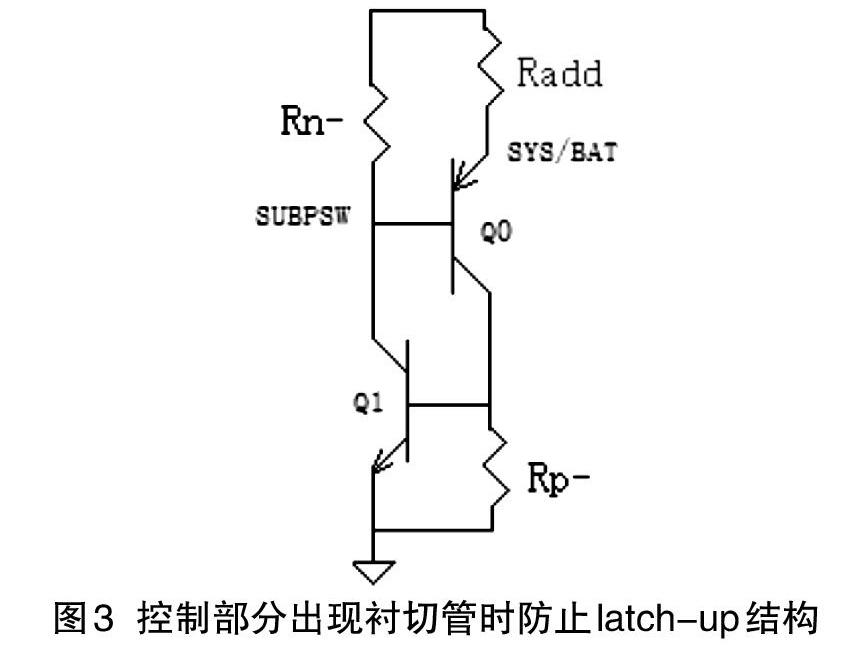

衬切的情况一般出现在功率部分,少数在控制部分也有。在功率管部分,除了要做到前面提到的普通情况下的预防latch-up措施,还要把衬切的管子PMOS单独画在一个DNW中,如图2所示。这种情况下,在电源掉零的情况下,VPNP不可避免的开启,但抬高的也只是P-的电位,从而破坏了latch-up结构。在控制部分,如果出现了衬切的管子,单独画在一个DNW中有点奢侈,可以通过改动电路,在衬切管的S端与PIN之间加一个电阻,起到限流的作用,以减小Q0的,管子Q0更难开启,如图3所示。

参考文献

[1] (美)黑斯廷斯.《模擬电路版图的艺术》[J].电子工业出版社,2007(04):145.

IC Layout Latch-up Prevent

HE Xue-qun

(xiamen Lingxi Semiconductor Technology Co., Ltd., Xiamen Fujian 361008)

Abstract:In the layout design, latch-up latch is a common phenomenon. Circuit design may naturally form, but it is easier to form this structure in layout design. In addition to the latch-up structure formed under normal conditions, we may also encounter a special case, such as the SUB of the tube is the case of the lining, in which case the latch-up latch is formed with carelessness.

Key words:PMOSs SUB isnt fixed;latch-up;Latch prevention