基于PCIe接口的高速数据采集系统

罗义军,陈 松

(武汉大学电子信息学院,湖北武汉 430072)

0 引言

超高速数据采集技术广泛应用在雷达测试、卫星导航、激光、高速数据记录回放、宽带无线网络通讯、频率捷变无线通讯等多个领域[1-2]。传统高速信号采集存储系统主要分为基于PCIe总线计算机采集存储系统、VPX架构的SATA采集存储系统和嵌入式采集存储系统。本设计为基于PCIe总线计算机采集存储系统,在已有的系统架构基础上,实现了具有更加通用化、集成化、可扩展的硬件架构,更加高速、高精度、可定制的多通道同步采集系统,最终能实现最高达2 GB/s的传输速率和60 GB的数据存储量,且具有非常稳定的性能。

1 系统整体设计

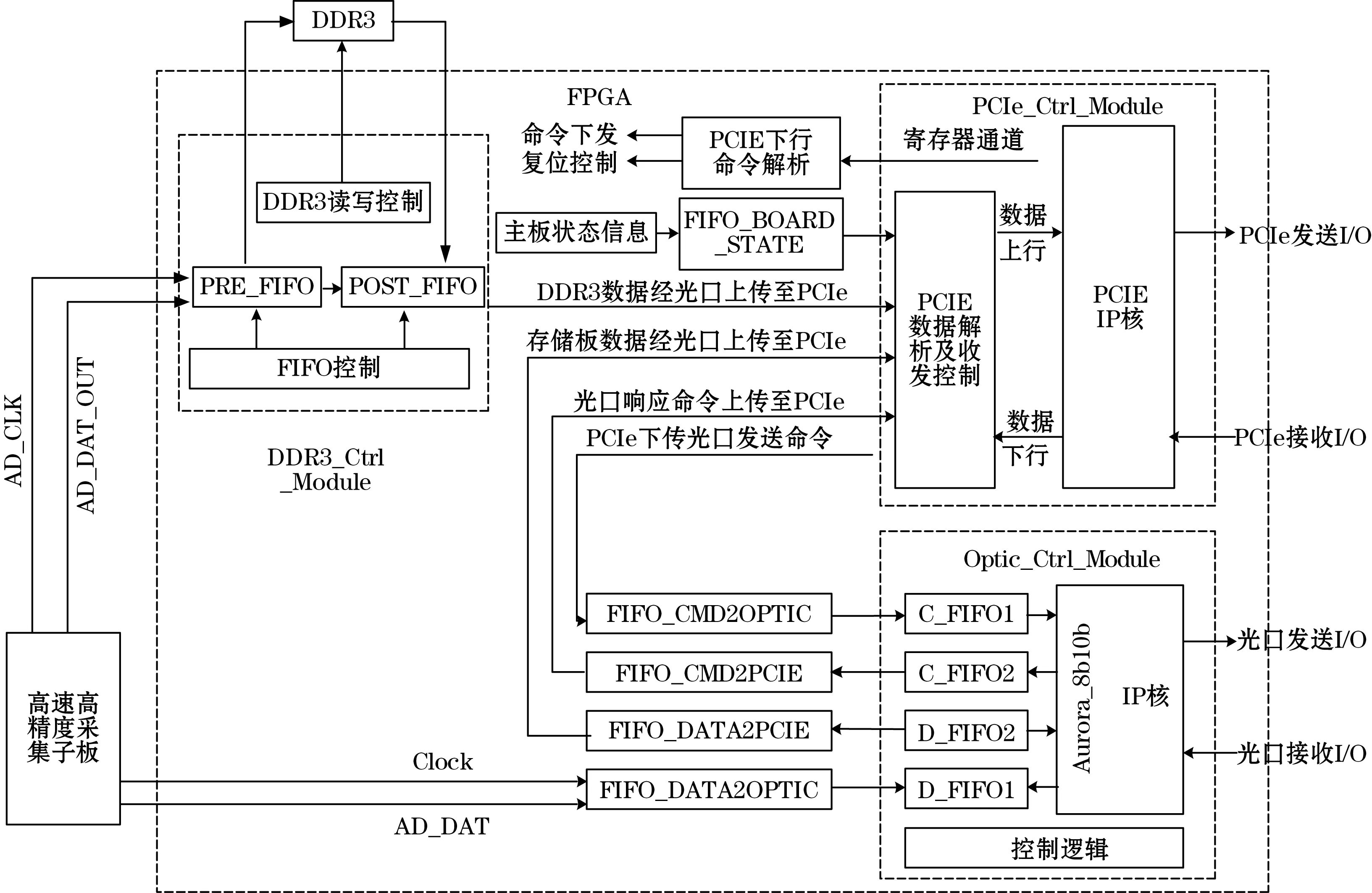

根据功能需求,整个系统架构包括FPGA控制载板、AD数据采集子板和外部存储板。其中FPGA控制载板包含AD数据采集模块、数据处理模快、DDR3数据缓存控制模块、PCIe接口控制模块、光口传输控制模块。AD采集子板通过FMC接口与FPGA载板相连,外部存储板通过光口与FPGA载板相连。系统整体组成如图1所示。

图1 整体系统架构图

整个数据采集存储系统的基本工作流程为:采集子板上的ADC将采集到的信号转换成数字信号高速传输到FPGA,FPGA完成数据接收和处理,并根据需要采集的数据量将数据传输至DDR3缓存模块进行缓存,以备PCIe进行少量采集数据上传;或者通过光口传输至大容量SSD缓存模块进行缓存,上位机PC在数据缓存完毕后可按需通过PCIe接口将大容量SSD缓存模块缓存的数据回传到FPGA中再进行上传[3]。

AD采集子板通过FMC(FPGA mezzanine card)与FPGA载板相连。FMC不仅简化了I/O接口模块设计,同时还能最大化载卡的重复使用率,支持高达10 Gb/s 的信号传输速率,夹层卡和载卡之间潜在总带宽达40 Gb/s。FMC标准有助于将现有的 FPGA载卡设计重新用到新的 I/O 上,而这只需更换 FMC 模块并对 FPGA 设计略作调整即可[4]。这样,同一个FPGA载板可以通过子板的设计实现不同的扩展功能,整个系统的应用更加灵活。

2 硬件电路设计

2.1 AD数据采样模块

系统设计为可定制扩展的模式,即针对不同采样信号选用不同AD芯片设计的数据采集子板,以满足信号带宽、通道数、量化位数的要求,兼顾系统的兼容性和通用性。 AD芯片基本参数见表1。

2.2 FPGA控制和数据传输模块设计

模拟输入信号经AD采样后送到FPGA,经FPGA内部FIFO后写入DDR3缓存。上述4种种信号中的前3种采样信号数据缓存结束后,控制相应DDR3数据读出。DDR3读出数据进行片内FIFO缓存后,经PCIe控制模块的控制,由PCIe接口送到上位机。第四种采样数据由于数据量大,采样率高,无法将数据缓存在DDR3中,采样的数据直接经过FIFO和光口缓存到外部存储板中,当缓存完毕之后,上位机下发命令上传数据,再经过光口将缓存的数据经过FIFO和PCIe接口送到上位机。以AD芯片为ADS54J60的采集子板为例,整个数据采集、传输、存储的实现机制流程图如图2。

图2 总体流程图

2.2.1 DDR3读写模块设计

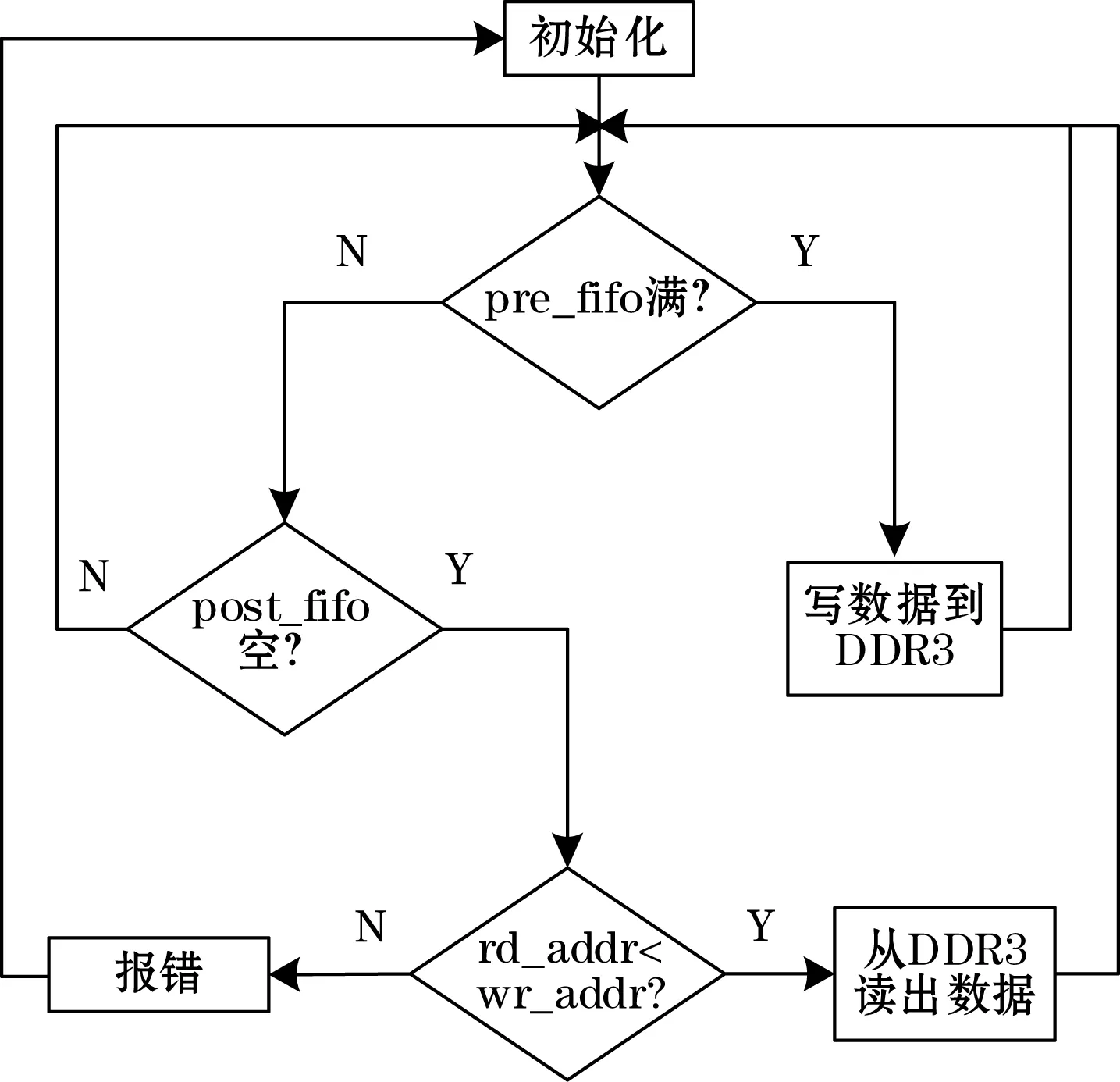

当需要的数据量较少,在DDR3的存储内存大小范围内时,直接使用DDR3作为缓存。在DDR3的前级和后级各加一个FIFO,做到当数据来时,且前级WR_FIFO缓存到达一定程度,DDR3可以自动将WR_FIFO的数据读出并写入DDR3,当DDR3检测到后级RD_FIFO无数据为空并且DDR3的读指针在写指针后面时,DDR3能自动读出DDR3的一帧数据并写入到RD_FIFO中供后续模块使用。DDR3读写数据的控制流程如图3所示。

图3 DDR3读写控制

无论是写入数据到DDR3还是从DDR3读取数据,均由上位机通过PCIe下行命令控制起止时刻。在存储ADC采集数据至DDR3时,上位机会先设定好本次需要存储至DDR3的数据个数,然后开始将ADC的数据写入WR_FIFO,直到DDR3存储够了该个数的数据后,停止存储。当需要将数据从DDR3读取至PCIe时,不需要指定上传数据个数,仅需要将DDR3读空即可,DDR3读空后,便停止数据上传至PCIe,完成本次数据上传。当然,FIFO的控制过程中还会遇到写满和读空的情况,需要进一步地进行控制。

2.2.2 PCIe接口设计

本文设计的高速数据采集板为3U PCIe板卡,因此在数字信号处理载板与工控机的交互使用PCIe接口。PCIe是高速串行计算机扩展总线标准,使用端到端的连接方式,可以进行高速串行点对地的双通道高带宽传输。PCle接口模块是本系统设计中的关键模块,用来实现采集板和上位机之间的高速数据传输和命令传输。

PCIe接口目前有3个版本,即PCIe1.0、PCIe2.0和PCIe3.0,各版本性能参数见表2。本次设计中采用PCIe2.0 x4接口,其可提供的链路带宽为20 GT/s,满足本文设计中与上位机的数据交互带宽需求。

表2 PCIe各版本性能参数

XC7K325T芯片内部集成了PCIe硬核模块,在不占用额外逻辑资源的情况下便可完成高性能、高效率的PCIe接口设计。该 IP 核占用 FPGA 资源少、功耗低,包含有物理层、数据链路层和事务层。 如图4所示,每一层都完成各自的功能,层与层之间有明确的分工,事务层与数据链路层负责将采集到的数据按批次组包,数据包在层与层之间传递时会附加对应的校验和帧信息。在PCIe的硬核中已经实现了物理层和数据链路层的设计,将开发周期中最复杂也最难调试的部分已经简化,用户在设计时仅需要完成事物层的交互和控制即可[5-6]。

图4 PCIe接口结构

2.2.3 光纤传输接口设计

在进行数据采集时,需要不间断传输和存储时间长度为30 s的单通道高速高精度ADC采集数据。采样时钟为1 GHz的高速采集且数据精度很高,在30 s的时间内,AD单通道采集的数据量为:1G×1×16×30=480 Gb=60 GB,显然板载DDR3的容量已经无法满足需求,因此高速数据采集板需要外挂一块板载有大容量SSD存储模块的后端数据存储板来存储这种大量的采样数据。同时,在高速时钟采样下, ADC采集数据时的数据吞吐率达到了1G×1×16 bit/s=16 Gbps=2 GB/s,所以传输数据的接口带宽必须能够满足2 GB/s的数据传输需求。

针对这一需求,本设计中选择的是光纤接口,光纤传输接口不仅可以满足带宽要求, XC7K325T的FPGA内嵌的RocketIO还拥有十分强大灵活的IP核支持,可以简化光纤传输硬件电路,同时Xilinx官方参与制定的Aurora协议适用于光纤传输,用户可以很方便的添加上层应用,也能适用于大多数内嵌RocketIO的FPGA,因此本次设计选用光纤传输接口来实现超高吞吐率和超大数据量的板间数据传输,图5是AuroraIP核的内部结构[7-8]。

图5 AuroraIP核内部结构图

3 上位机控制流程

整个系统是配合上位机来对信号进行采样的,上位机对FPGA发送采样需要的各种参数,FPGA在参数配置完成后会开始进行采样,将数据进行存储和上传。启动上位机应用程序,操作界面分为控制区和日志输出区,如图6所示。

图6 上位机控制界面

上位机的操作步骤为:

(1)打开板卡。在确认板卡正确插入卡槽后,点击打开板卡按钮,若右侧日志显示“板卡1打开成功,板卡2打开成功”,且板卡标号分别显示0x2,0x3则表示AD两块采集卡打开成功;若显示“打开设备失败”或其中一块失败则表示板卡打开不成功,需检查板卡是否插好,确保无接触不良,检查后关掉上位机重新打开。

(2)相位校准。若需要校准相位,则在设置相位的输入框中框中填入所需校准时长,该值不大于50。交付时系统已校准完毕,无需校准,每次重新开机点击开始校准。

(3)板卡复位。在任何状态下如需要板卡复位则可点击复位按钮,使板卡回到初始状态。若日志区显示“FPGA复位成功”, 则表示复位成功;若显示FPGA复位失败,则需关掉上位机重新打开或更新驱动。

(4)数据采集与存储。在采样时间框中输入所需采集时长,如10 s。然后点击开始采集,当日志区显示“数据存储完毕”则可进行数据上传操作。

(5)定时长采集数据上传。当采集完毕后若要将存储数据上传至上位机则需在数据长度框中设置所需上传数据量,如1 GB,则填入1 024,然后选择文件保存路径,点击上传数据即完成数据上传,日志显示区显示“数据上传完毕”。

4 测试验证

为了验证系统在采样和存储的过程中不会出现数据丢失,测试采用内部累加信号源作为整个FPGA系统的信号源。数据源为FPGA内部产生的长度为64 bit的连续整数,送入后级经过DDR3、光口、后级存储板、PCIe接口送到上位机,上位机接收到的累加数据如图7所示。

图7 上位机接收到的累加数据

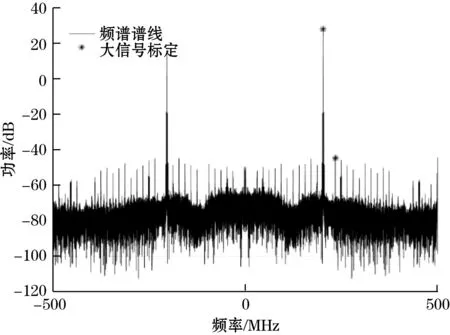

上位机将接收的数据进行数据长度检测,与信号源预设的数据长度进行比对,看是否相同。本次测试最长测试了60 GB数据量,结果为所有数据无丢失,准确无误全部上传到上位机。测试完系统传输数据的稳定性之后,对系统进行实际信号采集传输测试,观测信号频谱和信噪比。 测试信号为200 MHz正弦波,采样频率为1 GHz,采样方式为连续采样,采样时长为30 s,数据量高达60 GB,截取部分采集数据频谱见图8,信号的信噪比40.26 dBm。

图8 高精度带通测试信号200 MHz频谱图

本设计与当前主流高速AD采集卡基本参数对比见表3。由表3可知,本设计优点在于AD采集子卡可定制性和可扩展性强,采样精度高,采样率范围较宽,采用光口传输保证更高的传输速率,最高达到2 GB/s。且数据存储容量也扩展到了60 GB。

5 结论

本文设计了一种基于 FPGA 的可扩展 PCIe高速数据采集传输系统,主要通过光口进行数据存储,通过PCIe接口进行数据传输。能实现高采样率、超高传输速率和大容量存储,具有抗干扰能力强,稳定性好等特点,适用与各种高速数据采集传输领域,包括通信、声纳、遥感、地质勘探、激光多普勒测速、光时间域反射测量等领域。

表3 本设计与当前主流高速AD采集卡基本参数