基于FPGA片内Flash实现数据的动态加载和读取*

周 刚,曹健辉,彭 勃

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

本项目中涉及到4个通道的射频发射电路,频段覆盖225~400 MHz,射频输出幅度会随着频率的变化而变化。由于DA输出属于模拟电路,加之元器件的个体差异,常会导致相同电路、不同频率射频输出幅度不一致。每个通道的输出功率均有平坦度要求,因此每台设备的4个通道均需根据实际输出功率调整射频输出的衰减量,确定4个通道的衰减量后,编译生成本台设备的下载文件。根据经验,一般1 MHz频率内对应一个校正值。例如,175 MHz范围只需175个矫正值即可。此种方式导致每台设备的调试测试均需要重新编译FPGA工程文件,工作量大且不利于FPGA程序的归档和使用。

考虑两种改进方案。

方案一为传统的FPGA+SPI Flash或者FPGA+CPLD+Flash设计方案。由于硬件已经开发完成,此方案的缺点在于需要修改硬件电路,增加单独的Flash芯片或者CPLD芯片,因此实现难度较大,不建议采用。

方案二为直接利用Xilinx公司Spartan-3AN系列FPGA内含Flash进行设计改进。此FPGA内含16 MB内存的Flash,在PC中开发参数配置软件,通过串口下载配置文件至FPGA中的片内Flash。因为FPGA自带串行外围设备接口(Serial Peripheral Interface,SPI),FPGA每次开机后自动读取片内Flash的配置文件,也可以根据需要从FPGA的片内Flash中读取配置文件。

1 Spartan-3AN

1.1 Spartan-3AN主要特点

Spartan-3AN FPGA平台是Xilinx公司于2007年推出的非易失性FPGA解决方案,基于成熟的90 nm工艺的低成本FPGA构架,融合了SRAM技术和可靠的非易失性闪存技术。

以XC3S1400AN-4FGG676I为例,Spartan-3AN FPGA平台的主要特点如下[1]:

(1)工作温度范围:-40~100 ℃(结温);

(2)门数/乘积项:1 400 000门;

(3)最高工作频率:250 MHz;

(4)传输延迟时间≤1.21 ns;

(5)最大用户I/O数:502个;

(6)电源电压:1.2 V;

(7)I/O端电压:1.1~3.6 V;

(8)逻辑单元:25 344个;

(9)片内Flash容量:16 MB。

1.2 Spartan-3AN片内Flash特点

Flash又称为闪存,具有可电擦写、掉电后数据不丢失的特性,且容量大、功耗低、速度快,在现代电子产品中应用广泛[2]。

以XC3S1400AN-4FGG676I为例,Spartan-3AN系列FPGA中片内Flash的主要特点如下[1]:

(1)片内Flash容量:16 MB;

(2)SRAM页面缓冲区:2个;

(3)较小的空间(264 B或528 B)存储非易失性数据;

(4)随机存取,二进制地址可设置;

(5)最大66 MHz连续数据传输;

(6)支持全部擦除、块擦除和扇区擦除;

(7)重点区域数据具备保护功能和防护措施;

(8)128 B安全存储空间;

(9)支持100 000次擦写;

(10)Flash数据可保存20年;

(11)支持多种Flash使用方式。

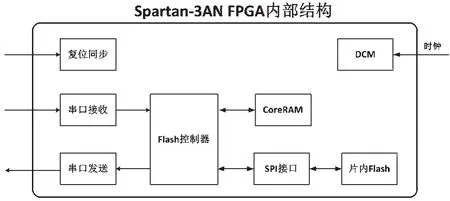

Spartan-3AN系列FPGA内部结构,如图1所示[3]。

图1 Spartan-3AN系列FPGA内部结构

Spartan-3AN系列FPGA中片内Flash的配置接口,如图2所示。

图2 Spartan-3AN系列FPGA中片内Flash的配置接口

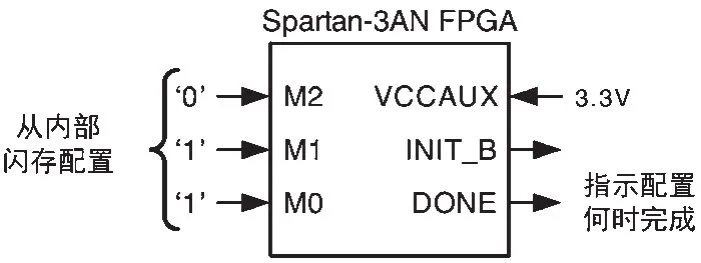

1.3 SPI接口

SPI是由Motorola公司推出的一种高速、全双工的同步串行通信总线,可以使MCU与各种外围设备以串行方式进行通信并交换信息。SPI接口主要有4根信号线:时钟信号线(CLK)、主输出/从机输入数据线(MISI)、主输入/从机输出数据线(MISO)和片选信号线(CSB)[4]。SPI接口框图如图3所示[5]。

图3 SPI接口

目前,Spartan-3AN等FPGA内含Flash模块,支持SPI接口。对于Spartan-3AN,FPGA是SPI主器件,SPI Flash PROM是从器件。

2 系统架构

本文构建了一个通过SPI接口实现FPGA片内Flash数据动态加载和读取的系统,系统架构如图4所示。

图4 系统架构

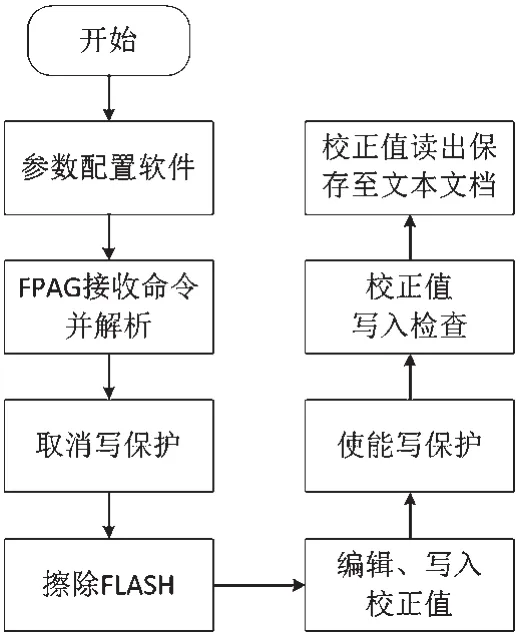

系统校正值写入流程,如图5所示。

图5 校正值写入流程

系统校正值读取流程,如图6所示。

图6 校正值读取流程

2.1 ISF Flash控制

SPI_ACCESS原语用来连接FPGA应用层和系统Flash。使用中,FPGA应用层是主,系统Flash是从。该原语包括MISO、MOSI、CSB和CLK四个管脚。

MISO:主入从出,串行数据从系统Flash存储空间中输出至FPGA应用层逻辑;

MOSI:主出从入,串行数据从FPGA应用层逻辑中输出至系统Flash存储空间;

CSB:系统Flash片选使能信号,低电平有效;

CLK:系统Flash操作时钟,由FPGA应用层逻辑给出。

SPI_ACCESS原语属性定义包括以下内容:

(1)SIM_DVICE:用来定义目标芯片类型,type为String,本实现中赋值“3S1400AN”;

(2)SIM_USE_ID:用来定义SPI存储器安全寄存器中的编程用户ID,type为16进制数据,本实现中赋值“0XFF”;

(3)SIM_MEM_FILE:用来指定存储初始化值的文件,type为String,本实现中赋值“NONE”;

(4)SIM_FACTORY_ID:用来指定安全寄存器中的用户识别号,type为16进制数据,本实现中赋值“0X00”;

(5)SIM_DELAY_TYPE:用来指定仿真延时类型,type为String,本实现中赋值“SCALED”。

2.2 ISF Flash地址分配策略

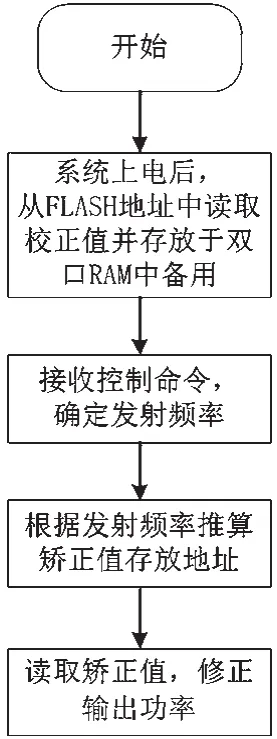

XC3S1400AN内部SPI FLASH基础构成是page。page是系统FPGA中的最小可擦除单元,每个page包含528个字节,8个page可组成一个block,32个block组成一个sector。

应用层可针对page、block和sector单独进行擦除操作,并且可对sector单独进行锁住和保护。内部SPI Flash存储结构如图7所示。

图7 内部SPI Flash存储结构

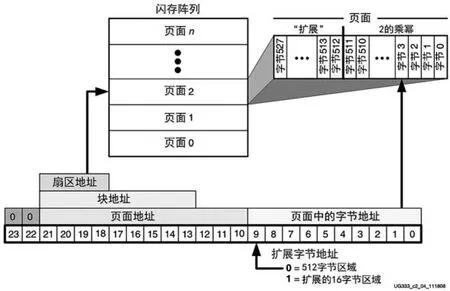

XC3S1400AN系列FPGA的默认寻址方式,如图8所示[5],本文即采用这种默认地址分配模式。

2.3 ISF Flash读寄存器

状态寄存器读取命令时序,如图9所示[5]。

图8 XC3S1400AN FPGA默认寻址方式

图9 状态寄存器读取命令时序

(1)在开始发送读取命令前,CSB必须开始拉低,并在整个读取过程中一直保持低电平;

(2)读取状态寄存器命令为0XD7,并伴随时钟下降沿以二进制形式“11010111”传至MOSI;

(3)系统Flash伴随时钟上升沿捕捉传来的数据;

(4)在状态结果输出之前,MISO一直保持高电平;

(5)在读取命令传输完毕后,系统存储器伴随时钟下降沿将状态寄存器内的内容一一输出,高位在前,低位在后;

(6)FPGA应用层伴随时钟上升沿捕捉系统存储器的状态信息;

(7)在系统存储器状态信息读取完毕后,将CSB拉高,结束读取过程。

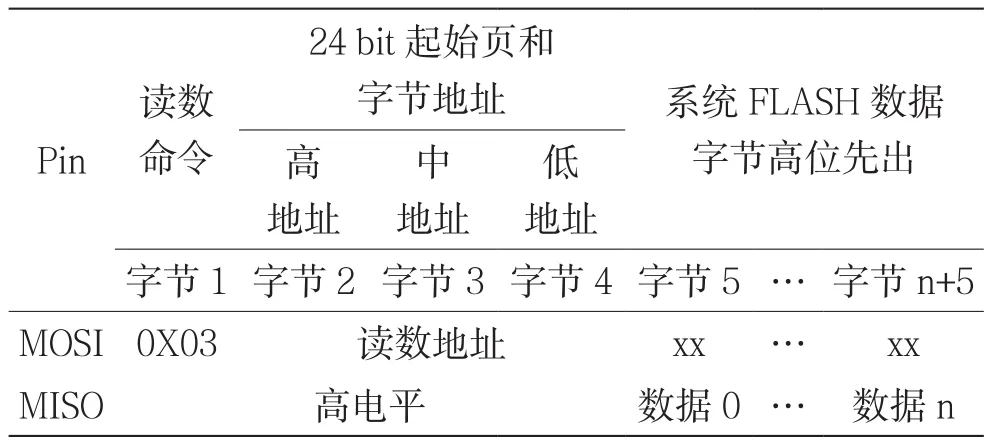

2.4 ISF Flash读数据命令

系统Flash读取命令有多种读取方式,包括快速读取、自由读取、页缓存至Buffer读取和Buffer读取等。本应用采取自由读取,原因是快速读取适合小数据量、自由读取;读取数据无延时,读取时钟可达33 MHz,满足本系统的使用需求。

读取命令格式及要求如表1所示。

表1 读取命令格式及要求

注意事项:

(1)读取输出数据无延时;

(2)当CSB保持低电平时,MISO数据随时钟下降沿串行输出,高位先出,地址会自动增加,无需人为控制;

(3)当CSB拉高时,结束数据读取操作。

读取命令的Chipscope截图,如图10所示。

2.5 ISF Flash写数据命令

系统Flash读取命令有多种读取方式,包括Buffer写、页擦除Buffer写、页不擦除Buffer写、页Buffer写、页Buffer比对和自动页写。本应用采取页Buffer写,原因是页Buffer写是将Buffer写和Buffer页擦除合二为一,用一条指令就完成了两个操作,减少了命令条数,简化了操作步骤,降低了出错概率,提高了写数据的效率。

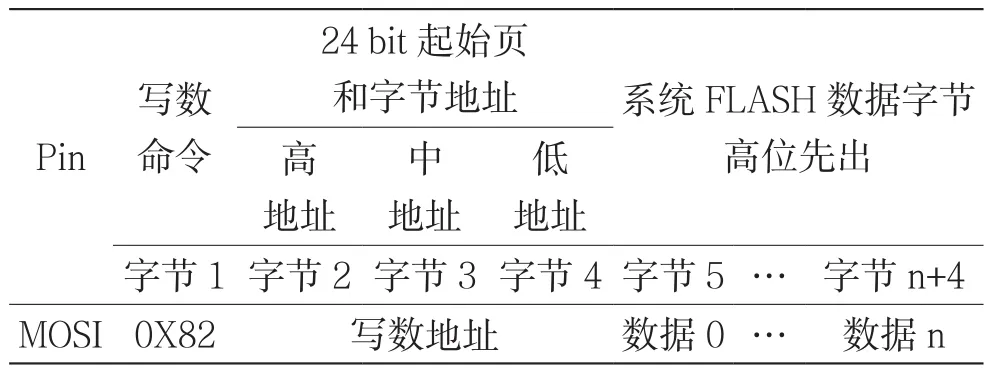

写数命令格式及要求如表2所示。

表2 写数命令格式及要求

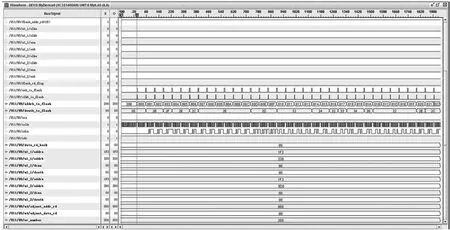

写数命令的Chipscope截图,如图11所示。

图11 写数命令的Chipscope截图

2.6 ISF Flash擦除命令

擦除有三种擦除模式:页擦除、block擦除和sector擦除。为防止sector误擦除和非授权的擦除,可实现sector保护和sector锁住。

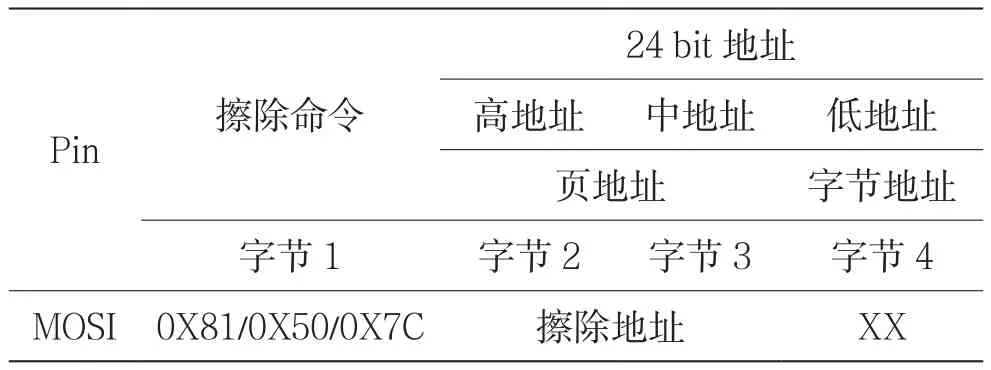

页擦除、block擦除和sector擦除命令格式及要求如表3所示。

表3 擦除命令格式及要求

擦除完毕后,相应擦除存储空间里的数据为0XFF。

2.7 ISF Flash Sector保护命令

Sector保护寄存器状态读取:相应的命令控制字为0X32。

Sector保护寄存器擦除:相应的命令控制字为0X3D+0X2A+0X7F+0XCF。

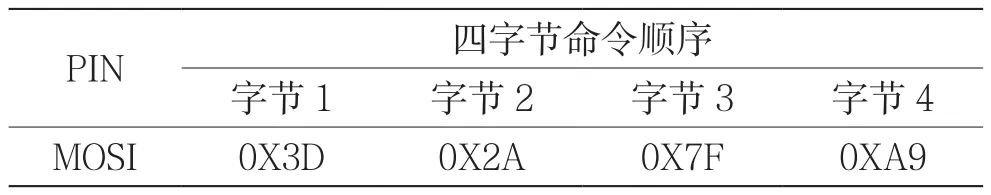

Sector保护寄存器擦除格式如表4所示。

表4 Sector保护寄存器擦除格式

擦除Sector保护寄存器后,Sector保护寄存器每个字节的值变为0XFF,代表所有的Sector均被保护。

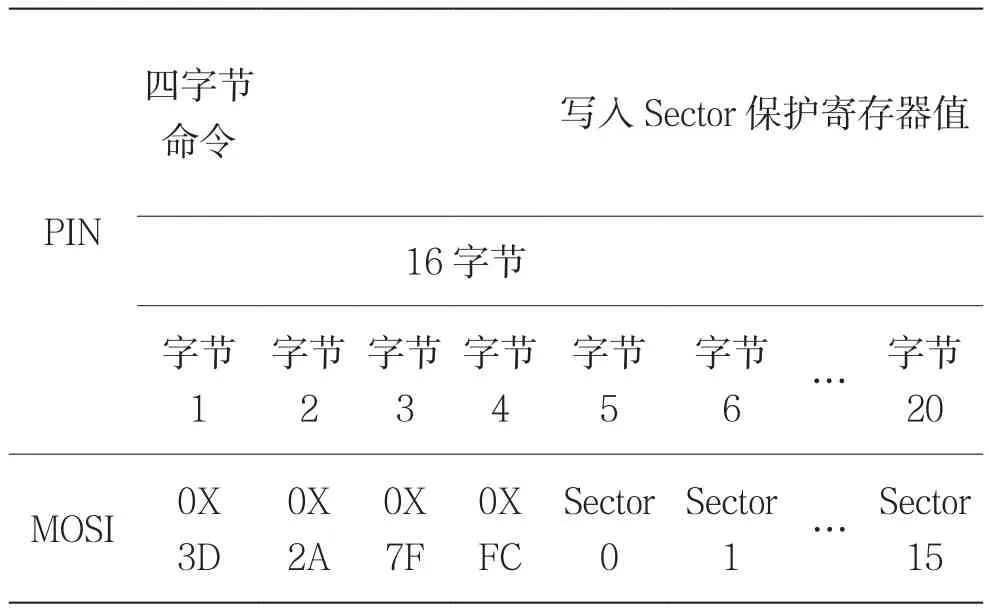

Sector保护寄存器写入:相应的命令控制字为0X3D+0X2A+0X7F+0XFC。

Sector保护寄存器写入格式如表5所示。

表5 Sector保护寄存器写入格式

Sector保护寄存器读出:相应的命令控制字为0X32。

Sector保护寄存器读取格式如表6所示。

表6 Sector保护寄存器读取格式

Sector保护寄存器使能:相应的命令控制字为0X3D+0X2A+0X7F+0XA9。

Sector保护寄存器寄存器使能格式如表7所示。

表7 Sector保护寄存器使能格式

Sector保护寄存器禁用:相应的命令控制字为0X3D+0X2A+0X7F+0X9A。

Sector保护寄存器禁用格式如表8所示。

表8 Sector保护寄存器禁用格式

2.8 参数配置软件

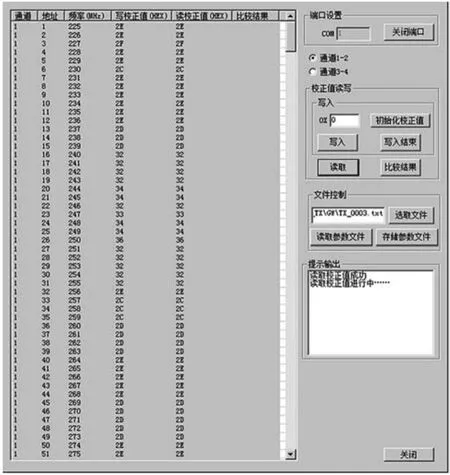

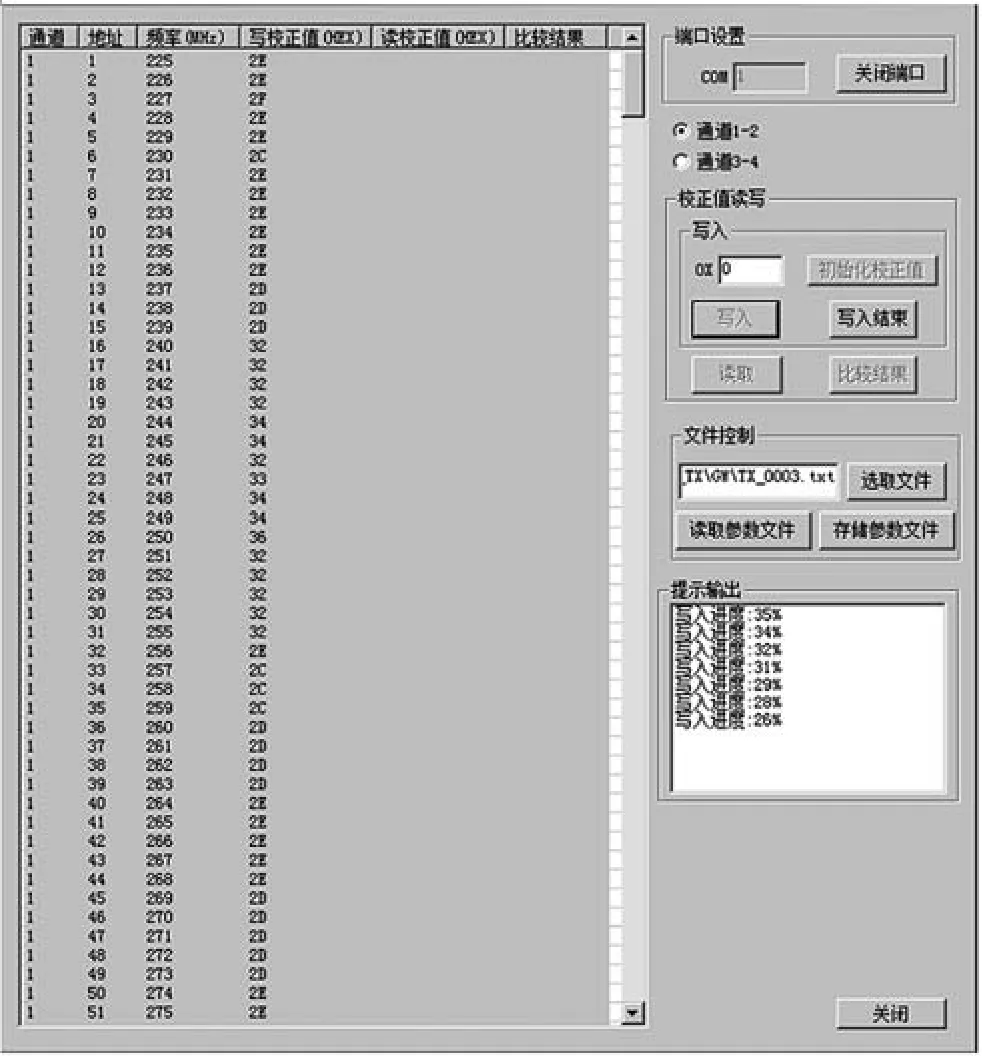

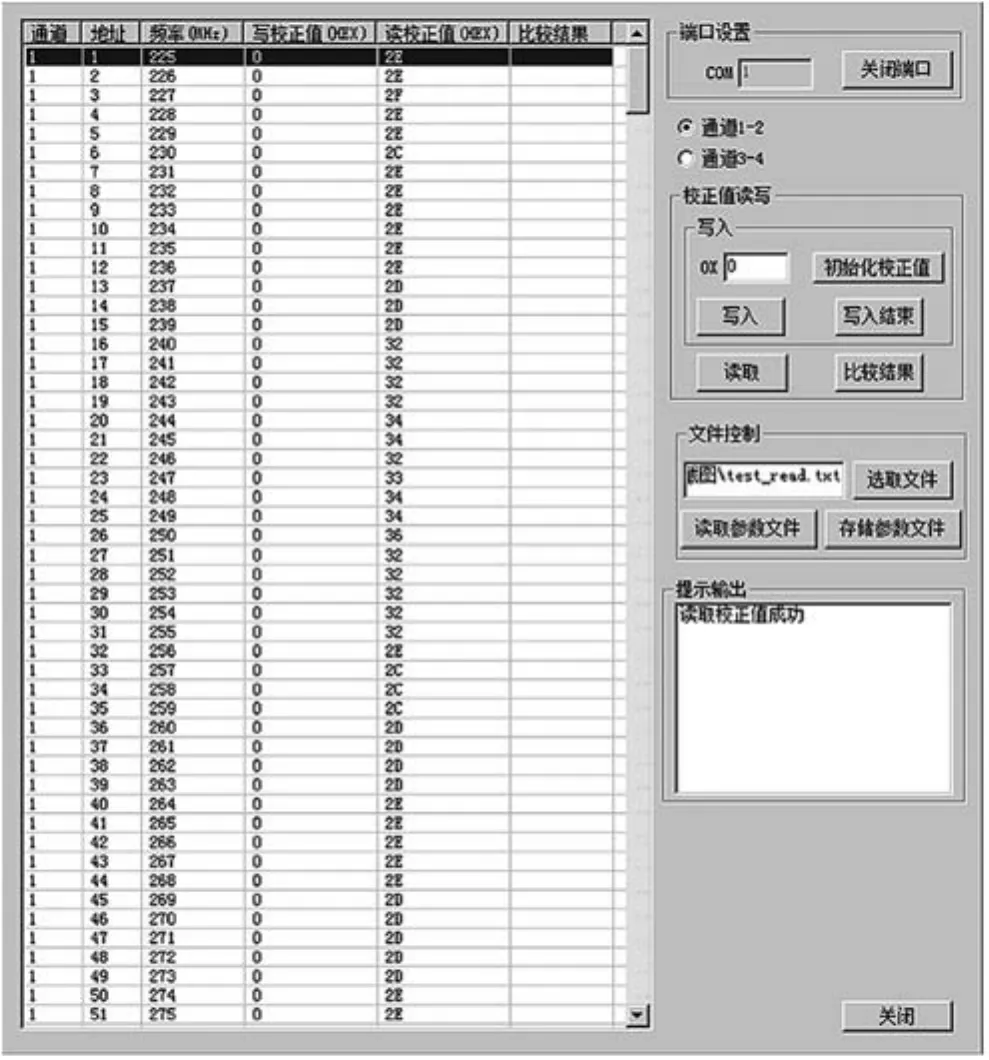

参数配置软件布置于一台普通PC中,通过串口与射频控制模块的FPGA相连,实现COM选择、通道选择、参数文件的读取和存储。参数配置软件截图如图12所示。

图12 参数配置软件截图

3 实现过程

制备显控小软件一个,该软件具备以下功能:能通过RS232协议与FPGA应用层进行通信;可下发系统Flash擦除、写入、回读和sector保护功能等;可将要写入的数据和地址一一对应保存在文本文件中;待写入完毕后,进行写入数据回读并一一比对,判定是否写入成功。若写入成功,则结束烧写;失败则再重写,直到烧写成功。

系统FPGA应用软件一套,该软件具备以下功能:能通过RS232协议与FPGA应用层进行通信,能正确接收显控下发的命令信息,执行相应的系统Flash擦除、写入、回读和sector保护等操作。在系统上电后,该系统运行后稍做延时,会执行从Flash读数据的操作,根据系统需要将读取到的数据保存至双口RAM,待程序需要该数据时会根据索引从相应的RAM地址中读取数据并使用,增加了系统应用的灵活性。

当系统程序控制DA发射射频时,系统会根据发射频率计算应该取双口RAM哪个地址中的矫正值。例如,发射频率范围为200~400 MHz,则200~201 MHz对应的矫正值保存在第1个地址中,201~202 MHz对应的矫正值保存在第2个地址中;以此类推,399~400 MHz对应的矫正值保存在第200个地址中,400 MHz对应的矫正值保存在第201个地址中。具体实现中,读校正值地址可通过addr=(Freqence-200 000 000)/1 000 000计算,即对结果取整获取所需的地址值;其他的读操作逻辑控制相应的给出,即可正确读出校正值。然后,矫正值被提出并转化为对应频率的功率补偿,进而实现DA输出幅度的平坦性。

4 试验验证

参数配置软件写入截图,如图13所示。

参数配置软件读取截图,如图14所示。

5 结 语

本文设计并实现了一种基于FPGA片内Flash进行数据加载和读取的方法:以装在普通PC中的参数配置软件作为配置主控制器,通过串口对FPGA片内的Flash进行控制,成功实现了对FPGA的数据动态加载和读取。

在应用该系统前,需根据每个频率测量求得一个校正值,并将校正值写入系统应用程序中。这样做的缺点是:针对每台设备校正值不同,需要重新修改源代码中相应的校正值,并对源代码进行编译烧写。这样不便于程序的版本控制,需对每台设备准备一套与之对应的版本程序,给设备后期维护带来了较大不便,尤其当设备大批量生产时。

图13 写入截图

图14 读取截图

应用该系统后,程序版本只需要一个版本,矫正值会存入Flash中,并可以根据DA发射频率将校正值读取出使用。后期设备维修维护时只需读出Flash中的校正值并保存至文本文件。硬件更换后,根据需要修改更换后硬件部分对应的校正值,并再次保存归档。当新的矫正数据写入完毕后,还可通过回读命令自动进行校正值的回读和比对,确保矫正值完全读写正确,提高了设备的稳定性,简化了操作的复杂性,节省了大量人力,尤其在设备大批量生产时。