基于FPGA的高帧频图像跟踪系统设计

(陕西理工大学 电气工程学院,陕西 汉中 723000)

0 引言

在高速运动的导弹末端制导、弹道实验或机载武器姿态跟踪系统中,需要快速地捕获目标与实时定位,完整记录高速实验数据,为目标高速运动规律研究和性能分析提供数据支撑[1-2]。高帧频图像跟踪系统的效果容易受到众多因素干扰,这对高帧频CMOS图像传感器、图像接口模块、图像处理器和跟踪机构等提出了更高的要求[3-4]。

现有高帧频图像处理系统多采用并行工作方式的FPGA器件,实现与图像传感器接口及内部算法并行处理功能。文献[5]通过Camera Link接口,利用FPGA对分辨率为2048×1088像素、帧频为280fps的图像进行采集、存储、目标粗定位等处理,利用DSP完成目标准确定位和实时跟踪,系统处理数据量大,相对较为复杂。文献[6]对分辨率为300×300像素、帧频1 000 Hz信标光斑图像的进行捕获、预处理、阈值分割和形心定位,实现了高帧频激光光斑跟踪与瞄准功能,系统结构简单,但图像采集与处理不能同步进行。文献[7]对分辨率为1280×1024、帧频为500fps的图像进行图像捕获、高速缓存、千兆网传输、外部控制功能,系统采用一片SDRAM完成图像采集和处理的缓冲功能,处理效率相对较低。文献[8]将DRAM分割成两个乒乓块Bank0-1和Bank2-3,采用兵乓切换方式读写DRAM中Bank0-1和Bank2-3区域,这种工作方式一定程度上提高系统处理速度,但图像保存和图像处理分开,系统工作效率仍旧不高。

为了提高高帧频图像系统的实时采集、处理需求,本文利用CMOS图像传感器LUPA-300、CycloneIV EP4CE115和2片DDR2等设计了一种高帧频图像目标跟踪系统,该系统能够对分辨率为640×480像素、帧频250 Hz的图像进行捕获、阈值分割、形心定位等处理,实现对高速运动目标进行精确跟踪。

1 系统总体方案设计

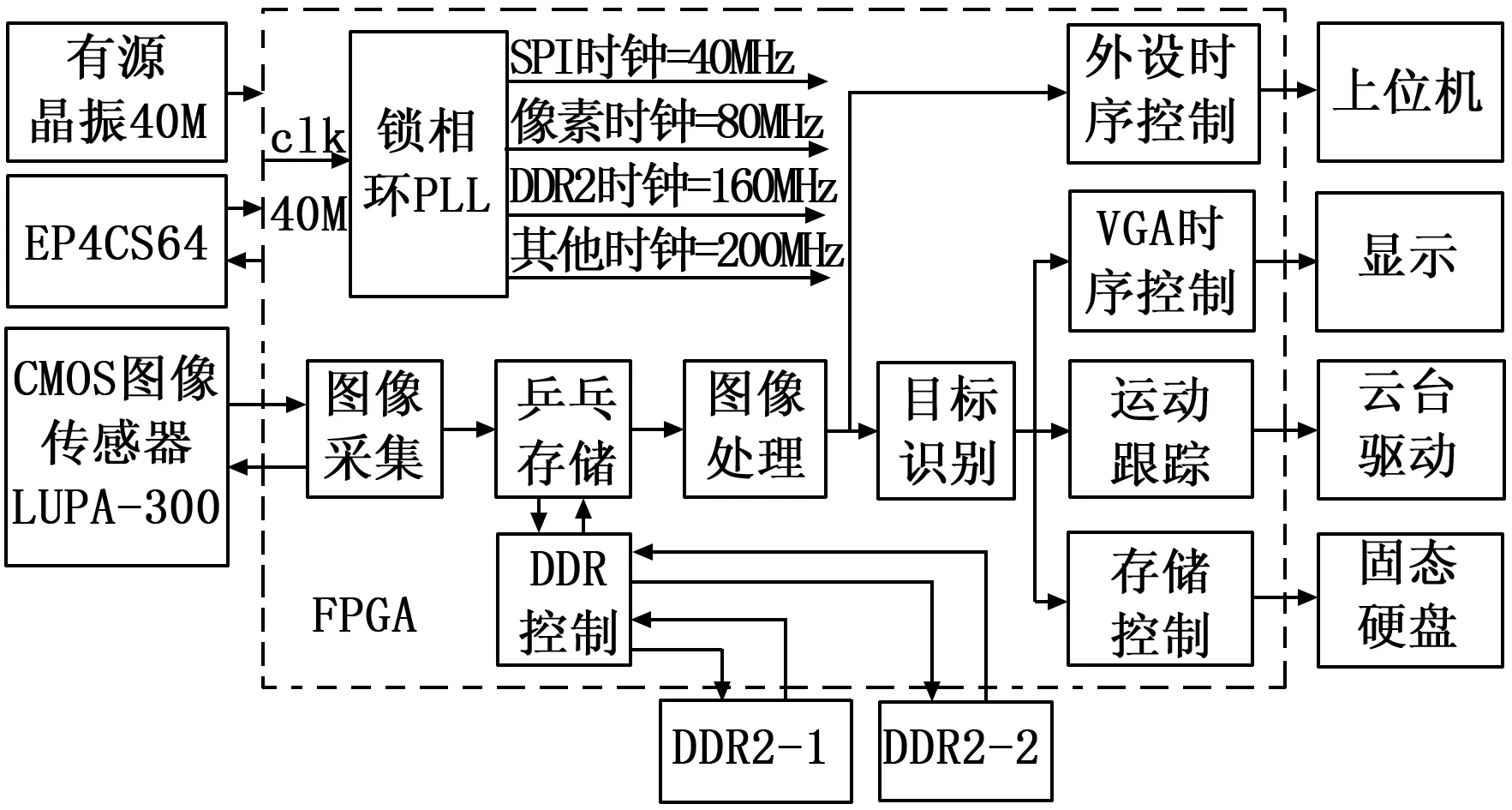

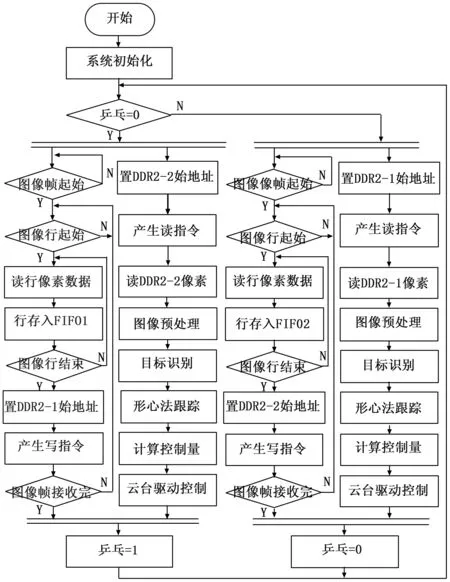

图像跟踪系统是利用FPGA对高帧频CMOS图像传感器图像进行捕获、预处理、目标识别、形心跟踪和云台驱动控制。系统结构如图1所示,主要包括FPGA模块、高帧频CMOS图像传感器模块、外设时钟模块、2片DDR2模块、二维云台控制模块和RS232、USB2.0、以太网等外设接口模块等。

图1 系统结构框图

FPGA是图像跟踪系统的核心芯片,实现与图像传感器、DDR2、VGA、上位机接口和目标识别与跟踪控制等功能,因而FPGA的内部资源及工作频率决定了整个系统的性能。高帧频图像传感器选用Cypress公司CMOS图像传感器LUPA-300,该芯片内置10位ADC,输出的图像数据长度为10位,数据输出最大速率为80 Mb/s。输出图像具有开窗功能,窗口分辨率为640×480时的帧频数可达250fps;窗口分辨率为256×256时的帧频数可达929fps。图像缓存单元采用美光DDR2芯片MT47H64M16HR,该芯片容量为1 Gbit,数据总线宽度为16位,与FPGA之间数据频率最高可达333 MHz。FPGA选用CYCLONE IV 系列EP4CE115F29C7N,该芯片拥有114480个逻辑单元、3888Kb嵌入式存储器,266个18*18乘法器、4个PLL、528个I/O,可以满足图像乒乓存储、外设接口需求;FPGA芯片的速度等级为C7,内核时最高工作频率为437.5 MHz,锁相环输出时钟最高为450 MHz,能够满足高帧频图像传感器数据传输和DDR2存储需求。

2 系统功能模块设计

FPGA中设计的功能模块如图1所示,主要包括锁相环PLL、图像采集、DDR2乒乓读写、图像处理和运动跟踪等几个模块。通过SPI总线配置LUPA-300芯片内部寄存器、实时采集高帧频图像;DDR2乒乓读写模块用于缓存采集与处理图像帧,避免高帧频图像处理不及时的问题;图像处理模块用于目标动态阈值分割及形心计算;运动跟踪模块用于控制云台跟踪目标。

2.1 锁相环模块设计

根据各功能模块时钟的需求配置PLL,CMOS图像传感器LUPA-300配置总线SPI的时钟为20 MHz,像素输出的主时钟为80 MHz;DDR2存储器MT47H64M16HR的时钟频率最高166.7 MHz,目标识别模块的时钟为200 MHz。因而锁相环模块设计时,选择输入时钟信号为40 MHz的有源晶振,锁相环内部经过分频和倍频配置后,输出四路时钟信号分别为20 MHz、80 MHz、160 MHz和200 MHz。PLL输出的20 MHz时钟信号用于CMOS图像传感器LUPA-300的SPI总线时钟,PLL输出的80 MHz用于读取LUPA-300像素时钟信号,PLL输出的160 MHz用于读写DDR2模块时钟信号,PLL输出的200 MHz其他模块时钟驱动信号。

2.2 高帧频图像采集模块设计

2.2.1 SPI总线时序驱动

LUPA-300的工作模式由内部16个寄存器决定,因而系统上电后,需要通过SPI总线接口(SPI_ENABLE、SPI_CLK和SPI_IN)对CMOS图像传感器LUPA-300的内部寄存器进行配置。依据LUPA-300寄存器参数设置主从工作模式、曝光时间、开窗大小和亚采样等参数。通过配置X方向、Y方向的起始地址,设置图像读入X方向、Y方向的像素开始位置,也可配置图像开窗的宽度和高度。外部40 MHz晶振信号经锁相环后产生80 MHz时钟,再经4分频后产生的20 MHz为SPI时钟。SPI_IN为SPI串行数据输入线,有效数据为16位,其中前4位[15:12]为地址,后12位[11:0]为数据。SPI允许线SPI_ENABLE为低电平时,每个SPI_CLK的上升沿将SPI_IN的串行数据送入LUPA-300内部寄存器,具体配置时序如图2所示。

2.2.2 图像数据采集模块设计

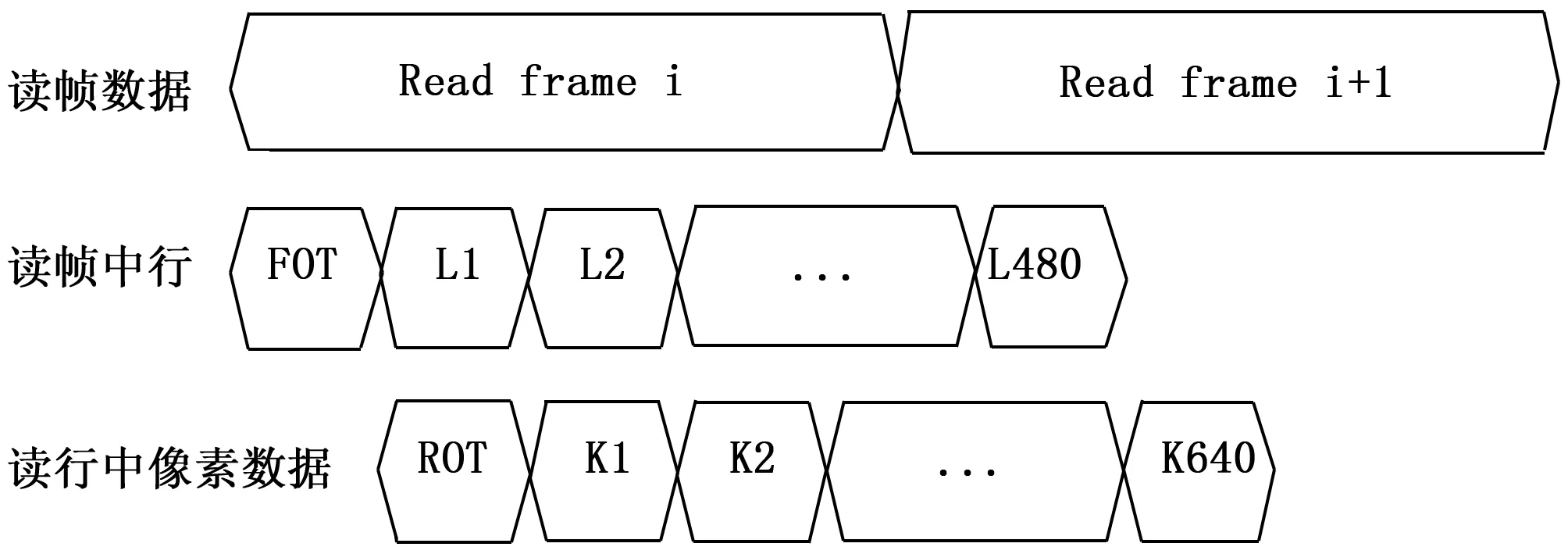

若LUPA-300的16个16位寄存器配置完毕,依据LUPA-300的帧有效FRAME_VALID和行有效LINE_VALID进行图像采集。如图3所示,帧有效FRAME_VALID上升沿表示一帧图像开始输出,在FRAME_VALID为高电平期间,行有效LINE_VALID上升沿表示一行图像开始输出;在LINE_VALID为高电平期间,每个时钟CLK(80 MHz)信号上升沿输出一个像素数据。当一行像素输出完毕,LINE_VALID变低电平,间隔一个ROT时间后 LINE_VALID再次变高电平,开始下一行的输出;当行有效LINE_VALID为低电平,输出无效的像素数据;当一帧图像输出完成后,帧有效FRAME_VALID输出低电平,间隔一个FOT时间后,FRAME_VALID再次有效,开始下一帧图像输出。因而,一帧图像的输出周期可以表示为:Tframe=FOT+Nline·(ROT+Npixels·Tclk)=7.8 μs+480·(400 ns+640·12.5 ns)=4.039 ms。

其中,FOT和ROT分别表示帧开销时间和行开销时间,Nline和Npixels分别为图像帧的行和列数,Tclk为时钟周期。

图3 图像帧读取时序

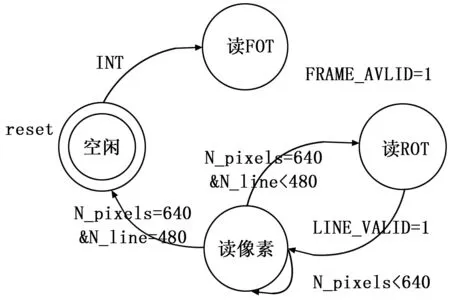

如图4所示,LUPA300 的状态转换图主要分为空闲、读FOT、读ROT和读像素四个状态。每一帧图像从帧开销时间FOT开始,然后逐行读取各行像素数据,则读取第i帧480*640图像的时间等于间隔帧开销时间FOT与读取480行的时间之和;每一行图像从开销时间ROT开始,然后依次读取行中各像素数据,则读取帧中一行的时间等于行开销时间ROT与读取640个像素时间之和。

图4 LUPA 300读图像状态转移图

2.3 DDR2乒乓存储模块设计

LUPA-300图像传感器内部集成4路10位ADC,因而分辨率为640×480的一帧图像存储大小为640×480×10 bit=3.072 Mb。FPGA要进行程序存储和图像数据缓冲,内部容量相对较小,不能满足高速图像存储需求,故选用两片DDR2作为图像缓存。为了保证图像采集与处理能并行执行,系统使用两片DDR2实现乒乓读写操作[9],采集到的图像交替存入DDR2-1和DDR2-2存储器。乒乓方式交替读写DDR2的流程[10]如图5所示,将采集到的图像数据写入DDR2-1的同时读取DDR2-2中图像数据,进行目标识别、跟踪和云台驱动控制等处理;同理,在将采集到的图像数据写入DDR2-2的同时读取DDR2-1中图像数据,进行目标识别、跟踪和云台驱动控制等处理,如此交替乒乓方式读写DDR2。另外,DDR2内部的两个块区域也采用乒乓读写模式,避免同时对一幅图像进行读写操作,保证能够读出完整的一幅图像。

图5 乒乓方式读写DDR流程

2.4 DDR2读写控制模块设计

DDR2控制模块主要包括读写两部分控制功能,由于数据读写速率高,要求数据捕获的精度也高,因而保证DDR2控制模块的信号稳定性和完整性相对较为复杂。利用Quartus软件的MegaWizard管理器产生DDR2 SDRAM控制器IP核。设定该DDR控制模块的参考输入时钟为40 Mhz,DDR2存储器的驱动时钟为160 Mhz,采用全速数据模式读写DDR2器件MT47H64M16。DDR2控制模块设计主要包括PLL、ALTMEMPHY和Memory Controller 三个部分,PLL模块用于DDR2时钟管理,根据输入外设输入的40 MHz时钟产生160 MHz读写时钟信号;ALTMEMPHY模块用于DDR2自动校正和实现DDR2所需物理接口;Memory Controller模块用于产生读写DDR2芯片所需数据和地址时序信号。在DDR2初始化阶段,ALTMEMPHY模块断开用户编写的逻辑控制块,所有读写操作都处于非活动状态,由ALTMEMPHY完成DDR2器件的自动校正。初始化完成后,才能依据控制要求对SDRAM执行读写操作[11]。

SDRAM控制模块的读、写模式都采用突发连续读取模式,只要指定起始列地址与突发长度,就会自动进行寻址与数据的读取。根据SDRAM的读、写工作状态,SDRAM控制模块产生SDRAM读、写需要的地址和控制信号,并对SDRAM的数据进行读、写操作。在将640*480图像写入SDRAM时,输出一行图像数据的长度为640×10bit;设置SDRAM读写的突发长度(Burst Length)为640×16bit,SDRAM每写完一行640×16bit后,发送Burst Stop命令终止当前的突发操作;随后执行刷新操作,再继续读写下一行数据。SDRAM存储器中电容的数据有效保存期上限是64 ms,因而通过不断刷新来保持数据。读写640*480图像数据时以一行图像为单位进行刷新,设定自动刷新时间间隔为64 ms/480=133.3 μs(微秒),这样不会造成数据失效。另外,LUPA 300输出数据速率与SDRAM存取时间不匹配,因而SDRAM前端加入FIFO模块进行图像数据缓冲。

2.5 目标识别模块设计

2.5.1 目标分割

要准确跟踪目标,首先需要将目标从背景图像中分割出来。不同的应用场景下的背景图像复杂多样,而对于空域目标跟踪,背景图像随天气的影响也较大,不能采用固定的阈值分割目标,而应根据输入图像直方图的灰度值选择动态阈值分割目标。

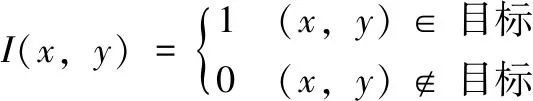

2.5.2 目标形心坐标计算

利用形心法计算目标边界尺寸及中心坐标,具体的目标中心计算方法如下:

2.5.3 目标滤波

将目标从背景之中分割出后,需要对分割的目标进一步数据清洗,滤除空域中云块等干扰信号。由于高帧频相机的相邻两帧图像之间时间差异非常小,空域中稳定飞行目标的姿态和距离摄像头距离不可能产生较大变化,因而相邻两帧图像中分割的目标形心位置和目标区域面积变化也不会太大。分割出目标后,计算当前目标的形心坐标及统计目标区域面积内像素数量,并与上一帧图像中目标的形心坐标及像素数量进行比较。若形心坐标之间距离及目标图像之间像素差异在允许阈值范围内时,则认为是正确的跟踪目标。形心坐标之间距离及目标图像之间像素差异的阈值设置要合理,阈值设定与跟踪目标大小、距离远近有关,阈值过小会导致跟踪不及时,阈值过大会导致跟踪范围广,容易丢失目标。

2.6 目标跟踪模块设计

目标跟踪目的是目标形心坐标位于图像视场中央(320,240)附近,分别依据横向和纵向偏移量,利用增量式PID计算二维云台控制量,加入带死区和抗积分饱和控制,再根据控制量驱动云台俯仰和偏航舵机跟踪目标。在目标跟踪系统设计中,常常出现部分或全部被遮挡,引起跟踪目标丢失,这需要考虑云朵或其它障碍物遮挡时目标跟踪问题。在帧序列图像跟踪中,用FIFO存储500组(约2秒)跟踪目标的特征参数。当分割出目标图像时,释放最早存入FIFO的目标特征参数,存入当前分割目标的特征参数。若跟踪目标部分或全部丢失时,利用前期存储的目标特征参数预测当前目标特征参数,并依据预测值驱动云台跟踪;若长时间仍未捕获目标时,则认为目标丢失,控制云台重新进行全局扫描。

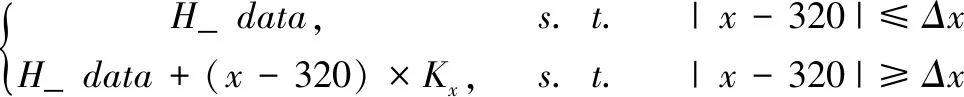

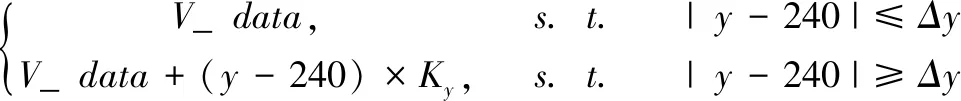

为了平滑跟踪目标,当目标形心在图像中心的四边形区域时,认为目标处于图像中央,控制量不变;否则按照偏移量计算控制量。二维云台控制主要分为偏航和俯仰两个方向控制,具体控制量计算过程如下:

2.6.1 云台偏航方向的控制量可表示为:

H_data=

2.6.2 云台俯仰方向控制量可表示为:

V_data=

3 实验测试及结果分析

将LUPA-300图像传感器配置成分辨率为640×480,帧频为250 fps。系统采用流水线方式并行执行图像读取、图像分割、形心跟踪及二维云台驱动控制功能。由于图像帧频为250 fps,云台的偏航和俯仰方向跟踪舵机选用工作频率在50~300 Hz的DS3120MG,舵机模块的时钟选用1 MHz,周期为4 ms。通过控制两路PWM波的脉冲宽度,从而实现云台偏航和俯仰角度。偏转角度从0°~180°变化对应的脉冲宽度为500~2 500 μs,偏航舵机的控制量范围为1 000~2 000(对应偏航转角45°~135°),俯仰舵机的控制量为800~1 000(对应俯仰角37°~45°)。

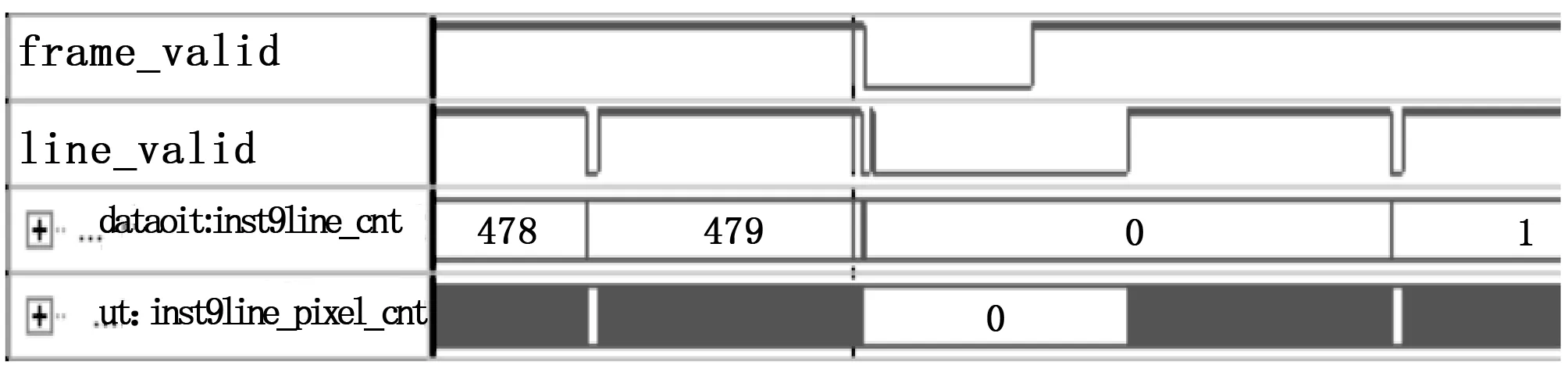

图6为图像采集时序图,利用Quartus软件内部SignalTapII捕获一帧图像,捕获的图像分辨率640×480,line_cnt的计数范围为0~479,每行图像包括640个像素,line_pixel_cnt计数范围为0~639。

图6 图像像素读取时序图

对比采用25fps和250fps的图像跟踪目标光斑实验,采用25fps图像传感器跟踪慢速目标时,跟踪效果差异不明显;跟踪快速目标时,采用25fps图像跟踪目标时,相邻两帧图像之间形心水平方向相差9像素,输出的舵机控制量变化率较大,容易引起不能及时响应,从而使目标脱离图像视场范围。而采用250fps图像传感器跟踪目标时,获得的形心水平方向相差2像素,形心轨迹点较多,曲线相对光滑,控制量曲线平滑,跟踪效果相对较好。

4 结论

本文给出一种基于高帧频图像传感器、FPGA及高速舵机的目标跟踪系统,通过SPI总线对图像传感器的寄存器进行配置,使CMOS图像传感器在像素分辨率为640×480时帧频可达250 fps。采用流水线方式进行图像采集、动态阈值分割目标、目标形心跟踪、二维云台跟踪控制等,能够满足高帧频图像处理需求,提高了系统的跟踪精度。