多协议智能快充电路的设计

刘有耀 崔盼 张烨晨

摘要:为了提高充电速度,解决电子产品充电协议不兼容的问题,提出一款基于USB Type-C接口的多协议智能快充电路,可同时兼容PD和QC 2.0协议,最大耐压值为40 V。使用软硬件结合的方式,通过Verilog HDL硬件描述语言完成物理层的设计;用软件语言完成协议层的设计,从而用搭载USB Type-C接口的适配器可为使用多种不同协议的终端设备快充。通过仿真测试,结果表明多协议智能快充电路可实现不同快充协议间的切换,且能达到对应协议支持的最大充电功率,从源头上降低了各种充电线缆的产生。

关键词:智能快充;多协议;USB Type-C接口;电路设计;仿真测试;FPGA验证

中图分类号:TN402-34

文献标识码:A

文章编号:1004-373X( 2019) 24-0025 -05

0 引言

USB-IF( USB Implementers Forum)组织提出的USBType-C接口[1]已成为主流接口,其具有正反可插、供电性强和兼容性佳等优点。目前,华为的P9、MATE9,小米4,乐视等很多手机接口都使用Type-C接口,但搭载Type-C接口的手机只有使用官方标配的适配器才可实现快充,比如使用华为的P9适配器给同样具有Type-C接口的小米4手机充电时,只能实现普通充电,并不能达到小米4手机所要求的快充。这是因为华为适配器和小米4手机分别采用不同的快充协议,再加上市面上的快充协议更多,为了实现手机快充,适配器目前还不能达到通用的地步。直至USB-IF组织发布了USB PD 3.0协议[2],该协议支持PPS( Programmable Power Supply)充电,且与USB Type-C接口的结合可支持高达20 V/5 A的标准电力传输[3],这样便把市面上不同的快充标准统一在USB PD 3.0的范畴,即只要符合USB PD 3.0的充电器和终端都可以兼容[4]。因此研究基于USB Type-C接口的多协议智能快充电路不仅可以统一快充标准而且还有巨大的市场前景[5]。

本文设计的多协议智能快充电路基于Type-C接口实现,其中PD 3.0部分使用Verilog HDL硬件描述语言完成PD控制器的设计,使用软件语言完成PD协议层的设计,QC 2.0协议使用软件实现,最终通过SOURCE端(供电器如适配器)和采用PD 3.0或QC 2.0的SINK端(消耗端,如手机)进行数据交流,从而可为SINK端提供适合快充的电压和电流。该电路克服了市场上适配器无法通用快充的弊端,且电路成本低,扩展性强。1 PD 3.0快充电路总体结构

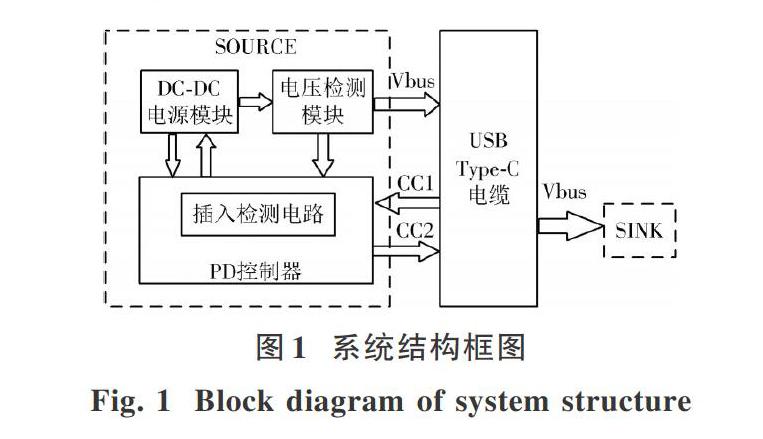

本文设计的多协议智能快充电路中的PD 3.0部分的结构主要包含三部分,分别为SOURCE端、电缆部分和SINK端,其结构框图如图1所示。

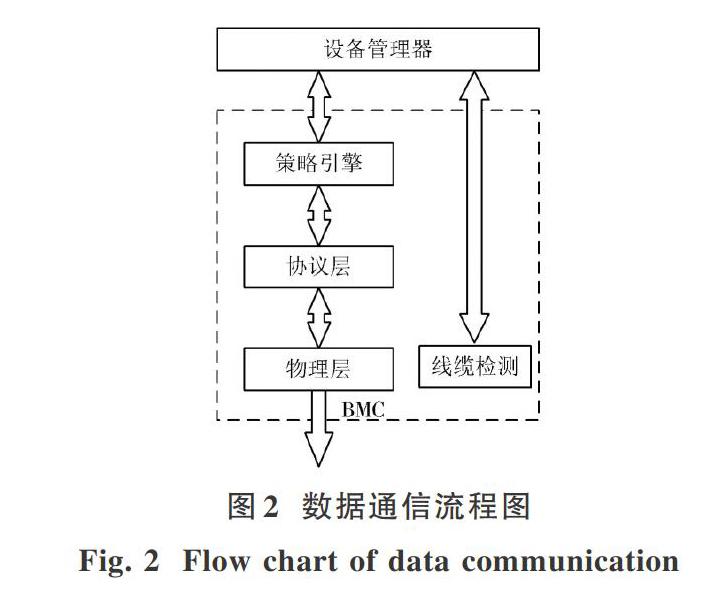

设计重点主要集中在SOURCE端,其端主要包括DC-DC电源模块、电压检测模块和PD控制器三部分。PD控制器即物理层的设计先使用Verilog HDL硬件描述语言完成设计,之后将硬件描述语言对应的jic文件下载到Alter Cyclone IV EP4CE6E22C8N FPGA仿真器,再使用软件开发协议层,其中整个数据通信流程如图2所示。

设备管理器用来获取能量供给能力、端口额定电流和判断插入设备是否为PD设备,相当于该系统的控制中心[6]。

线缆检测主要功能是检测USB Type-C线缆所能传递的电压电流信息。策略引擎提示协议层生成原始数据包,然后发送给物理层,之后在物理层中添加PRE,SOP*,CRC,EOP,并且进行485B编码和BMC编码,再将编码后的数据传输到CC线上[7],以此来进行数据的交互实现快充,且策略引擎可直接与设备管理器进行交流。为了确保执行当前的协议,当设备管理器发生更改时,策略引擎也将随之发生改变[8]。

总体来说,整个SOURCE端系统可分为硬件设计和软件设计两部分。

2 硬件电路设计

系统硬件设计主要包括PD控制器设计、插入检测电路设计、DC-DC电源模块设计和电压检测模块设计四部分。

2.1 PD控制器的设计

PD控制器主要包括发送机设计和接收机设计,其主要作用是负责数據接收、发送和协议处理。

由于本设计是基于USB Type-C接口的,为了增强抗干扰能力并均衡直流分量,发送数据时,物理层先使用485B编码对数据进行转换,再使用BMC编码对数据流进行二次转换,最终将信号传输到CC线上[9],接收过程和发送过程相反,具体流程如图3所示。

2.1.1 发送机设计模块

发送机的设计总框图如图4所示。在该设计中,物理层接收来自协议层的初始数据包,为其添加PRE,SOP,EOP等部分,然后将这三个部分通过BMCTH和BMCTL寄存器传输到tx—state状态机,将head和data部分传送给CRC32模块进行校验,将校验后的值通过BMCT4T5[7:0]寄存器传输到485B编码模块。通过编码后,将数据包存放在BMCBUF寄存器中,之后再传输给状态机,在图4中的两个状态机分别为控制发送数据的tx—state和控制BMC编码状态的mc_state。tx_state的状态有6种,分别为TX- IDLE,TX_WAIT,TX_SYNC,TX_DLY,TX_OK,TX_BUF,经过条件判断,最后输出数据存放在TX_BUF中,然后将TX_BUF寄存器中的值按位传输到mc_state状态机中进行BMC编码。mc_state的状态有5种,分别为MC_IDLE,MC_00,MC- 10,MC_11,MC_01,由于BMC编码的规则为如果数据为“0”则保持,如果为“1”则反转,那么MC_00和MC_ 11为数据不反转的情况,MC_10和MC_01为数据反转的情况,通过两个状态机的相互工作,最终输出编码后的数据为pdtx_data,此时若满足CCIEN=1或CC2EN=1的条件,那么最终输出的数据为dig2alg_pdtxl_data或者dig2alg_pdtx2_data,这些数据将会被将传输到CC信道。

在本设计中采用MCTRO和MCPRO作为接收和发送波特率控制,发送和接收时间分别设定不同波特率进行数据发送和接收,标准时间设置为300 kHz。波特率由MCPRO决定,比如FCPU是20 MHz,MCPR0=20 MHz÷300 kHz-1≈66,所以MCPRO填入66,采样波特率由MCTCON中MSAMPLE[5:0]決定,数值为20 MHz÷300 kHz÷4≈16。

1) CRC模块

CRC即循环冗余校验码,其作用是为了防止协议层生成的数据在传输过程中受到损坏或者丢失,因此对数据包的Message Header和数据部分进行了CRC数据保护,计算完CRC之后,通过EOP来进行包结尾标识,如果CRC校验不对,则整个包将会被丢弃,如果CRC校验正确,则整个数据包将会被传到协议层。

2) 485B编码模块

为了提高编码效率,采用485B编码,485B编码是用5 bit的二进制码来代表4 bit二进制码。此编码的效率是80%,比Manchester( 50%)码高。以SOP—CAP包为例,首先使能接收信号和CCI信号,由上可知只对head-er,data和crc32这三部分进行485B编码。其中,header部分配置为11al,data部分数据为00019121( SV3A),经过crc32计算后的值为312c3eda,经过编码后的值传输到bmcbuf[7:0]寄存器中。

3) BMC编码模块

由于本设计是使用USB Type-C接口中的CC线来传递信息,而在CC信道上传递数据时,为了确保数据DC的平衡,必须要经过BMC编码。此码是一种单向通信编码,数据1的传输需要有一次高低电平的转换,数据0的传输则是固定的高电平或者低电平。

2.1.2 接收机设计模块

接收机的设计框图如图5所示。第一步先进行BMC解码,其次由于数据发送时是按位发送的,最低位最先发送,那么接收时是先接收到最低位,所以需要对解码后的数据进行顺序的颠倒,即最低位放到最高位上,经过倒序后的数据为bmcr5b[4:0]。之后将进入pd_state状态机进行数据包的拆包,与此同时还会进行SB4B解码。

1) BMC解码模块

由于在CC线上传输都要经过BMC编码,因此接收部分需要首先对数据进行BMC解码。来自CC1信道的数据为alg2dig_pdrxl_data,来自CC2信道的数据为alg2 dig_pdrx2_data,只有在使能信号CCIEN=1或者CC2EN=I的情况下,数据才可以正确接收,接收到的可处理的数据为bmcr_ccdat,经过BMC编码模块输出的数据为bmcr_sdat[1:0],其中解码的波特率与发送模块中BMC编码的波特率一致。

2) pd_state状态机模块

pd_state状态机主要是对BMC解码后的数据包进行拆包,将依次解出PRE,SOP,DATA和EOP,按照解包顺序,当解完前导码时会产生一个sync64_flag标志位,解完SOP时会产生三个syncl_flag标志位和一个sync2_flag标志位,依此类推,当产生eop_flag标志位时代表该数据包解包完毕。该状态机总共有7个状态,分别为IDLE,WAIT.SFIRST.SYN64, SYNI, DATA和EOP。

3) 584B解码和CRC校验模块

由于在发送模块中只对head和data部分进行了485B编码和CRC校验,那么在接收数据时就只需对这分两个部进行584B解码和CRC校验,因此将数据包分为两部分。PRE,SOP和EOP通过运算模块输出,head和data部分进行584B解码,将解码后的数据发送给CRC校验模块,如果新旧CRC计算值相同,则说明数据接收成功,如果CRC计算值不同,说明校验错误,那么整个数据包将被丢弃。

2.2 插入检测电路的设计

由于USB Type-C接口可正反插,所以需要设计CCl&CC2插入检测模块,使用OPI和OP2,利用DACO设定检测电压,具体做法是CC1和CC2两端默认上拉电压都是3.3 V,一旦有外设接人,那么CC1或CC2的电压就会被拉低。通过与预设的电压比较器进行比较,如果CCl PLUG被拉低,则可判断出CC1被接人;同理,如果CC2 PLUG被拉低,则可判断出CC2被接人。

2.3 DC-DC电源模块的设计

USB Type-C接口支持的电压范围为0-20 V,其中以50 mV的幅度逐渐递增,支持的电流范围为0-5 A,以10 mA的幅度逐渐递增。本设计的电源模块电路图如图6所示,具体的调压做法是:FPGA通过SPI控制DAC,DAC的输出通过运放控制恒流源最终控制FB上的电流,抽掉FB上不同的电流则相应的电压Vout就会按照比例增加,从而达到升压的过程。

2.4 电压检测模块的设计

在经过上述调节之后,电压达到了终端需求的数值,但是为了确保终端设备的充电安全,本设计通过SPI采集ADC128S022的方式采集最终的电压数值,最终通过Vbus将电压输出到SINK端。

3 软件设计

3.1 通信协议的设计

系统软件部分设计主要包括PD协议层和QC 2.0协议的设计。两个协议都对应不同的数据格式以及编码原理,其中USB PD数据包主要由preamble(数据长度为64 bit),SOP(数据长度为20 bit),Message Header(数据长度为16 bit),data,CRC(数据长度为40 bit)和EOP(数据长度为5 bit)组成。数据类型有两种分别为控制信息和数据信息,当信息为控制信息时,该数据包由Message Header和CRC组成;当信息为数据信息时,该信息由Message Header和一个或者多个Data Objects组成。其中Data Objects的格式是由Message Header里面的Message Type定义的,其总共有四种消息格式分别为:PDO (Power Data Object), RDO (Request Data Ob-ject), BDO( BIST Data Object), VDO (Vendor DefinedData Object)。供电就是通过包含有电流电压性能的PDO实现的。

3.2 程序设计

针对基于PD 3.0协议的快充来说,硬件部分主要实现485B编码、BMC编码和CRC校验,软件部分通过数据包格式构造数据包和配置相应的寄存器来实现数据包的通信。其中,需要构造SRC_CAP,GoodCRC,Re-quest, GoodCRC, Accept, GoodCRC, PS_RDY和GoodCRC等8個数据包的模块,通过自定义的PD_C harge函数调用各个数据包模块,再使用maln.c调用PD_Charge函数来实现最终的PD通信。

4 FPGA验证

4.1 PD控制器仿真

本部分使用VCS作为仿真工具,Novas公司的Verdi作为Debug工具,对PD控制器进行功能仿真。其中能量协商过程中SOURCE端到SINK端5个步骤分别为:

1) SOURCE端提供它的能力数据信息(SRC_CAP);

2) SINK端收到能力数据并且从SOURCE端提供的能力数据信息中选出适当的电源配置参数并发出GoodCRC和相应的请求(Request);

3) SOURCE端接收请求并且回复GoodCRC和Ac-cept;

4) SOURCE端将总线电压修改成相应的参数并且向SINK端发PS_RDY表示功能准备完成;

5) SINK端接收电压,充电协商过程完成,开始充电。当SINK端希望总线电压降低的时候,同样的通信过程也会发生。

图7为数据交流仿真图,图中的8个数据包依次为SRC_CAP, GoodCRC, Request, GoodCRC, Accept, Cood-CRC,PS_RDY和GoodCRC。

由于每个数据包具体内容繁琐,信号量大,故在此就不再将各个数据包内容呈现。

4.2 系统验证

FPGA验证平台如图8所示,其由Alter Cyclone IVEP4CE6E22C8N FPGA仿真器、USB PD协议测试仪(POWER-Z)和手机组成。将软件程序对应的hex文件下载到仿真器,则仿真器相当于SOURCE端,手机则为SINK端。

通过给iPhone X充电进行验证,iPhone X内部支持USB PD 3.0协议,但官方配置仍是传统的5 V/1 A适配器,其快充潜能没有发挥出来,通过本设计可以使得充电电压电流达到9 V/2 A,实现快充。其中,SOURCE端和SINK端数据相互交流,利用PD分析仪将数据包解析出来并且用示波器抓取Vbus上电压变化过程,如图9所示。

由图9可以观测到,SOURCE端(SRCI电源)与SINK端(SNKI终端)的协商过程以及电源的供电能力。首先SOURCE端发送5个供电能力包,SINK端正确接收后回复GOODCRC,并且发送请求数据包,此时请求的电压电流5 V/3 A为系统默认的电压电流;SOURCE端收到请求数据包后回复GOODCRC,并且接收请求,等待大约2s,SINK端开始请求9 V/2 A;SOURCE端收到请求数据包后回复GOODCRC包,并且接收请求,将电压电流调整到9 V/2 A,到此协商过程结束,充电开始。之后采用QC 2.0协议进行快充时,用示波器抓取的升压波形如图10所示。电压默认初始值为SV,之后通过数据协商电压上升到9V,最终实现快充。

5 结语

本文提出一种基于Type-C接口的多协议快充电路,通过SOURCE端和SINK端数据交流实现了快充。最后对整个系统进行了FPGA验证,结果满足设计要求。在众多的快充产品中,该设计使用软硬件结合的方式不仅简化了电路,降低了成本,还实现了多协议快充,使得搭载USB Type-C接口的适配器可为采用PD 3.0和QC 2.0协议的手机快充,克服了市场上适配器无法通用快充的弊端,后期还可根据需要增加多种协议,具有极大的扩展性,且电路成本低,未来市场广阔。

参考文献

[1] USB-IF. USB Type-C cable and connector specification release1.3[M].[S.1]:USB-IF, 2017.

[2] USB Implementers Forum. Universal serial bus power deliveryspecification [S]. Rev 3.0.[S_1.]:USB-IF. 2017.

[3] DUNSTAN Bob. Universal serial bus power delivery specifica-tion [M]. Revision 3.0.[S.1]:USB Implementers Forum, 2017.

[4] Conpaq Hewlett-packard. Universal serial bus specification [M].Revision 2.0.[Sll]:USB Implementers Forum. 2000.

[5]李勇.USB PD在移动设备快速充电中的新兴应用[J].电子产品世界,2018.25(9):27-30.

LI Yong. USB PD emerging application in mobile equipmentquick charge [J]. Journal of electronics world, 2018, 25(9):27-30.

[6]李生辉.基于Type-C接口的USB PD协议的设计与实现[D].西安:西安电子科技大学,2017.

LI Shenghui. The design and realization of the Type-C interfaceof USB PD agreement [D]. Xi' an: Xidian University, 2017.

[7]俞德军.基于USB TYPE-C协议的大功率智能电源技术研究[D].成都:电子科技大学,2018.

YU Dejun. Based on the USB TYPE-C protocol of high-powerintelligent power technology research [D]. Chengdu: Universityof Electronic Science and Technology of China, 2018.

[8]惠惠,支持快充协议的充电接口芯片XD952的研究与设计[D].西安:西安电子科技大学,2017.

HUI Hui. Support quick charge agreement charging the re-search and design of the interface chip XD952 [D]. Xi' an: Xid-ian University.2017.

[9]欧阳联铂.USB Type-C接口显示器特性及其验证要点[J]电子技术与软件工程.2017( 15):90-91.OUYANG Lianbo. USB Type-C interface display features andprocess validation [J]. Journal of electronic technology and soft-ware engineering, 2017( 15): 90-91.

[10]马献武,基于IMS架构多协议信令网关研究与实现[D],西安:西安电子科技大学,2018.

MA Xianwu. Research and implementation of multi-protocolsignaling gatewav based on IMS architecture [D]. Xi' an: Xidi-an University 2018.

作者简介:刘有耀(1975-),男,陕西榆林人,教授,研究方向為集成电路设计。

崔盼(1994-),女,陕西西安人,硕士,研究方向为电路与系统。

张烨晨(1993-),男,陕西渭南人,硕士,研究方向为电路与系统。