基于FPGA的LED点阵显示控制方法

蒋中荣 甘俊杰 欧伟明

摘 要:为了研制基于FPGA的LED点阵显示系统,文中论述显示系统的硬件设计方案,给出16x16 LED点阵与FPGA芯片的接口电路,详细介绍FPGA的基于IP核的设计方法。显示数据存放在FPGA片内,其内部的控制逻辑单元与ROM存储器分别进行设计,很方便地实现了22个字符的左移动态扫描显示。充分利用了FPGA运行速度快、I/O引脚多、设计灵活的特点,该文提出的LED点阵显示控制方法具有较好的实际应用价值。

关键词:LED;点阵显示;硬件设计;动态扫描;存储机制;硬件调试

中图分类号:TN873.3-34

文献标识码:A

文章编号:1004-373X(2019)24-0016-04

0 引言

随着科学技术的发展进步,现场可编程门阵列(Field Programmable Gate Array,FPGA)作为嵌入式的一种,被广泛应用于各个领域[1-2]。FPGA拥有丰富的硬件资源,具有较强的可重配置能力和灵活的设计方式,已经成为嵌入式系统设计的主流硬件平台之一。与数字信号处理器(Digital Signal Processor,DSP)相比,FPGA能够实现数字信号处理算法硬件流水或复杂的数字控制,可以满足高速数字控制和硬件系统高度集成化的需求;与单片机( Micro-Controller Unit,MCU)或者是ARM相比[3-4],FPGA具有更丰富的I/0引脚和更高速的性能,并且FPGA是纯硬件电路实现,工作时没有CPU程序运行,从而可以提高系统可靠性和工作速度。

LED点阵显示屏是随着计算机技术、半导体微电子技术、光电子技术的迅猛发展而形成的一种新型信息显示媒体,它利用发光二极管构成的点阵模块或像素单元组成可变面积的显示屏幕,以可靠性高、使用寿命长、环境适应能力强、性价比高、使用成本低等特點,迅速成长为平板显示的主流产品,在信息显示领域得到了广泛的应用[5-10l。近几年有关LED点阵显示屏的研究论文,主要基于MCU和ARM实现[3-4],存在运行速度慢、控制单元与LED点阵显示屏的接口电路复杂等不足。本文研究基于FPGA的LED点阵显示控制方法,充分利用FPGA运行速度快、I/0引脚多、设计灵活的特点,以FPGA控制16x16 LED点阵实现左移字符串显示为例,介绍系统的整体结构、FPGA芯片与LED点阵的接口电路、FPGA基于IP核的设计方法。

1 系统硬件设计方案

1.1 系统整体结构图

基于FPGA的LED点阵字符和图像显示系统,由FPGA和LED点阵两部分组成,如图1所示。FPGA向LED点阵发送显示数据和扫描信号,控制LED点阵的工作,实现字符和图像的显示。

FPGA芯片内部由3个单元电路组成:时钟逻辑单元产生起同步作用的系统时钟脉冲信号;存储器ROM单元用于存放显示数据,是基于FPGA的IP核而实现的,其中的显示数据决定于所显示的内容,显示内容包括字符或者图像;控制逻辑单元产生读取存储器ROM的地址信号和控制LED点阵的扫描信号,是基于FPGA的文本设计输入方法实现的,如何完成其设计取决于LED点阵的显示内容和显示方式,LED点阵的显示方式分为静态显示和移动显示。

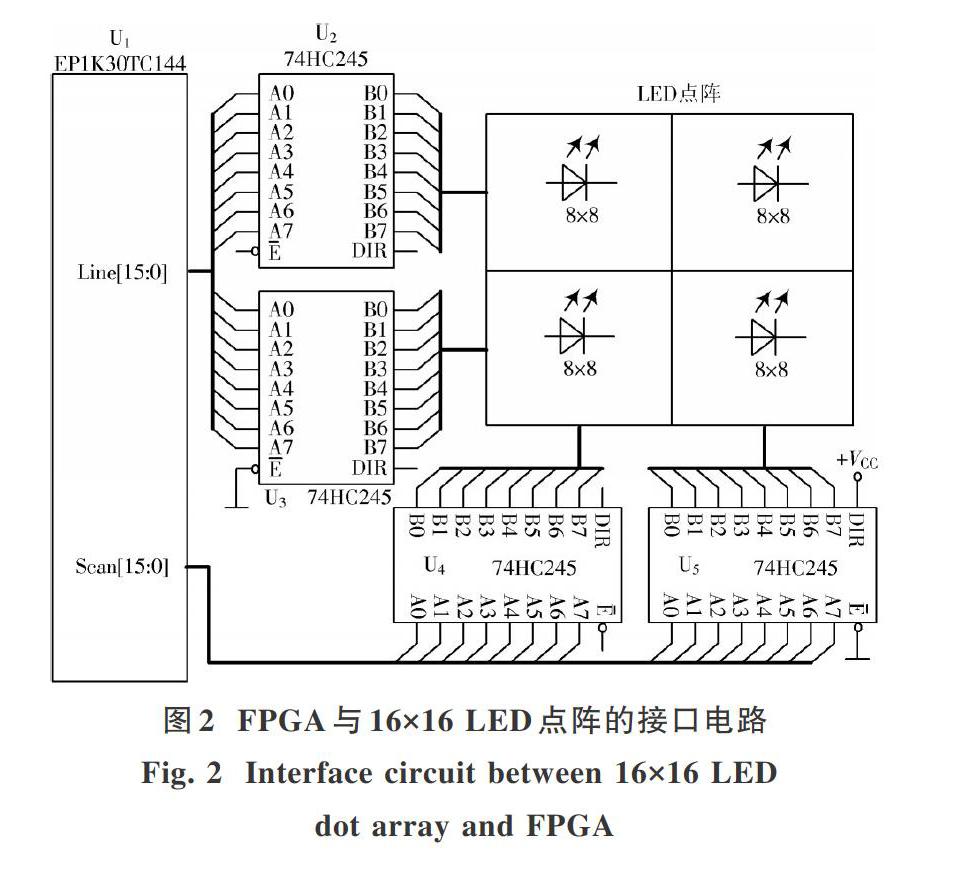

1.2 FPGA与LED点阵的接口电路

一般而言,LED点阵采用低电压扫描控制方式来完成显示,为了叙述的方便,本文采用16x16 LED点阵,并且采用列扫描控制方式。FPGA芯片与16x16 LED点阵的接口电路如图2所示,U1是FPGA芯片,其型号为EPIK30TC144;U2-U3是8 bit总线驱动器,其型号为74HC245;16x16 LED点阵是由4块8x8 LED点阵模块拼接而成的。需要说明一下,本文选用的8x8 LED点阵模块是行共阳、列共阴的。

由图2可知,接口电路由4片总线驱动器U2-U5组成,其中,U2和U3接收FPGA提供的行显示数据Line[15:0],并控制16x16 LED点阵的16行,行显示数据是高电平有效;U4和U5接收FPGA提供的列扫描信号Scan[15:0],并控制16x16 LED点阵的16列,列扫描信号是低电平有效。

芯片U2和U3的每一个输出引脚,最多提供1个发光二极管的阳极电流,所以U2和U3的驱动能力是足够的。芯片U4和U5的每一个输出引脚,最多提供16个发光二极管的阴极电流之和,U4和U5的驱动能力也是足够的,但是当LED点阵显示屏增大时,需要提供的最大阴极电流之和随之增大,这时U4和U5的驱动能力不足,这种情况下可以在U4和U5的输出端添加达林顿晶体管来满

图2所示接口电路的特点是,在每一个时钟周期,在FPGA提供列扫描信号Scan[15:0]的同时,行显示数据Line[15:0]也送到了LED点阵的行引脚,无论是行显示数据,还是列扫描信号,FPGA是直接送达LED点阵引脚的,不需要FPGA外部芯片进行串并转换和地址译码,因此,充分发挥了FPGA芯片的运行速度快和1/0引脚多的特点,即使LED点阵显示屏增大时,接口电路也只是增加8 bit总线驱动器和达林顿晶体管,从而简化了接口电路,完全能够保证LED点阵显示屏的刷新率和显示亮度。

2 FPGA片内逻辑电路的设计

2.1 FPGA芯片内部电路框图

由图1可知,FPGA芯片内部由3个单元电路组成:时钟逻辑单元、存储器ROM单元和控制逻辑单元。FPGA片内逻辑电路的设计,是在FPGA开发环境Quar-tusⅡ下完成的,时钟逻辑单元的设计很简单,下面主要介绍控制逻辑单元、存储器ROM单元的设计方法。

2.2 控制逻辑单元设计方法

如何完成控制逻辑单元的设计,取决于LED点阵的显示内容和显示方式,为了叙述的方便,拟定显示内容为字符串,显示方式为左移动态扫描显示方式。因此,控制逻辑单元的功能是:产生读取存储器ROM的地址信号;产生LED点阵的列扫描信号。使用FPGA的VHDL硬件描述语言文本设计输入方法,完成控制逻辑单元的设计,VHDL程序关键代码如下:

Entity ControILogic is

Port(

clk:in std_logic;

//1 kHz,同步时钟信号

ROM_Addr: out std_logic_vector(9 downto O) ;

//ROM地址信号

Scan : out std_logic_vector( 15 downto O )

//LED点阵列扫描信n号 );End Entity ControlLogic ;Architecture Artl of ControlLogic is Signal counter : std_logic_vector( 3 downto O) : = B"II11" ; Signal f_slow : std_logic ; Signal x: natural range O t0 287 := O; Signal y: natural range O t0 271 := O;

//271=287-16 , y控制左移Begin ROM_Addr <= conv_std_logic_vector( x , 10) ;

//存儲器 ROM的地址信号pl : Process ( clk) Begin if rising_edge(clk) then

if counter = B"OOOO" then

counter <= B"11lI";

else

counter <= counter- I ;

end if; end if; End Process pl ;p2 : Process( clk)

//256分频器 Variable tmp: natural range O t0 255; Begin if rising_edge( clk) then

if (tmp=10#255#) then

tmp := O;

else

tmp := tmp +1;

end if; end if; End Process p2 ;p3 :

Process ( f_slow )

//y控制左移 Begin if rising_edge ( f_slow ) then

if (y=10#271#) then

else

end if; end if; End Process p3 ;p4 : Process ( counter)

//产生列扫描信n号 Begin Scan <= ( others => ' I ' ) ; case counter is

when B"0000" => Scan(0) <= 'O' ;

when B"0001I" => Scan( 1) <= 'O' ;

when B"O010"=> Scan(2)<='O';

when B"0011"=>Scan(3)<='0':

when B"0100"=>Scan(4) <='O':

when B"0101"=>Scan(5)<='O':

when B"0110"=>Scan(6)<='O';

when B."0111"=>Scan(7)<='0':

when B"1000"=>Scan(8)<='0':

when B"1001"=>Scan(9)<='0';

when B"1010"=>Scan(10)<='0':

when B."1011""=>Scan(11)<='O,:

when B"1100『t=>Scan(12)<='0,;

when B"1101"=> Scan( 13)<='0':

when B"111101t=>Scan(14)<='0';

when B"1111.t=>Scan( 15)<='0':

when others=>Scan<=(others=>1):

end case:

End Process p4;

End Artl;

2.3 创建只读存储器初始化数据文件

在FPGA芯片内部开发的存储器ROM单元用于存放显示数据,其中的显示数据决定于所显示的内容,首先根据显示内容变换成显示数据,再由显示数据创建只读存储器的初始化数据文件。

显示内容变换成显示数据的过程,是在取字模数据软件中完成的。例如,取字模数据的软件有“PC-toLCD2002完美版”,其是一个绿色软件。文章前面已述及,显示内容为字符串“欧伟明指导数字系统设计2018年11月28日”,在取字模数据的软件PCtoLCD2002完美版中,可以很方便地获取字符串对应的字模数据(即显示数据),当然也可以很方便地获取显示内容为图像的字模数据。

根据得到的字模数据(即显示数据),在开发环境QuartusⅡ中,就可以创建只读存储器的初始化数据文件ROM_data.mif.只要将字模数据拷贝到ROM_data.mif文件中即可。

2.4 创建只读存储器

本文在FPGA芯片内部实现存储器ROM单元的设计,是基于FPGA的免费IP核而实现的。在开发环境QuartusⅡ中,利用开发商提供的免费IP核,设计了一个包含1 024个字,字长为16 bit的只读存储器ROM_1024_ 16。需要提醒的是,在设计过程中,要选中前面已经创建好的只读存储器初始化数据文件ROM_data.mif这样就很方便地在FPGA芯片中,完成了存储单元中存放有显示数据的只读存储器ROM_1024_16的设计。

3 硬件调试结果

为了验证本文所讨论的LED点阵显示系统实际效果,本文按照图2所示电路,制作了基于FPGA的16x16LED点阵显示系统,实现了在16x16 LED点阵上,向左移动显示由22个字符组成的字符串“欧伟明指導数字系统设计2018年11月28日”。调试结果表明,LED点阵显示稳定、清晰、亮度适中、无闪烁感,如果改变控制逻辑单元的时钟脉冲频率,就可以改变字符串向左移动显示的速度。硬件调试效果如图3所示。

3.1 硬件系统结构特点

对于采用MCU或ARM的LED点阵显示系统而言[3-4],由MCU或ARM发送的显示数据一般是串行传送给具有锁存功能的移位寄存器,比如8 bit的移位寄存器74HC595,如果要将一个8 bit的显示数据送到74HC595芯片,就需要8个时钟周期。然而一屏完整的显示数据往往是远大于8 bit,所以就需要更多的时钟周期;而且移位寄存器中的显示数据送达LED点阵,是在锁存时钟脉冲信号控制下完成的,所以还需要一个时钟周期,因此,这样严重制约了系统的整体工作速度,并影响LED点阵显示屏的刷新率和显示亮度。本研究的硬件系统主要由FPGA,LED点阵及其驱动器74HC245组成,结构非常简单。由于采用FPGA芯片,一屏完整的显示数据并行地由FPGA发送给驱动器74HC245,经其驱动后送达LED点阵,只需要一个时钟周期。

3.2 FPGA的设计灵活性

系统中的FPGA芯片内部电路结构清晰且结构简单,FPGA芯片内部电路的设计,是在开发环境QuartusⅡ下完成的,控制逻辑单元的设计采用VHDL硬件描述语言,可以利用VHDL语言很强的行为描述能力,从而实现复杂的数字控制算法。存储器ROM单元的设计采用基于FPGA的IP核设计方法,这样可以简化设计过程,很容易获得任意字长、包括任意多个字的只读存储器,并将显示数据以初始化文件的方式融合到存储器ROM单元的创建过程中。另外,设计完成后,FPGA是纯硬件电路,工作时没有CPU程序运行,从而可以提高系统可靠性和稳定性。

4 结论

本文以16x16 LED点阵为例,论述了基于FPGA的LED点阵显示控制方法。实验结果对于本技术领域的技术人员而言,很容易将这种控制方法用于更大的LED点阵。实验结果表明本文介绍的基于FPGA的LED点阵显示控制方法,充分利用了FPGA运行速度快、1/0引脚多、设计灵活的特点,具有较好的实际应用价值。

注:本文通讯作者为欧伟明。

参考文献

[1]欧伟明,聂辉,李圣清.基于FPGA的机械抖动测量方法[J]核电子学与探测技术,2014,34(8):998-1001.

OU Weiming, NIE Hui, LI Shengqing. Measurement methodof mechanical dither based on FPGA [J]. Nuclear electronics&detection technology, 2014. 34(8): 998-1001.

[2]李锐,田帆,邓贤君,等.基于FPGA的全数字延时锁相环的设计[J]现代电子技术,2019,42(6):69-75.

LI Rui, TIAN Fan. DENG Xianjun, et al.Design of all-digitaldelay-locked loop based on FPGA [J]. Modern electronics tech-nique, 2019, 42(6): 69-75.

[3]欧伟明,刘欢,李圣清.燃弧时间传感器的研制[J]电子测量与仪器学报,2014,28(4):441-446.

OU Weiming, LIU Huan. LI Shengqing. Development of anarc time sensor [J]. Journal of electronic measurement and in-strument. 2014. 28(4): 441-446.

[4]张学成.基于电力线载波模块的LED点阵图文显示系统[J]液晶与显示,2011,26(3):350-353.

ZHANG Xuecheng. LED dot matrix graphics and text displaysystem based on power line carrier module [J]. Chinese journalof liquid crystals and displays, 2011. 26(3): 350-353.

[5]郑争兵.基于FPGA的图形点阵液晶显示系统设计与实现[J]液晶与显示,2013,28(3):403-407.

ZHENG Zhengbing. Design and implementation of graphic dotmatrix LCD display system based on FPGA [J]. Chinese journalof liquid crystals and displays, 2013, 28(3): 403-407.

[6]朱晓青,马定寰,李圣清,等,于BP神经网络的微电网蓄电池荷电状态估计[J].电子测量与仪器学报,2017,31(12):2042-2048.

ZHU Xiaoqing, MA Dinghuan, LI Shengqing, et al.Estima-tion of state of charge for micro-grid battery based on BP neu-ral network[J].Journal of electronic measurement and instru-ment, 2017. 31(12): 2042-2048.

[7]袁谦,黄波,张多英,等,基于FPGA的可见光波段便携式光谱仪的设计[J],现代电子技术,2019.42(6):100-104.

YUAN Qian, HUANG Bo. ZHANG Duoying,et al.Design ofFPGA - based portable spectrometer working in visible lightband [J]. Modern electronics technique, 2019, 42 (6): 100-104.

[8]刘欢.基于FPGA的多路温度开关检测系统的设计[D].株洲:湖南工业大学,2015.

LIU Huan. Design of multichannel temperature switch detec-tion svstem based on FPGA [D]. Zhuzhou: Hunan University ofTechnology, 2015.

[9]歐伟明,聂辉,张婷,电气开关接点机械抖动次数的测量[J]电子测量与仪器学报,2014,28( 11):1268-1273.

OU Weiming, NIE Hui, ZHANG Ting. Measurement of themechanical dithering number of electric switch contact [J]. Jour-nal of electronic measurement and instrument, 2014, 28( 11):1268-1273.

[10]欧伟明,凌云,李圣清.基于同步串行通信的汽车TPMS低功耗设计[J]汽车安全与节能学报,2018,9(4):427-432.

OU Weiming, LING Yun. LI Shengqing. Low power consump-tion design of automobile TPMS based on synchronous serialcommunication [J]. Journal of automotive safety and energy,2018. 9(4):427-432.

作者简介:蒋中荣(1964-),男,副教授,主要研究方向为PLC控制技术与嵌入式系统应用。

欧伟明(1962-),男,硕士,教授,硕士生导师,主要研究方向为信号处理、嵌入式系统。