基于FPGA和TDC芯片的高精度时间间隔计数器研制

闫菲菲,马红皎,何在民,邢燕

(1.中国科学院 国家授时中心,西安 710600;2.中国科学院大学,北京 100049)

0 绪论

高精度时间间隔测量技术在原子物理实验、天文测量、激光测距及高精度无源定位中有着广泛应用,现已成为军事通信、卫星导航定位等领域中不可或缺的关键技术[1]。通常将测量精度高于1 ns的时间间隔测量称为精密时间间隔测量[2]。

实现高精度时间间隔测量的方法有很多,目前国内外普遍采用的有利用FPGA(field-programmable gate array)进行TDC(time-to-digital conversion)电路设计的方式,国外R.Szplet等人利用FPGA设计TDC电路得到LSB(least significant bit)为100~200 ps的系统[3];国内西安电子科技大学使用游标延迟线的设计方法,将FPGA内部布线资源作为延迟单元,实现了58 ps的测量分辨率和38 ps的RMS(root-mean-square)测量精度的TDC设计[4]。利用FPGA进行TDC设计周期短且研发成本低[5],但是,该方法需要大量的人力和精力调整芯片内部逻辑单元的布局,当TDC设置成多通道结构时工作量将成倍增加,而在一些应用场合实现多通道同时测量具有非常重要的意义。随着集成电路(integrated circuit,IC)技术的发展,使得利用IC实现TDC技术成为可能,利用成熟的ASIC芯片进行精密时间间隔测量装置的研制为很多科研人员采用[6]。

本文提出利用FPGA控制AMS公司的TDC-GPX2芯片,实现了一款4通道同时测量,测量精度达到60 ps,多次测量准确度优于60 ps,量程可达1.6 s的时间间隔计数器,该设备操作简单,使用灵活,可满足大多数场合应用。

1 时差测量原理

时间作为一个特殊的物理量,有其专门的测量方法,通常需要将流动的时间转化为可以观测的物理量来进行间接的测量[7]。例如,将时间信息转化为电信号进行精密的测量[8]。利用时间信息到电信号之间的转换来测量时间间隔有多种方式,常见的方式有直接计数法、时间内插法、时间放大法等等,实际使用中通常会将各种方法结合进行测量[9]。

1.1 经典测量原理

本文采用的TDC-GPX2芯片是利用“粗计数”和“细测量”相结合的方法进行测量[10]。“粗计数”就是直接对参考时钟进行计数,得到“粗”时间,这样可以得到更大的测量量程,但测量精度不够;“细测量”则是采用一定方法对“粗计数”测量不到的微小时间间隔进行测量,通常可以得到很好的测量精度,但测量量程难以提高[11]。两种方法结合使用则可以得到较大的测量量程和更好的测量精度[12]。“粗计数”和“细测量”方法相结合的测量原理如图1和图2所示。

图1 时间间隔测量的基本原理

如图1所示,待测时间间隔ΔT由两部分组成,一部分为“粗计数”部分TN,一部分为“细测量”部分Ti(Ti1和Ti2),计算用公式(1)表示:

ΔT=TN+Ti1-Ti2。

(1)

当“开始”有信号到来时,系统开启参考时钟计数器,开始测量,参考时钟周期开始计数。“结束”信号到来时,停止计数。此时可以由公式(2)来计算“粗计数”时间间隔TN:

TN=N×Tref。

(2)

“细测量”的测量原理如图2所示,本文介绍的“细测量”方法为抽头延迟线法。通过计算脉冲经过的延迟单元个数来进行时间间隔测量[13]。可以用公式(3)来计算,其中m为经过延迟单元个数,Δτ为每个延迟单元的延迟时间[14]。

Ti=m×Δτ。

(3)

1.2 本系统测量原理

系统测量的原理如图3所示,假设待测脉冲从通道1和2输入,假设通道1中信号先于通道2中信号到来,测量两通道输入信号之间的时间间隔[15]。

图3 系统测量原理

本系统测量时,输出两个结果参数,可分别作为“粗”计数结果和“细”测量结果[16]。上电后即开始参考时钟数N的计数,并作为结果参数之一,即“粗”计数结果输出;当通道1中有待测脉冲到来时,先将此时的参考时钟数N1锁存,然后对参考时钟进行实时测量,得到测量值Tref1,同时测量该脉冲与它前一个参考时钟脉冲之间的时间间隔Δt1,将两者的比值锁存并作为另一个结果参数ti,即“细”测量结果输出,最后进行计算时,根据系统所配置参考时钟分频系数,按照公式(4)进行计算,式中LSB为分频系数,测量前已设置好。根据公式(5)计算该脉冲到来的系统时刻Tsys1,其中T为参考脉冲周期[17]。通道2中另一个待测脉冲到来时利用同样的方法计算其系统时刻。对两脉冲的系统时刻做差,则得到两者之间的时间间隔ΔT,如公式(6)所示。

ti=Δt/Tref×LSB,

(4)

Tsys=N×T+ti/Tref,

(5)

ΔT=Tsys2-Tsys1

(6)

系统测量原理实质上和传统的“粗计数”和“细测量”相结合的方式原理是一致的:不同通道“细测量”测量结果ti即为公式(3)中的Ti,而不同通道“粗计数”测量结果N与参考时钟周期T相乘之后做差的结果即为公式(2)中的TN。但本系统采用做差的方法求得最终结果可以将不同通道测量结果中共同的误差项去除,从而有效减少公共误差对系统测量精度的影响[18]。

2 系统设计

本系统设计主要是由硬件设计和软件设计构成。硬件部分包括各个模块电路的设计和设计中需要注意的事项;软件部分主要是芯片配置时序的实现,各个接口逻辑设计以及数据流处理逻辑的设计等。

2.1 硬件设计

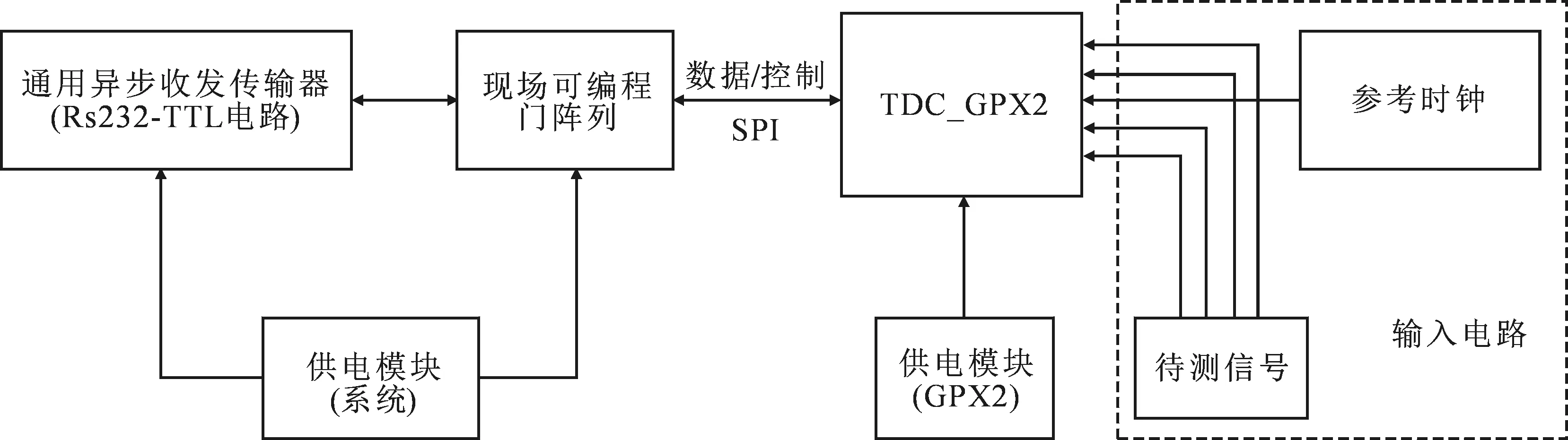

硬件设计主要包括时间间隔测量模块、处理器控制模块、串口通信模块、供电模块(系统、GPX2)和信号输入模块[19]。时间间隔测量模块由TDC-GPX2芯片及其外围电路构成。串口通信电路主要由电平转换电路构成。处理器控制模块是由FPGA芯片及其外围电路构成,用来实现芯片配置,功能选择等控制功能[20]。数据输入部分包括4个通道待测数据的输入以及参考时钟的输入,以实现多通道同时测量。电路设计示意图如图4所示。

图4 硬件系统框图

在进行硬件设计时,考虑TDC-GPX2是一个数字化芯片,利用门延迟来进行精密时间测量,应着重考虑减小门电路因受到环境影响而影响测量精度,因此设计中对芯片采用单独电源供电,并且在芯片各个引脚放置去耦电容来降低电压波动的影响。同时使用0.1 μF滤波电容来滤除传输线上的纹波。在数据输入部分,将SMA(sub-miniature-a)传输接头输入的信号经过10 Ω电阻滤波之后接入芯片的测量引脚。

2.2 软件设计

软件部分主要是实现FPGA控制逻辑设计,本系统的控制部分由Intel公司的Cyclone EP4CE6E22F17C8芯片实现,该款芯片资源丰富,可灵活实现各种控制和接口程序,完全可以在降低系统设计成本的基础上完善地实现各个模块的功能。

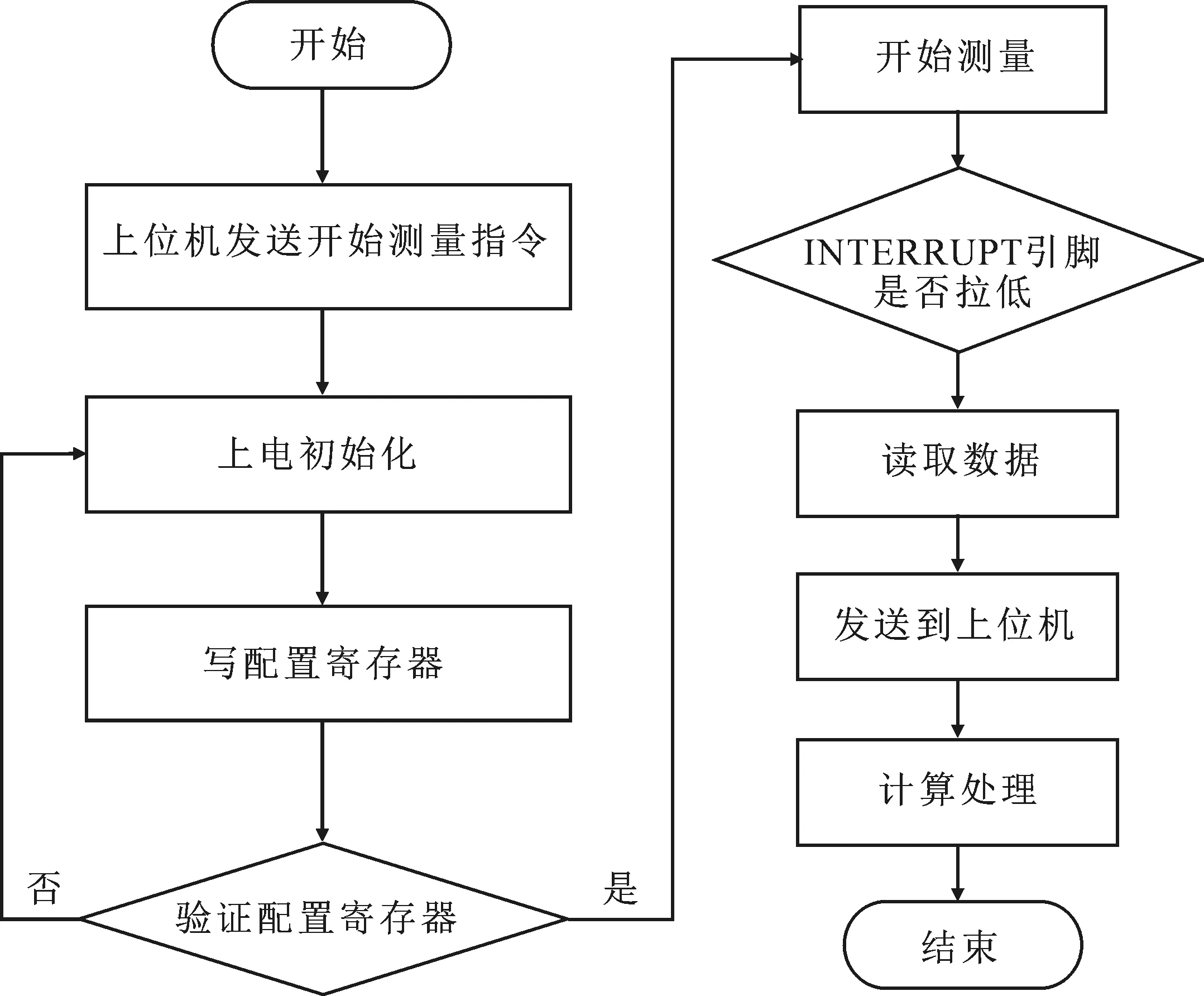

本系统FPGA设计部分使用Verilog语言编写,主要实现对整个测量过程的逻辑控制和各个接口的实现,其中最为关键的部分为测量流程的控制。本系统测量流程图如图5所示。

系统在进行测量前需要对TDC-GPX2芯片进行配置,配置步骤为:①上电复位;②写配置寄存器;③ 验证配置寄存器;④初始化并开始测量。

FPGA内部集成SPI接口对芯片进行配置,配置完成后开始测量,测量结果通过SPI接口发送到FPGA,FPGA利用FIFO(first input first output)对数据进行缓存,再通过串口将数据发送到上位机进行处理[21]。图6为FPGA内部各模块的RTL(register transfer level)连接图。

图5 计数器控制流程图

图6 FPGA内部逻辑RTL视图

3 实验结果及分析

本计数器的测试是按照图7所示的测试平台进行测试,将计数器测量结果和进口仪器SR620同步测量结果进行比对。使用国家授时中心钟房产生的10 MHz信号作为计数器和SR620时基参考信号,再将中国科学院国家授时中心钟房产生的1 PPS信号通过脉冲分配放大器,产生两路秒信号,通过三通分别送入SR620和计数器,再将三通另一输出端接入待测试延长线,延长线另一端分别接入SR620和计数器,测量结果都送入上位机进行处理[22]。

实验过程中,将参考时钟周期计数器位宽设置成24位,时钟分频系数设置成100 000(20 bit),在使用10 MHz参考时钟下可获得1 ps的分辨率(LSB,least significant bit),量程可达到1.6 s;另外设置系统接收参考时钟与4个通道的待测信号输入,各通道相互独立,采用CMOS电平接入,任意通道的结果缓存器有数据时开始读取测量结果。

3.1 通道时延标定

由于系统通过通道测量结果做差得到最终结果,所以需要对通道时延进行标定。本系统在设计时已充分考虑通道间的对称性并尽量使信号输入到芯片引脚距离最短,所以各通道的时延偏差应为皮秒量级。

图7 测试实验原理图

根据系统测量的原理设计通道时延标定方法:使用国家授时中心钟房的10 MHz作为参考时钟,1 PPS信号通过4根等长的线缆接入系统4个通道,记录4个通道的测量值。计算4个通道待测脉冲与其前一个时钟脉冲上升沿间的时间间隔,该间隔之间的差异即是由于通道时延引起的[23]。原理如图8所示。

图8 系统通道延迟标定原理

对实验结果统计后发现,通道1的结果均值为10.49 ns,通道2的结果均值为10.51 ns,通道3的结果均值为10.64 ns,通道4的结果均值为10.54 ns,通道时延引起的偏差可在具体测量中进行修正。

3.2 时间间隔测量结果分析

实验中计数器及SR620的误差通过平均绝对差来表征,测量精度通过标准偏差(A类不确定度)来表征[24]。平均绝对差以及标准偏差计算方法如公式(7)和(8)所示:

(7)

(8)

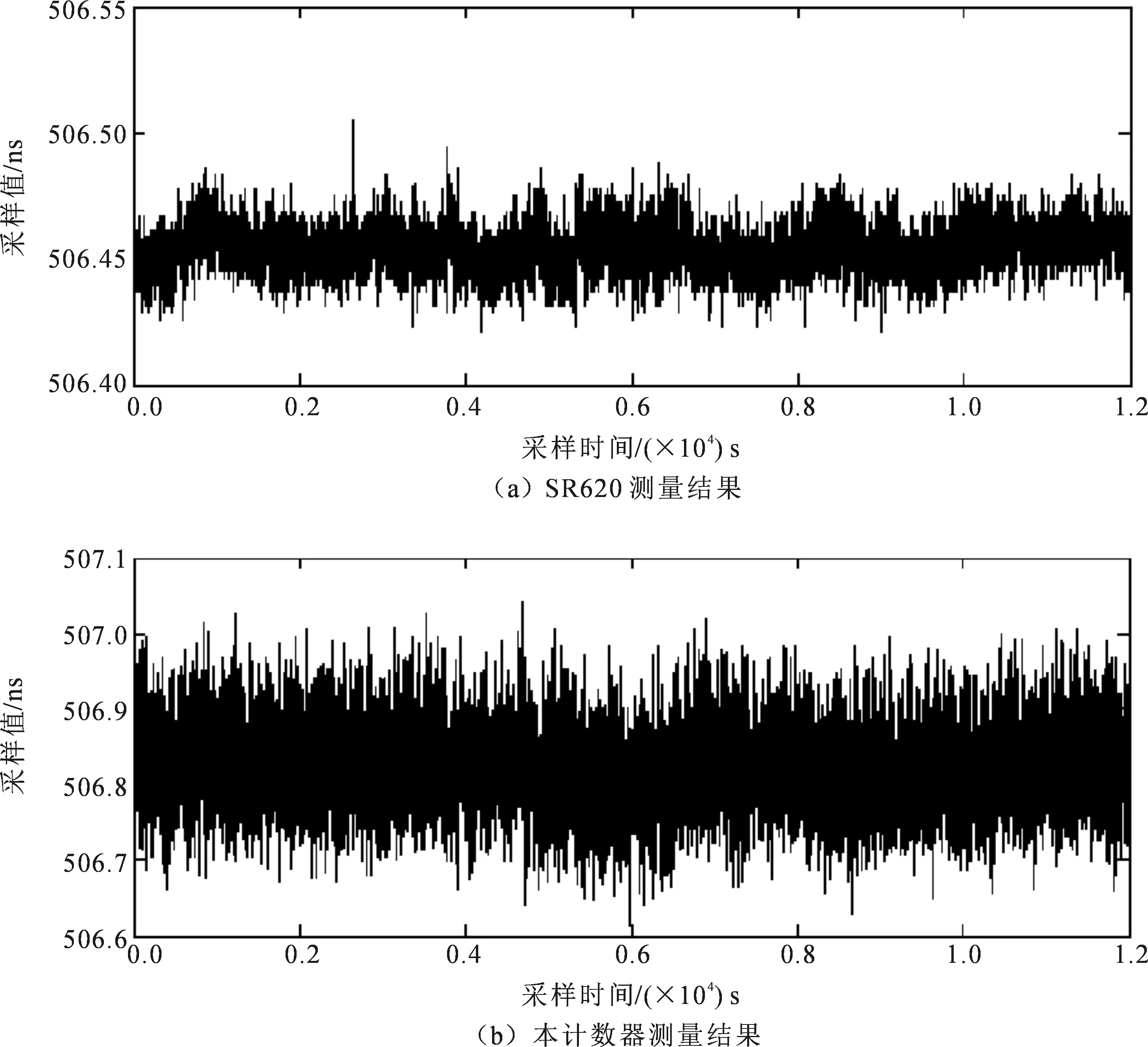

计数器2~4通道及SR620对于100 m延长线测试结果如图9所示,图中分别是本文设计的时间间隔计数器测量结果和SR620测量结果,图10为两者结果的偏差值。数据统计结果如表1及图11所示。

图9 本计数器与SR620测量结果比对

图10 本计数器与SR620测量结果之差

通过平均值绝对差统计结果可以看出,计数器测量时间间隔误差为44.8 ps,SR620测量时间间隔误差为9.3 ps;通过标准偏差(A类不确定度)统计结果可以看出,计数器测量时间间隔精度为56.3 ps,SR620测量时间间隔误差为9.3 ps。通过计数器与SR620偏差统计结果可以看出,两者偏差最大值为588.3 ps,偏差的标准均方差为57.3 ps。可以说明该时间间隔计数器可以达到单次测量优于600 ps,多次测量优于60 ps的测量准确度。

表1 计数器与SR620纳秒级测量统计结果

需要说明的是,测量结果中计数器与SR620有一定的偏差,是由于实验器材(线材、转接头)并不能做到完全相同等因素引起,后续可进行进一步的校准。

前文提到本论文采用做差的方式得到时间间隔,可有效降低公共误差对系统测量性能的影响,为验证这一结论对实验数据进行进一步的分析。分别对单通道测量结果和做差之后的结果进行统计分析,统计结果如图11所示,通道2的标准偏差为0.244 8 ns,通道4标准偏差为0.253 1 ns,做差之后得到待测值的标准偏差为0.056 3 ns,且符合规范的正态分布。通过数据可以看出,该方法可抵消掉测量结果中公共误差的影响,得到更好的测量精度。

图11 计数器单通道测试结果分析

3.3 脉冲宽度测量结果分析

本计数器可通过将工作模式设置为“脉冲宽度测量”功能实现脉冲宽度测量,测量原理为两个内部测量通道1和3(或2和4)连接到一个输入引脚STOP1(和STOP2)。上升沿由通道1(2)测量,下降沿由通道3(4)测量。再将两通道测量结果相减,即得到脉冲宽度测量结果。测量原理如图12所示。

本功能测量结果依然和SR620的脉冲宽度测量结果进行比较,待测脉宽均为国家授时中心钟房的1 PPS信号,参考时钟为钟房的10 MHz信号。由图中可以看出,本次测量所用的1 PPS信号脉宽并不恒定,本计数器的测量结果和SR620的测量结果基本一致,测量结果如图13所示。

图12 脉冲宽度测量原理

图13 本计数器与SR620脉冲宽度测量结果

4 结语

本文基于FPGA和GPX2设计了一款高精度时间间隔计数器,可实现4通道同时测量。实际测试结果表明系统对时间间隔测量的精度(A类不确定度)优于60 ps,多次测量的准确度偏差优于60 ps,量程可以达到1.6 s;具备脉冲宽度测量功能,测量结果和SR620基本一致,能初步满足时间同步等领域的测量需求,并且由于测量方法的优越性,可以为系统在不同环境下的测量精度提供一定保证。由于本系统还处于测试阶段,尚不能达到芯片的理论测量性能,还有许多方面需要完善:比如系统的供电质量对测量精度的影响,各种误差的处理等问题,都需要做进一步的讨论[25]。