应用于UTC(NTSC)远程复现终端中的时间间隔计数器的设计与验证

刘琼瑶,刘音华,刘正阳,李孝辉

(1.中国科学院 国家授时中心,西安 710600;2.中国科学院 时间频率基准重点实验室,西安 710600;3.中国科学院大学,北京 100049;4.中国科学院大学 天文与空间科学学院,北京 101048)

0 引言

中国科学院国家授时中心承担着我国标准时间的产生、保持和发播等重大任务。将国家基准时间UTC(NTSC)以更准确、更经济的手段传播给用户,是科学家们坚持不懈研究的目标。目前为止,主要的授时手段有长短波授时、低频时码授时、互联网授时、卫星单向授时、卫星共视、卫星双向比对、光纤传递等。其中,光纤时间传递是目前为止授时精度最高的时间传递方法,时间比对不确定度优于1 ps,但是其成本较高,长短波授时、卫星单向授时等方法成本较低,用户只要具备相应的接收机即可,但其精度也低,短波的授时精度约为1 ms,长波约为1 μs,卫星单向授时为100 ns左右[1-3],这些方法均不能满足高精度时间服务的需求。卫星共视法于1999年被国际电信联盟采纳为计算协调世界时的方法,相比其他授时手段,其比对精度较高,并且成本适中,成为现在广泛使用的时间比对方法[4]。

传统的卫星共视法每个观测周期都存在3 min的死时间,且观测结束后才进行数据处理,使得比对结果滞后,存在较大的局限性[5]。国家授时中心针对该问题对卫星共视法进行了改进,通过连续时间比对的方法设计了UTC(NTSC)远程复现系统。

在UTC(NTSC)远程复现终端中,时间间隔的精密测量是关键的一个环节,且时间间隔的测量精度直接影响着最后的复现精度,因此要提高系统的复现精度,设计更高精度的时间间隔计数器也是十分重要的。目前,通讯、导航等各行业领域对时间频率信号的准确度要求越来越高,为满足更多用户的需求,不仅要探索更高性能的授时手段,还要设计更精密的时间频率信号的测量方法。本文基于FPGA(field-programmable gate array)加法进位链设计了时间间隔计数器,并在UTC(NTSC)远程复现终端中进行了验证。

1 UTC(NTSC)远程复现原理

远程复现系统基于卫星共视原理进行时间比对:时间基准端和复现端的接收机在同一个共视时间表作用下,在同一时刻观测同一颗卫星,事后进行数据交换,计算出基准端和复现端的钟差,实现两地的时间比对[6-7]。

基于卫星共视法的原理,国家授时中心设计了UTC(NTSC)远程复现终端,其原理图如图1所示。

图1 UTC(NTSC)远程复现原理图

该系统通过连续时间频率比对的方法进行UTC(NTSC)远程复现。工作原理就是:时间基准端和复现端同时观测所在地的共同可视卫星,通过时间间隔计数器分别测得国家标准时间UTC(NTSC)与导航系统时间、本地原子钟与导航系统时间之间的钟差,并将测得的钟差传送至数据处理中心,抵消钟差、部分星历误差以及大部分路径时延,得到复现端与基准端的时间偏差,并将其反馈至UTC(NTSC)复现终端,UTC(NTSC)复现终端根据收到的数据及历史结果,输出一个对时间复现端本地原子钟的驾驭量,控制复现端本地原子钟的输出,使其与基准端的标准时间UTC(NTSC)同步,从而实现UTC(NTSC)远程复现[1-4]。

在上述的UTC(NTSC)远程复现系统中,UTC(NTSC)的准确复现依赖于对复现端与基准端时间偏差的准确测量,而时间间隔计数器在这个过程中起到了决定性作用,其测量精度直接影响着最后的时间复现精度。因此,对于整个系统而言,设计一个高精度、稳定性好的时间间隔计数器是必须的。

2 时间间隔计数器

在UTC(NTSC)复现终端中,时间间隔计数器主要是测量两个不同来源的1 PPS信号之间的时间间隔,针对此应用需求,笔者基于精密时间内插法设计了测量范围为0~1 s的时间间隔计数器。

2.1 时间间隔计数器的测量原理

时间间隔计数器的设计采用“粗+细”的测量模式,原理如图2所示。

图2 时间间隔测量原理

粗测量部分采用脉冲计数法,通过周期为TP的基准时钟进行直接脉冲计数,粗测量部分计数结果为N,则该部分测量的时间间隔为NTP[8]。但是该部分测量分辨率为TP,对于小于TP的时间间隔,如图2所示的ΔT1和ΔT2的测量则通过细测量实现。

最终待测量的起始信号与停止信号之间的时间间隔为:

T=NTP+ΔT1-ΔT2。

(1)

细测量部分通过利用FPGA内部的加法进位延迟链资源实现时间的精密内插,从而有效提升测量的分辨率。FPGA芯片中具有大量的逻辑单元LE,LE之间具有用于快速进位功能的进位链,其carry-in到carry-out的进位延迟一般都在几十皮秒,且各级LE之间没有多余的走线延迟[9]。将LE之间的进位延迟作为精密时间内插的最小延迟单元,理论上可以将时间间隔测量的分辨率至少提高到100 ps,足够满足时间复现精度的需求。

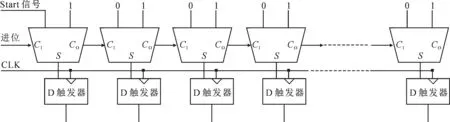

2.2 进位链的设计

FPGA中进位连线是为了加减法运算而设计的,各级进位连线之间没有任何关系,要将它们级联起来,才能形成一个完整的测量链路。串行加法器可以将各级进位连线级联起来,如图3所示。

第一级加法器的两个输入端分别接起始信号和高电平,其余加法器的两个输入端分别接低电平和高电平,当起始信号的上升沿到来时,就会在所构建的进位链中进行传播。各级加法器的输出端均接入一个D触发器,D触发器的时钟端接入粗计数的基准时钟信号,当基准时钟信号的上升沿到来时,就可以定位起始信号在进位链中的位置。根据起始信号在进位链中传播的延迟单元个数以及各个延迟单元的时延,从而求得起始信号上升沿和紧接着的下一个时钟信号上升沿之间的时间间隔,达到细测量的目的[10]。

图3 进位链的设计

2.3 进位链的校准

由于制作工艺等因素的影响,不同型号的FPGA器件的进位链时延是不同的;同一器件各级进位延时单元的时延也并不完全相同,并且很容易随着工作环境(温度、电压等)的改变而改变。为了使测量结果更加准确,需对进位链的各级进位延迟单元的时延进行实时校准[11]。

本文采用基于统计学的码密度法对各个延迟单元的时延进行校准,校准原理如图4所示[12]。

图4 码密度校准原理示意图

大量具有随机跳变特性的脉冲信号在进位链中传播,同时用周期为TP的粗计数基准时钟信号进行采样,则随机脉冲的跳变将均匀地分布在[0,TP)的区间内,随机跳变落入第i级延迟单元内的次数ni正比于第i级延时单元的时延di,当样本数N足够大时,则有:

(2)

可以近似认为进位链中各个延迟单元的时延为:

(3)

(4)

(5)

进位链校准的过程如图5所示。对进位链进行校准时,在进位链的开始端输入随机脉冲,在D触发器阵列的时钟端输入粗计数的基准时钟作为采样信号,当采样信号的上升沿到来时,通过编码器对D触发器阵列的输出进行编码,定位随机脉冲在进位链中传播的位置,并将该位置信息存储到RAM存储器中。根据多次采样的结果,按照式(3)和(5)计算出各级进位链的时延,并存储到查找表中,在之后计算测量结果时调用。

图5 进位链校准过程示意图

3 时间间隔计数器测量精度分析

本文基于Altera 公司的Cyclone IVEP4CGX150DF31C7器件上设计了时间间隔计数器,并进行了测试验证。试验中测量了上百组不同时间间隔的秒信号,每组秒信号连续测量1 min,每秒输出一次测量结果,取60次(即1 min)测量的平均值为最终测量结果。表1为10组1 PPS秒脉冲信号时间间隔的实测结果,并与SR620的标定结果进行了对比,测量范围从100 ns至999 999 900 ns,测量时间为1 min。

表1 时间间隔计数器实测结果 ps

由表1中的实测结果可以看出,计数器的测量误差保持在100 ps以内,具有较好的准确度;标准偏差小于80 ps,有较好的稳定度。

为进一步对时间间隔计数器的稳定性进行测试,对多组时间间隔进行了长达20 h左右的连续测试,图6为对999 999 903 008 ps的时间间隔长时间测试的测量结果,测量均值为999 999 902 209 ps,对测量结果进行系统偏差的校准后,测量值与真值之间的偏差为68 ps,标准偏差为78.5 ps。图7为该组测量结果的概率分布情况,由图中可以看出,测量结果基本满足正态分布,均值在999 999 902 200 ps左右,符合实际情况。

图6 时间间隔计数器长期测量结果

图7 测量结果的分布情况

4 UTC(NTSC)远程复现结果分析

将基于FPGA加法进位链设计的时间间隔计数器应用到UTC(NTSC)远程复现终端中,复现由临潼至西安卫星导航试验场的时间,对远程复现终端连续测试100 h,实现结果如图8所示。

图8所示的试验中,每隔1 min采样一次,即1 min输出一次复现端与基准端的时间差值,单位为ns。表2为对复现结果的统计分析,用复现端与基准端的差值(复现误差)来表征该UTC(NTSC)远程复现的准确度,复现误差的标准偏差表征该系统的稳定度。根据对复现结果的统计分析,可以得到UTC(NTSC)远程复现的准确度始终保持在±10 ns以内,而时间间隔计数器的测量误差小于100 ps,对UTC(NTSC)远程复现误差的贡献小于1%。

图8 复现端与基准端的时间差值

表2 对复现误差的统计分析 ns

5 结论

基于FPGA加法进位链,设计了时间间隔计数器,并且基于码密度法对进位链进行实时校准。测量了时间间隔在100 ns与999 999 900 ns之间的多组信号,实验结果表明,该时间间隔计数器测量准确度优于100 ps,稳定度也保持在80 ps以内,性能较好。

将该计数器应用于基于卫星共视的UTC(NTSC)远程复现终端中,连续测试100 h,时间复现的准确度保持在±10 ns以内,稳定度优于5 ns,时间间隔计数器对UTC(NTSC)远程复现终端的复现误差贡献小于1%,完全满足UTC(NTSC)远程复现终端中时间间隔计数器的应用需求,具有一定的推广价值。