基于FPGA的电容式声压传感器阵列信号采集存储系统

沈倪鑫,王任鑫,张国军,杨晟辉,张文栋

(中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051)

0 引言

采用MEMS工艺加工制作的电容式声压传感器可在水下实现很好的声特性阻抗的匹配,具有器件设计灵活、体积较小、易实现阵列集成[1],且生产成本较低、灵敏度较高、适合批量化生产加工等特点,使得该类传感器在水声信号检测方面具有很高的应用价值与广阔应用前景。但由于电容式声压传感器的敏感微结构的静态电容量一般处在pF量级左右,电容变化量处在fF量级甚至更低[2],且针对不同频段所设计的电容式声压传感器组成阵列后,不同阵元接收声信号时产生的电容变化量也不同,因此设计一种能够检测不同阵元的电容检测电路,同时实现信号的采集与存储,是电容式声压传感器阵列应用于水下环境、进行水声信号检测的前提。

目前用于测量微小电容的方法有:交流电桥法[3]、开关电容法、调制解调法、电荷放大法以及跨阻放大法等。本系统选用跨阻放大法[4]设计电容检测电路,通过可编程增益跨阻放大器构建程控放大电路,并通过FPGA控制增益大小选择用以匹配传感器阵列的不同阵元,实现电容变化量到电压信号的转化。该方案相较于针对不同的传感器阵元设计不同的检测电路更加灵活,适用性更广。

1 电容式声压传感器阵列

电容式声压传感器实际上类似一个微型化的、底部电极固定、顶部电极可以振动的平板电容,其工作原理是利用了平板电容两极板间的静电力和顶部电极(即振动薄膜)自身的结构应力之间的力平衡。当振动薄膜接收到声波时,振动薄膜会由于一定频率的声压作用产生相应频率的振动,从而使电容传感器上、下电极的间距发生改变,引起电容值的变化,从而实现了声波的接收和检测。电容式声压传感器微结构如图1所示。

图1 电容式声压传感器微结构

电容式声压传感器的振膜厚度与直径与传感器谐振频率相关,硅油孔大小与灵敏度相关[5]。电容式声压传感器阵列共4个阵元,每个阵元谐振频率不同,用于检测4路声压信号。

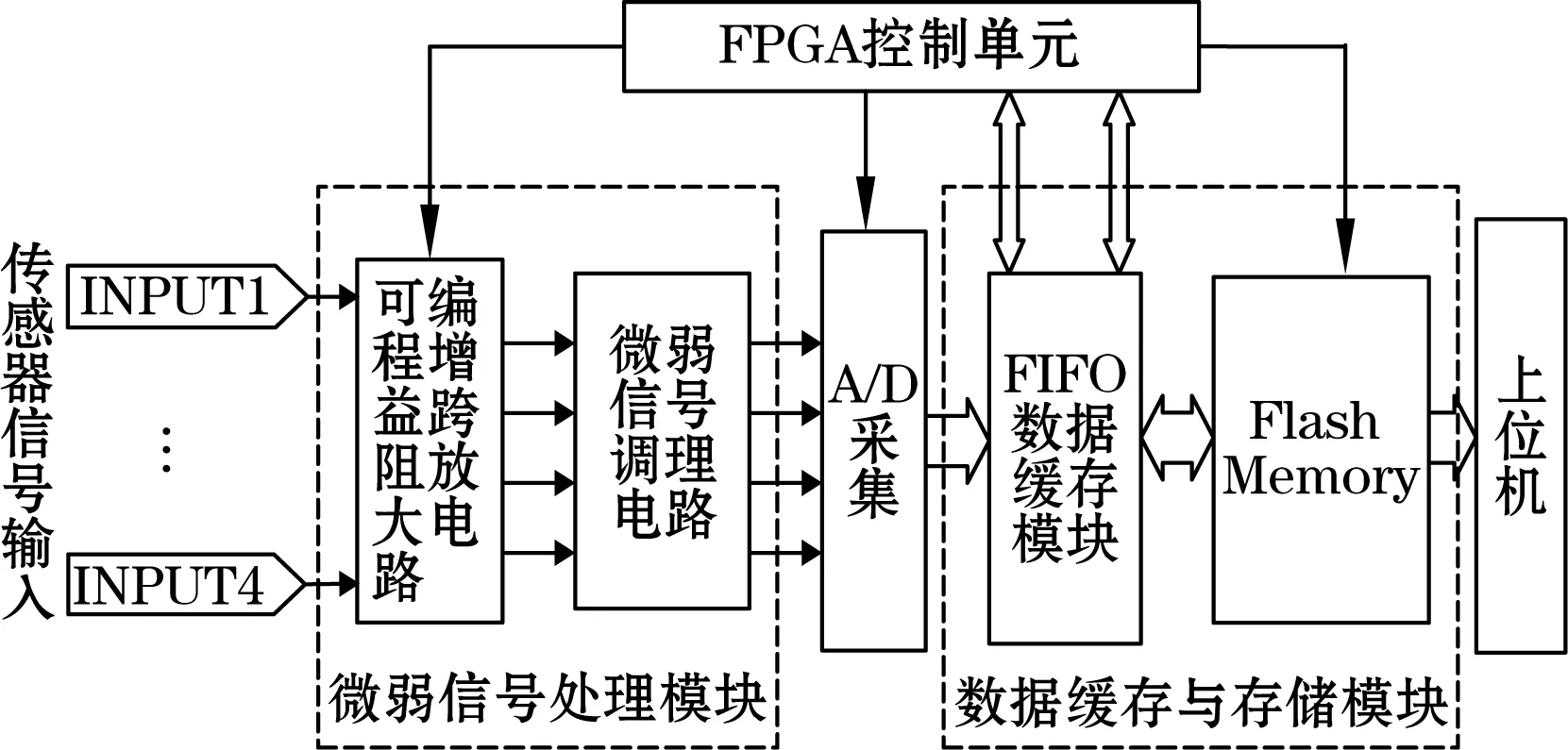

2 基于FPGA的系统总体结构

本系统主要由信号处理模块,A/D转换、FIFO数据缓存模块与存储模块组成,FPGA主控单元选用SPARTAN-6系列的XC6SLX9芯片,通过Verilog硬件描述语言与原理图混合编程实现全部时序的控制。系统总体结构图如图2所示,其中电容式声压传感器信号的检测、采集与存储是本文的设计核心,包括传感器信号检测电路、FPGA逻辑控制、微弱信号处理模块、数据缓存模块与Flash存储模块的设计。

图2 系统总体结构图

3 系统硬件设计

3.1 电容式声压传感器信号检测

本系统采用可编程增益跨阻放大器构建程控放大电路[6],增益大小分别设置为1倍、2倍、4倍、8倍、16倍、32倍,增益路径预设为FB0。主控单元FPGA将通过SPI总线控制ADA4350选择与传感器相匹配的增益路径。串行工作模式下,用于选择不同跨阻增益路径的编码如表1所示。

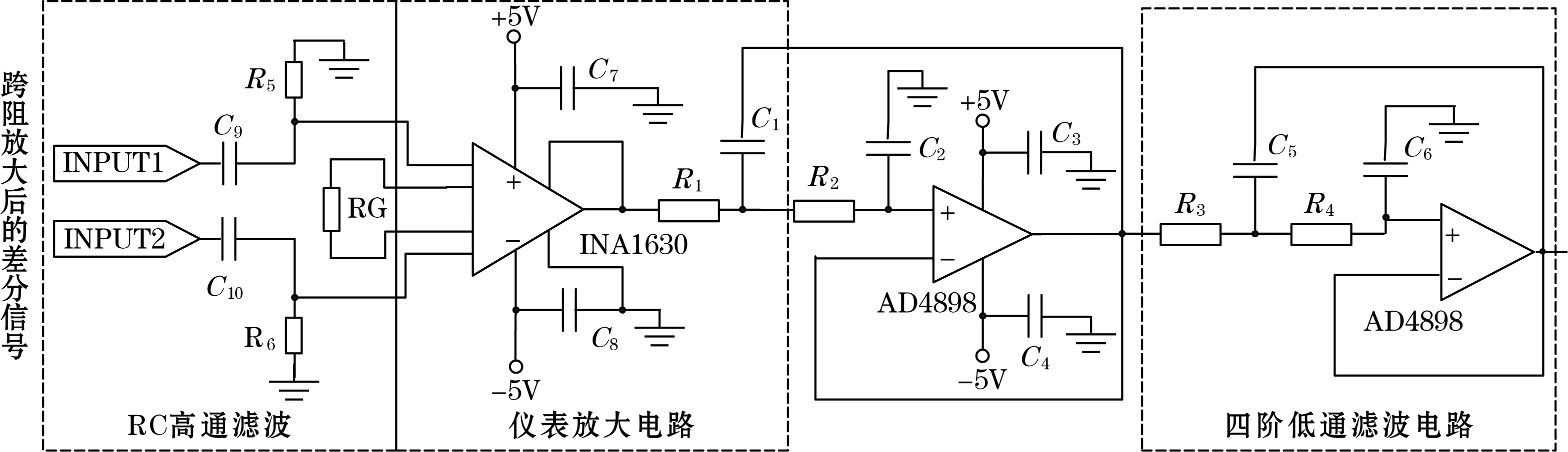

3.2 微弱信号调理电路

直流偏置电压施加在电容式声压传感器两端,传感器输出电流值为nA到μA级别,经过跨阻放大电路转化为电压值为μV到mV级别,仍属于非常微弱的信号且易被复杂的水下环境背景噪声淹没,本系统通过信号调理电路对经由跨阻放大后的传感器信号进行预处理,调理电路采用双电源供电,对信号进行放大与滤波,信号增益设置为33.98 dB,通带范围为5~5 kHz。信号调理电路采用具有超低噪声和高共模抑制比的仪表放大器INA163实现传感器信号的放大。为滤除水声信号中掺杂的高频成分毛刺,需对信号进行低通滤波处理,选取具有超低噪声、超低失真度、单位增益稳定的电压反馈型运算放大器ADA4898搭建Sallen-Key结构型四阶低通滤波电路[7],该滤波电路的设计使用可降低信号的失真度以及压缩噪声带宽。电容式声压传感器微弱信号调理电路基本结构如图3所示。

表1 ADA4350串行工作模式命令

3.3 A/D转换模块

A/D转换模块芯片采用微功耗采样AD7606来完成对电容式声压传感器输出模拟信号到数字信号的转换[8]。本系统设置AD7606工作状态为:并行接口模式(16位)输出;设置采样率为4 ksps;模拟信号输入电压范围为±5 V;16倍过采样进行采集转换;使用片内内置的2.5 V带隙基准电压源。转换开始前,Reset上升沿复位AD7606,复位信号至少保持50 ns;复位后CONVSTA与CONVSTB上升沿开启模数转换,转换开始后BUSY输出为高直至所有通道完成转换,拉低片选信号CS,使能数据帧传输。

3.4 FIFO数据缓存模块

FIFO缓存模块是一个带有控制逻辑模块的先进先出的数据存储阵列[9],用于解决异步时钟之间的接口电路通信问题。为使A/D采集到的数据写入FPGA的速度与Flash的存储速度相匹配,同时避免发生亚稳态和产生毛刺,本系统采用具有读写功能的存储单元FIFO作为异步时钟域之间的隔离接口以实现高速数据的缓冲。XC6SLX9内部配置有32个Block RAM,每个Block RAM块容量为18 KBit,这里利用两个Block RAM以实现宽度为16 bit、总容量为2 KByte的FIFO缓存模块。配置方式为双端口RAM 模式,一个端口在写信号的控制下写入经模数转换后得到的数字信号,并存储在缓冲器中,另一个端口在读信号的控制下读取数据,并转存到Flash存储器中。FIFO模块与Flash存储模块逻辑连接如图4所示。

图3 微弱信号调理电路基本结构

图4 FIFO数据缓存模块与Flash存储模块逻辑连接图

3.5 Flash存储模块

本系统采用NAND型Flash芯片K9WBG08U1M,Flash基本操作包括写入、读取和擦除,其中写入/读取操作是以page页为基本单位;擦除操作是以block块为基本单位[10]。在写入字节地址、页地址和块地址后,将会判断OFFSET(控制逻辑根据双口RAM的写入地址addra和读取地址addrb的偏差值来判断FIFO中是否存入数据)是否为零,若为零则等待双口RAM写入数据,否则将数据从B口读出。Flash页编程流程图如图5所示。

图5 FLASH页编程流程图

图6 系统测试示意图

4 系统测试

系统测试如图6所示,测试过程采用比较校准法[11-12],将电容式声压传感器阵列弹性悬挂于机械回转杆上,并将标准声压水听器放入驻波桶内,使两者处于同一水平面上、同时接收由驻波桶底部发射换能器发出的声信号。测试使用的标准声压水听器灵敏度为-193 dB(0 dB ref 1 V/μPa)。测试过程中从50 Hz~5 kHz,以1/3倍频程为步长,对电容式声压传感器的输出信号进行采集与存储,并通过示波器读取并记录标准声压水听器的输出电压值。通过MATLAB程序对数据进行处理。测试结果选取一路阵元信号显示;电容式声压传感器与标准声压水听器输出电压值对比如图7、图8所示。

图7、图8测试结果表明:通过改变增益路径、提高增益能够明显提高电容式声压传感器的输出信号大小。

图7 选取增益路径FB0时输出电压值对比图

图8 选取增益路径FB3时输出电压值对比图

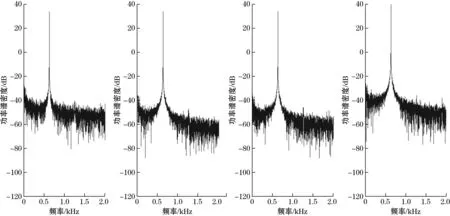

驻波桶发射频率为630 Hz的单频信号,通过本系统对电容式声压传感器阵列进行信号采集与存储,并通过上位机显示,图9所示为该系统检测信号的频谱分析图。

图9(a)、图9(b)测试结果表明该系统可实现传感器阵列不同阵元的声信号检测。

5 结束语

本系统基于FPGA成功设计了一套应用于电容式声压传感器阵列的信号采集存储系统。测试结果表明,本系统可成功对电容式声压传感器阵列拾取的声压信号进行采集与存储,信号传输快、数据存储稳定。本系统在实现电容式声压传感器阵列信号检测方面具有较好的应用前景。

(a)4通道增益路径均为FB2时检测信号频谱图

(b)调整各通道增益路径后检测信号频谱图图9 系统检测信号频谱分析图