超低盲区时域反射以太网电缆测试仪设计

陈 玉, 刘永泰, 冯红银萍

(1. 山西大学 商务学院信息中心, 太原 030031; 2. 山西大学 数学科学学院, 太原 030006)

0 引 言

在网络维护中,网线测试是其中重要一环,简易网线测试仪在复杂布线环境检测中效率低下、不够直观和准确;而时域反射(Time Domain reflection, TDR)网线测试仪能够及时、准确地定位故障点;工程中常用商业化高分辨率网线测试仪由于价格高等因素,致使其使用普及率相对较低,为此开发较低成本的高分辨率网线测试仪就显得较为重要;近年,国内外在高分辨率网线测试仪研究方面很少有公开、完整、有实用价值的参考资料,而一些可参考的文献技术资料[1-2]又存在研究相对不完善的地方;面对上述问题,从测试完整性、高分辨率和低成本需求出发,在实验改进的基础上开发设计了超低盲区TDR网线测试仪,该测试仪可对网线的开路和短路故障进行准确测量判断,其分辨率与国外品牌高分辨率网线测线仪相当。

1 理论依据

1.1 电缆TDR测量法

电缆TDR测量法主要有脉冲法和阶跃法2种技术方案。

1.1.1脉冲法

脉冲法是在被测电缆始端发射一定幅度和宽度的脉冲,通过单独判断发射脉冲和反射脉冲的时间差来确定被测电缆的长度[3]:

L=0.5v×Δt

(1)

式中:L为被测电缆长度;v为脉冲信号在电缆中的传播速度,由于脉冲信号传播时受传输介质影响,所以脉冲信号一般在铜缆中的传播速度约为0.66~0.85倍光速;Δt为发射脉冲与反射脉冲的时间差。

受脉冲宽度的影响,被测电缆较短时,会产生发射脉冲和反射脉冲的重叠,不能单独区分发射、反射脉冲,从而形成测量盲区,脉冲越宽盲区越大。

结合实际测试,假如网线测试仪要求最小测量0.1 m长网线,那么测试脉冲宽度必须保证在1 ns以下,如此窄的脉冲在实际中不仅难以实现,而且会带来很多其他难题,比如器件成本和电路设计难度的提升,即使最终实现了1 ns的脉冲,由于1 ns脉冲携带相当高的频率成分,在测试较长网线时又会引起脉冲的严重畸变,测试精度最后还是大打折扣,上述各种问题说明脉冲法并不适合低成本网线测试仪的设计要求。

1.1.2阶跃法

阶跃法的提出是为了解决脉冲法的不足,阶跃法主要是通过判断发射信号和反射信号叠加后二者信号电压特点进行测试的,与脉冲法相比阶跃法有如下优点[4]:① 由于通过依次比较测量叠加后发射、反射信号来确定被测电缆长度,所以理论上不存在测量盲区;② 阶跃信号持续性特点使得反射信号相对畸变要小得多,而且阶跃信号具有良好的平坦度。阶跃法缺点是功耗大,不便于多次测量。

1.2 网线测试仪设计原理

综合阶跃法和脉冲法各自特点,网线测试仪使用阶跃脉冲法进行设计,有文献也称之为宽脉冲法,即向被测网线注入一定宽度阶跃脉冲进行测试,由于设计网线测试仪所测网线最大长度为150 m,据式(1)阶跃脉冲大于1.5 μs即可,但是为了反射脉冲相对陡峭的上升沿和平坦度,设计中使用了15 μs的阶跃脉冲。下面主要针对网线测试仪开路和短路测试设计原理进行说明。

1.2.1宽脉冲法开路测试设计原理

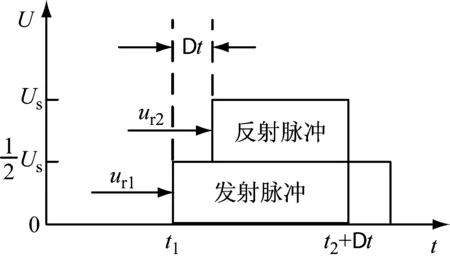

测量中将网线中的每一对双绞线近似看作均匀无损传输线,那么其特性阻抗就可看作实数阻抗,据此,已知阻抗等于网线阻抗(100 Ω)的信号源向被测网线注入一定宽度(15 μs)和幅度(3.3 V)的阶跃脉冲,具体电路如图1所示。网线终端开路时测试理想波形如图2所示,图2中纵坐标值Us表示信号源不接负责时的脉冲幅度(图3、图5同此),根据TDR原理,图中发射、反射脉冲互相叠加,相应测试电路(图1)中分别用参考电压Ur1及Ur2比较发射脉冲和反射脉冲的前沿[5],即发射、反射脉冲分别送入图1中的高速比较器C1和C2,最后通过计算两路高速比较器输出时间差Δt并依据式(1)即可确定开路距离。图2中由于器件本身的物理延迟,所以发射脉冲起始时间点t1不可能为零。

图1 开路测试高速比较单元电路图

图2 开路测试发射和反射脉冲叠加图

图1中固定电压的取值需要根据具体测试条件做一定的微调,从而保证测试结果精度上的“匀称”性,高速比较器C1、C2使用3.5~7 ns范围内的轨到轨比较器即可,如常用的AD8561、TLV3501等型号。

1.2.2宽脉冲法短路测试设计原理

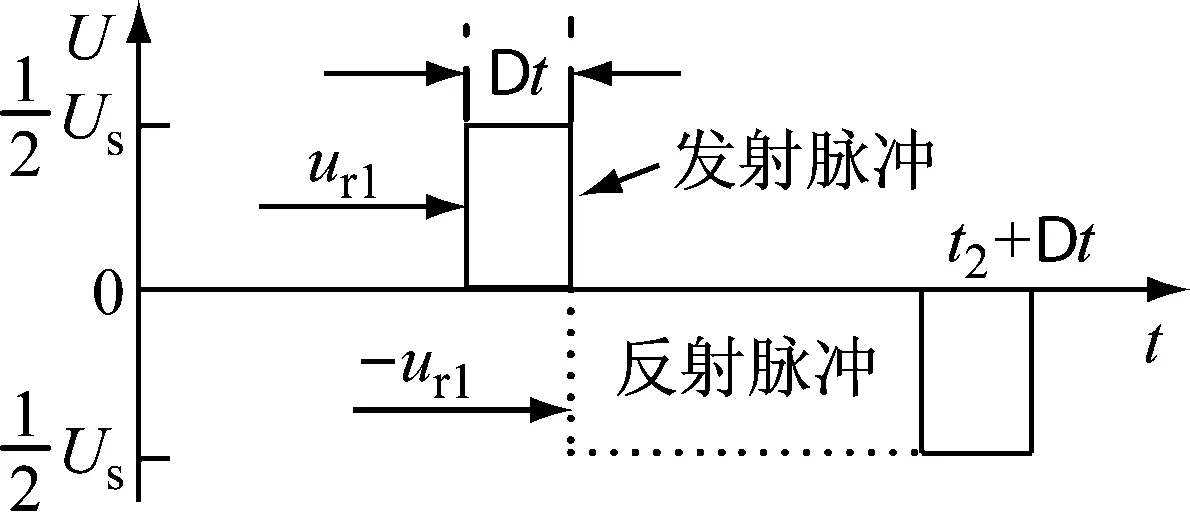

同开路测试设计原理,已知阻抗等于网线阻抗(100 Ω)的信号源向被测网线注入一定宽度(15 μs)和幅度(3.3 V)的阶跃脉冲,当网线终端短路时波形如图3所示,依据TDR原理,图中发射、反射脉冲叠加后由于极性相反,重叠部分相互抵消(理想状态下),最后只剩部分发射脉冲和反射脉冲,这时直接用开路测试中的电压比较法显然不行,主因是图3中没出现反射脉冲前沿(即图3中参考电压-Ur1所对应的虚线部分)。

为此设计中利用运算放大器差分放大特性,对反射脉冲作差分提取,原理电路如图4,分别将叠加脉冲和发射脉冲输入到差分放大电路,差分电路对两路脉冲作单位增益差分运算[6],最后输出图5即单一反射脉冲,运算式为:

(2)

式中:uso为还原反射脉冲,us2为发射脉冲,us1为叠加脉冲;最后计算分离的发射、反射脉冲时间差Δt即可确定短路距离。

图3 短路测试发射和反射脉冲叠加图

图4 差分运算放大单元电路图

图5 短路测试反射脉冲还原示意图

图4中的运算放大器选用共模抑制比为80 dB以上,-3 dB带宽在100 MHz以上轨到轨普通运放即可,如运放AD8091等。图4发射脉冲在输入到运算放大器时需做一定的阻抗匹配处理,由于网线的阻抗近似为100 Ω实阻抗,所以阻抗匹配电路可用纯电阻网络实现。

承接上述原理性知识介绍,下面对网线测试仪的具体实现环节作进一步说明。

2 网线测试仪软硬件结构单元

网线测试仪组成主要包括微控制器(Microcontroller Unit,MCU)、时间-数字变换器(Time-to-Digit Conversion,TDC)时间计数、链路脉冲检测单元、网线开路和短路测试单元及12路模拟开关单元,各单元分述如下:

2.1 MCU(单片机)处理单元

单片机主要依靠其内部程序控制外围单元电路完成网线链路脉冲、开路和短路测试,测试仪所用单片机为ATmega128A,当然也可选用性能相当的其他型号单片机,ATmega128A是一款高性能低功耗的8位单片机,单片机工作于16 MHz时性能高达16 MIPS,同时ATmega128A自带128 K Byte可编程flash和SPI串行通信接口,单片机的SPI接口正好和TDC-GP22的SPI接口直接对接;ATmega128A[7]在时钟选择上使用了16 MHz外接晶振,按照ATmega128A器件手册在3.3 V供电情况下外接晶振最大取12 MHz,不过为了提高程序指令的执行速度,在设计中选用了16MHz晶振,这样TDC-GP22芯片就可以将测量上限提高到150 m,经过实际电路验证,16 MHz晶振完全可以长时间稳定测量。

2.2 脉冲间隔时间测量单元TDC

时间数字测量方案常见的有单片机和FPGA等,采用单片机进行测量,时间跨度多在μs级,同时误差较大,而采用FPGA进行测量虽可精确到ns级,但是FPGA需要复杂编程来实现时间数字测量功能,同时FPGA功耗大成本高,引脚数量巨大,这些方案都不适合低成本及手持仪器设计要求[8]。TDC-GP22是一款高精度可编程TDC芯片,该芯片静态功耗在微安级,引脚数少等优势,TDC-GP22只需通过单片机读写其中寄存器就可以精确测量间隔脉冲的时间跨度,其测量精度可达45 ps。

设计中通过开启TDC-GP22噪声位,将测量范围1扩展到了0~2.4 μs[9];由于阶跃脉冲在网线中的传播速度约为200 m/μs,2.4 μs上限最远可以测240 m长的网线,完全满足网线测试仪150 m最大测量范围要求;TDC-GP22具有SPI接口, ATmega128A可通过SPI方式对TDC-GP22的各类寄存器进行读写来完成时间测量,TDC-GP22中7个配置寄存器配置程序代码如下:

gp22_wr_config_reg(0x80, 0x00242000);

//时钟4分频

gp22_wr_config_reg(0x81, 0x19490000);

//测量模式1,每通道一个采样

gp22_wr_config_reg( 0x82, 0xE0000000);

//通过Timeout给出中断

gp22_wr_config_reg( 0x83, 0x00000000);

gp22_wr_config_reg( 0x84, 0x20000000);

gp22_wr_config_reg( 0x85, 0x10000000);

//开启噪声单元

gp22_wr_config_reg( 0x86, 0x00000000);

TDC-GP22能否正确测试,关键在于其配置寄存器的精确配置,TDC-GP22程序每次测试前必须进行初始化操作以清空上次测量数据,同时单片机和TDC-GP22的数据通信必须严格符合SPI通信协议,否则单片机就不能正确读写TDC-GP22的寄存器。

图6 测量流程图

2.3 链路脉冲检测单元

以太网链路脉冲分为普通链路脉冲(Normal Link Pulse, NLP)和快速链路脉冲(Fast Link Pulse, FLP),二者的周期约为16 ms;链路脉冲是以差分方式传输的,设计中使用差分电路来获取链路脉冲信号;由于网线测试仪只需判断链路脉冲的有无,所以只使用传统的单运放四电阻电路来对链路脉冲信号做单位增益放大[1],电路如图7所示。

图7运放OP2为AD8091,该运放为可单双电源供电轨到轨高速放大器,其共模抑制比典型值为88 dB;因运放输出链路脉冲宽度较窄,不易被ATmega128A单片机捕获,所以加入峰值保持电路,通过调整C31与R*的值可以改变峰值信号的幅度与宽度,图中二极管D31选用普通1N4148系列二极管即可。

图7 链路脉冲检测单元电路图

2.4 开路测试单元

通过ATmega128A编程输出宽度15 μs的脉冲,再经74LVC1G17高速斯密特缓冲器对脉冲整形和阻抗变换后送至被测网线;送入被测网线后的脉冲同时也送至图1中比较器C1,随后的反射脉冲送入比较器C2。

在图1中C1和C2为TLV3501比较器,其中比较器C1输出至TDC-GP22的stop1,比较器C2输出至TDC-GP22的stop2,最后计算stop2-stop1值即可确定开路长度。图8所示为80 m 5类网线开路状态实测波形,图中反射脉冲叠加在发射脉冲上,反射脉冲幅度平坦,两路脉冲前沿区分明显;受测试电缆损耗影响,反射脉冲幅度有所降低[10],反射脉冲前沿较发射脉冲前沿变缓,不过对比前面图2的理想波形图和实际测试结果证明,图8完全可以满足测试要求。

图8 80 m网线开路实测波形图

2.5 短路测试单元

同开路测试,15 μs脉冲经过整形和阻抗变换后分别送入被测网线和TDC-GP22的stop1;网线上发射和反射脉冲的叠加信号送入差分放大电路(图4)反相输入端,同时发射脉冲送入差分放大电路的同相输入端,两路信号进行差分运算后输出至比较器TLV3501,比较器对差分信号幅度提升后送TDC-GP22的stop2,最后计算stop2-stop1的值即可确定短路长度。

图9为80 m 5类网线短路实测波形,图中发射和反射脉冲叠加部分幅度应为零,但由于被测网线和模拟开关直流电阻的影响而产生了图9中小幅度的正反射脉冲;实验结果表明,在150 m测量范围内的部分正反射脉冲并不会影响反射脉冲的提取[11-12]。

图9 80 m网线短路实测波形图

图10为差分电路所提取反射脉冲,其中残留了部分发射脉冲,这是因为参与差分运算的发射脉冲比反射脉冲具有更陡的前沿所致,残留脉冲可通过小电容去耦降低幅度。

本次教学改革所使用的简易腹腔镜训练器,同样能够达到规范腹腔镜下基本操作、提高手术技能的目的,且利于基层医院推广。但最重要的是重视基本功的训练,不盲目追求手术操作。有效的腹腔镜手术培训,对于提高手术质量、降低手术风险具有积极作用,真正做到磨刀不误砍柴工。

图10 反射脉冲还原实测波形图

2.6 12路模拟开关单元

网线多为4对双绞线组成,测量时需4对双绞线轮流测试,网线测试仪主要测试链路脉冲、开路和短路3种状态,每种状态测试4次,3种状态共需测12次,为此需要进行12次切换;考虑到功耗和切换速度因素,网线测试仪没有使用继电器,代之以12路模拟开关ADG621来进行测试切换,ADG621在±3.3 V供电下的单路直流导通电阻约为5 Ω,开关单次切换速度小于200 ns。

一对双绞线需ADG621的两个通道,这样加载到被测双绞线的直流电阻为10Ω,100 m 正规5类双绞线回路直流电阻约为18.5 Ω,总回路电阻约为28.5 Ω,短路测试由于回路电阻的影响[13],在发射、反射脉冲叠加处会产生正反射,正反射见图9,这样差分运算提取的反射脉冲幅度会降低,为此用比较器TLV3501对反射脉冲幅度进行提升,以便TDC-GP22识别。

3 网线测试仪电路组装和调试

3.1 电路板设计和整机组装

网线测试仪的主电路板为双面设计,电路板设计时对脉冲电路部分进行了接地包围处理,同时电路板背面整体覆铜并使覆铜面接地,各单元电路走线接地点通过过孔连接覆铜面以减少脉冲信号的干扰。电路采用手工分块焊接,同时辅以软件程序来实时检测芯片的焊接效果,网线测试仪完成焊接组装后如图11所示。

3.2 长度区间校准系数

受双绞线中分布电容和分布电感的影响,网线测试仪中发射脉冲和反射脉冲在测量不同长度的网线时其前沿的上升时间会相应的变化,网线越长脉冲前沿上升越缓;脉冲前沿变化势必会影响到网线测量长度的准确性[14-15],为此,网线测试仪先对不同长度的标准网线进行测试分析,对不同长度区间定义不同的校准系数,并重新定义式(1)为:

L=0.5V·Δt·λ

(3)

式中:λ为长度区间校准系数。

4 实验测试数据

4.1 实验前提条件

实验所用网线为5类非屏蔽双绞线,为方便测试,不同长度被测网线两端按568B规则加接水晶头,对短路测试,用5类模块按568B规则压接模拟短路故障点。

为模拟真实测试环境,实验使用了1台H3C-S1024千兆交换机、1台非管理24口百兆TEH2400交换机、1台TR-932D百兆光纤收发器及多台千兆网卡的PC机。实验中发现上述网络设备链路脉冲的幅度和周期都存在一定差别,不能一概而论。测量前用1 m、10 m和50 m的标准电缆对网线测试仪和FLUKE CableIQ网络测试仪进行3点测量校准。

4.2 实验数据结果

4.2.1网线测试结果

从表1测试结果可以看出,网线测试仪和FLUKE CableIQ在0.1~110 m的范围内,二者在链路脉冲测试、开路和短路测试精度上基本接近;表1中的测试结果显示网线测试仪误差范围在±10%以内,误差与FLUKE CableIQ相当。

4.2.2网线测试仪整机功耗

由于网线测试仪多在手持状态下使用,故设计上要尽可能降低整机功耗,为此设计上多选用低功耗方案和器件,最后实测网线测试仪最大测试电流为57 mA,远低于FLUKE CableIQ的150 mA测试电流。

5 结 语

网线测试仪通过硬件电路和软件程序的有机组合,以较低成本实现了高分辨率测量;TDC芯片的使用不仅简化了网线测试仪的软硬件设计,而且也提高了系统整体稳定性;再有,网线测试仪后期经过多人多次试用和改进,其对链路脉冲、开路和短路故障完全可以进行快速准确地判断。实际网线故障种类繁多,测试手段也各有不同,而网线测试仪主要是针对网线关键的开路和短路故障进行测试,为此,网线测试仪还有很多扩展开发余地,如增加线序测试和电缆阻抗测试功能等。