雷达FPGA软件测试技术研究与实现

申春妮

(南京电子技术研究所,江苏 南京 210039)

0 引 言

复杂可编程逻辑器件(CPLD)和现场可编程门阵列(FPGA)的出现,给数字电路系统设计带来了革命性的变革,极大地缩短了数字系统研发的周期和成本.由于其规模大、 集成度高、 处理速度快以及编程灵活等优点,在航空航天等军工领域可编程逻辑器件中得到广泛应用,常用于重要性和复杂度较高的产品,因此对FPGA/CPLD设计的质量和可靠性要求越来越高[1,2].原本在军用领域中作为硬件管理不作测试要求的可编程逻辑器件现已逐渐纳入测试范围.

本文针对FPGA软件特点及其测试的现状,结合软件测试技术对FPGA软件测试的过程进行了研究,重点阐述了雷达FPGA软件测试设计与实现的过程,最后对雷达某波控机FPGA软件进行了实例分析.

1 FPGA软件测试现状

雷达装备中FPGA应用越来越多,很多重要功能也是通过FPGA实现,但相关测试不充分,需求分析采用对设计文件追踪的方式,只进行对设计依据的罗列和追踪覆盖,独立性不强,依赖于设计文档质量,容易遗漏; 代码审查采用人工审查方式,只关注代码实现,不设计报告(概设、 详设)的一致性,甚至有时以不设计方的联席走查代替测试人员的独立审查/走查; 仿真验证弱化仿真,以板级确认测试代替; 时序分析只关注主要时钟路径,缺少对接口的时序分析,约束不完备,时有遗漏等.产品中由于FPGA软件缺陷引起的故障日益增多.由于FPGA时序器件的特性以及开发过程中测试验证的不充分,导致不少FPGA类软件问题在系统测试或外场使用时才暴露出来,例如:

某型号微波着陆接收模块FPGA软件模块偶发出现低温上电后内部本振模块不工作,导致微波着陆功能方位、 仰角数据输出无效.

某型号综合分机接口控制FPGA软件在系统测试时,话音突然中断.经故障排查,原因为FPGA中断处理缺陷.

这些问题偶发难以复现,环境依赖性强,问题排查困难,严重影响了FPGA产品质量和科研生产进度.

2 FPGA软件测试过程概述

根据GJB 9433-2018《军用可编程逻辑器件软件测试要求》,FPGA软件测试的基本步骤与常规软件测试相同,都需要进行测试策划、 测试设计与实现、 测试执行和测试总结4个阶段[3].但是由于FPGA 软件的特殊性,其测试过程中涉及到功能仿真、 时序仿真、 静态时序分析、 逻辑等效性验证、 跨时钟域检查等区别于传统软件测试的内容[4].因此,本节针对FPGA软件特点研究FPGA软件测试过程,对其测试流程的各个阶段的具体内容进行了重新规划设计,FPGA软件测试过程如图 1 所示[5].

2.1 测试策划

测试方根据测评任务书、 合同或其他等效文件,以及被测软件的任务书或需求规格说明等设计文档进行测试策划,编制软件测试计划.软件测试计划应经过评审,并应受到变更控制和版本控制.

2.2 测试设计与实现

测试方根据软件测试计划和软件测试需求规格说明进行测试设计与实现.测试设计的工作要求如下: 选定测试工具,建立并验证测试环境,确定测试优先级,设计测试用例集,编制测试说明.软件测试说明应经过评审,得到相关人员的认可,并应受到变更控制和版本控制.同时需要根据情况进行修订.

2.3 测试执行

根据所选定的测试环境、 测试工具以及设计的测试用例、 测试方法,执行规定的测试项目和内容.在执行过程中应如实地记录测试过程、 结果(必要时包含中间结果)以及发现问题的现象,填写软件问题报告单.

2.4 测试总结

测试方应根据软件任务书、 软件需求规格说明、 测试计划、 测试说明、 测试记录、 软件问题报告单,对测试工作和被测软件进行分析与评价.编写测评报告.对测试工作的分析与评价,总结测试文档和测试环境的变化情况及相应原因,总结测试问题及采取的措施情况; 在测试异常终止时,说明未能被测试活动充分覆盖的范围及其理由.对被测软件的分析与评价,总结发现的软件问题及每一个问题的处理和确认情况; 总结通过测试被测软件与软件任务书或者软件需求之间的差异,可提出改进建议.

3 雷达FPGA软件测试设计与实现

雷达FPGA软件测试包括静态测试和动态测试两部分[6].静态测试一般在动态测试之前完成,FPGA软件静态测试技术包括文档审查、 静态分析、 代码审查、 跨时钟域检查、 静态时序分析和逻辑等效性分析6种测试类型.FPGA软件动态测试技术包括功能仿真测试和时序仿真测试[7,8].

3.1 雷达FPGA软件静态测试

3.1.1 文档审查

针对FPGA软件特点,特别是有别于传统雷达软件检查内容,对文档中内外接口状态、 时序图及时序参数、 寄存器/存储器的定义、 同步电路、 异步电路设计方式、 跨时钟域设计方式、 复位电路设计原则及要求、 对IP核的论证、 验证情况和使用说明、 设计和实现约束描述等方面并结合文档的完整性、 规范性、 正确性和一致性等逐项列出审查条目.

3.1.2 静态分析

静态分析依据FPGA软件编码规范,使用编码规则检查工具对时钟域复位规则、 可综合性规则、 异步时钟域检查、 时序约束检查及编码风格等检查是否符合编码规范,辅助测试人员发现可编程逻辑器件问题.

雷达FPGA软件编码规范参考《军用可编程逻辑器件软件编程语言安全子集》、 《航空装备FPGA编码要求》,覆盖总装下发的《军用可编程逻辑器件软件编程语言安全子集》要求,包含12类强制或推荐规范,具体编码规范如表 1 所示。

目前市场上主流的编码规格检查工具主要有LEDA,HDL designer,Alint,Vlint等.

3.1.3 代码审查

代码审查要对代码和设计的一致性、 代码执行标准的情况、 代码逻辑表达的正确性、 代码结构的合理性以及代码的可读性等进行审查.测试人员需要仔细阅读相关文档,对设计充分熟悉,然后对照代码审查单,逐行认真阅读代码进行人工审查.人工审查中,重点关注无法通过工具自动分析发现的各种问题,如算法实现的问题、 编码与设计不符的问题、 代码设计中存在的逻辑问题等.

3.1.4 静态时序分析

静态时序分析是利用静态时序分析工具来分析逻辑综合或布局布线后得到的静态时序信息,根据信息提示找出不满足建立/保持时间路径以及不符合约束路径的过程.

静态时序分析至少对可编程逻辑器件软件最好、 最差和典型工况下建立、 保持时间、 异步复位的恢复/移除时间进行分析记录,时序分析的路径覆盖率为100%.

除了集成开发环境ISE自带的静态时序分析工具TimingAnalyzer和Quartus自带的静态时序分析工具TimeQuest外,目前业界使用较多的第三方静态时序分析工具是Synopsys公司的PrimeTime.

3.1.5 跨时钟域检查

跨时钟域检查利用跨时钟域检查工具对可编程逻辑器件软件中多时钟域之间的交互问题进行检查,避免亚稳态等不稳定的电路设计.

跨时钟域检查工具包括: Mentor Graphics公司的0in CDC工具,SpyGlass(CDC)工具.

3.1.6 逻辑等效性检查

逻辑等效性检查用于检查综合或布局布线过程中引入的错误,避免最终所得到的逻辑电路与设计存在偏差.

逻辑等效性分析要对可编程逻辑器件的RTL级代码、 逻辑综合之后的网表文件、 布局布线之后的网表文件两两之间开展的逻辑一致性检查.

测试要借助于等效性分析工具对文件之间的等效性进行分析,人工对结果信息进行二次分析,对问题进行追踪和定位.

Synopys公司的Formality工具支持FPGA的逻辑等效性检查,验证RTL代码和综合后网表,综合后网表和布局布线后网表是否逻辑一致.

3.2 雷达FPGA软件动态测试

3.2.1 功能仿真

功能仿真在不考虑构成电路逻辑和门的时间延迟前提下,着重考核电路在理想环境下的行为与设计构想之间的一致性.

功能仿真用例测试类型覆盖功能、 性能、 接口、 可靠性、 余量、 强度、 恢复性、 边界等,并给出动态仿真结果.

专业仿真测试环境包括: ModelSim、 Questa、 VCS-MX等.结合EDA开发工具QuartusII、 ISE、 Vivado等,能支持Verilog、 VHDL、 Systemverilog和SystemC的RTL仿真、 综合后网表仿真、 时序仿真等[9,10].

3.2.2 时序仿真

时序仿真是针对加入器件延时和线延时的布局布线后网表,使用动态分析的方法考核电路与设计构想之间的一致性.

测试可编程逻辑器件软件布局布线后的逻辑网表功能和时序是否满足设计要求,通过仿真工具运行与功能仿真相同的激励,对可编程逻辑器件软件布局布线后的逻辑网表进行仿真,分别添加3种工况(最好、 最坏、 典型)下的SDF文件,对功能和时序进行测试.

4 应用实例

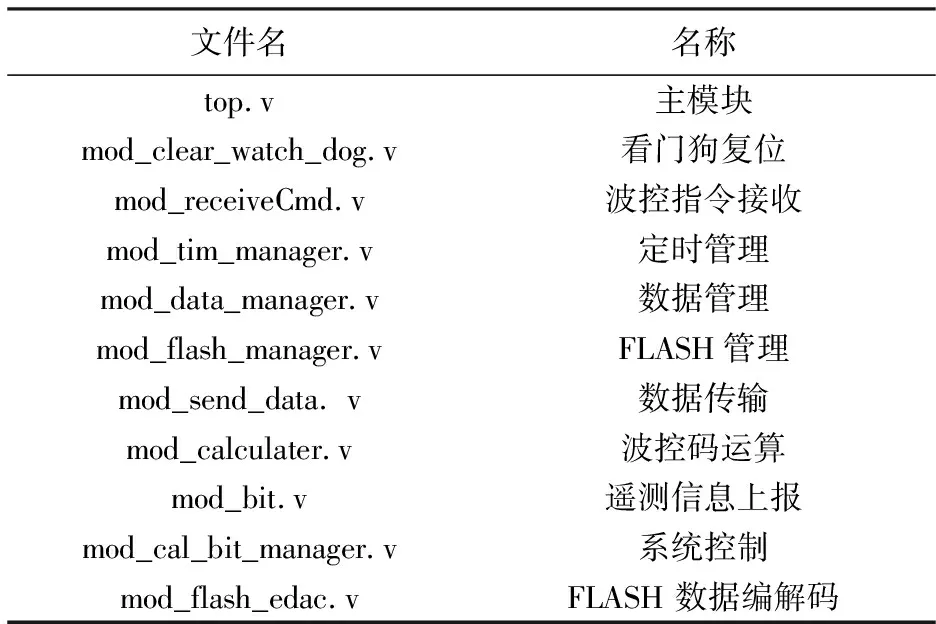

以软件测试为基础的FPGA 测试技术已经在雷达的各个分系统中得到了成功的应用.以雷达某波控机FPGA软件测试为例,该系统以Xilinx公司的XQ2V3000芯片为宿主机,采用Verilog语言开发,实现了SAR天线的波束控制功能,配合内定标器完成灵活的定标功能.同时采集SAR天线监测数据,向SAR监控定时器传递天线和波控机监测数据.程序清单如表 2 所示.

表 2 波控FPGA软件程序清单

测试人员根据测试总体方案的要求对该系统进行了文档审查、 静态分析、 静态时序分析、 代码审查、 功能测试/功能仿真测试、 时序仿真测试共6种测试类型的测试.搭建了仿真测试环境,进行了各模块的功能验证,开展时序仿真进行时序分析.测试结果如下.

4.1 文档审查

测试人员对开发方提供的需求规格说明和设计说明两份文档的完整性、 准确性、 一致性和规范性进行了审查,发现文档内容欠完整、 准确,缺接口信号定义、 时序关系、 协议数据定义等描述.软件开发人员修改了需求和设计文档.

4.2 静态分析

静态分析采用Alint工具自定义的规则集进行编码规则检查,发现顶层文件有门级逻辑、 模块缺端口信号和内部信号说明、 模块端口信号排列不符合格式要求等问题,提出改进建议后均进行了相应处理.

4.3 代码审查

代码审查发现代码和设计文档不一致后全部修改正确.

4.4 静态时序分析

静态时序分析采用ISE自带的静态时序分析工具TimingAnalyzer对软件布局布线后的门级网表在最好、 典型、 最差工况下进行时序分析检查,分析检查结果为: 未发现时序错误,满足建立时间、 保持时间时序要求.静态时序分析结果如表 3 所示.

表 3 静态时序分析结果

4.5 功能仿真

采用Altera Modelsim工具在仿真环境下,对独立功能的各个子模块进行比较全面的功能仿真,仿真语言为Verilog HDL.

图 2 FPGA软件仿真验证平台Fig.2 FPGA software simulation verification platform

仿真验证平台如图 2 所示,对不同的子模块写不同的test_bench,test_bench产生激励输出作为待测子模块的输入,子模块受输入激励产生输出,观察输出结果,验证子模块功能.

对各级子模块进行仿真测试,在对接口波形测试中发现,串行数据与需求规格说明文档中的定义不一致,需求文档中的协议描述有误,因此对该问题不更动代码,修改需求文档.

4.6 时序仿真

布局布线后,设计中添加了延迟信息.相应总结报告如下:

系统时钟clk: 外部时钟i_clk 经过BUFG延迟1 595 ps得到,作为各个子模块的输入时钟;

看门狗o_wdi: 相比于内部同步时钟延迟约567 ps (输出信号);

系统复位信号rst_4: 相比于内部同步时钟延迟约568 ps,作为其余各个子模块的复位信号(内部寄存器);

时序报告的结果表明内部逻辑各路径满足建立保持时间时序要求.

经过测试以及相应的修改和回归,该FPGA 系统代码质量和可靠性得到了提高,系统功能、 性能得到了验证.

5 结束语

针对雷达FPGA软件质量管控中存在的问题,以规范、 可操作性为目标,开展FPGA软件测试与验证研究.研究并制定符合雷达FPGA软件的编码规范、 测试规范,同时在实际项目中试点验证,实现持续改进.及早及时地发现和关闭FPGA 设计开发过程中存在的缺陷,提高了硬件描述语言的编写质量和系统的可靠性,并对FPGA的电路行为进行了有效的验证.最终保证FPGA 产品的质量,提升客户的满意度.