DSP和FPGA下的数据通信方案设计

李忠涛 中国电子科技集团公司第五十四研究所

1 系统的硬件设计

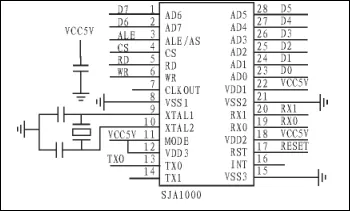

1.1 CAN总线控制器中的SJA2512模块硬件

SJA2512属于独立CAN总线控制器,其属于最先的总线控制器替代产品,其主要是在原本产品的基础上添加全新的工作模式。在本文所研究的系统中使用外接晶振能够实现系统时钟,并且在数据地址复用总线引脚和DSP相互连接。其中的地址锁存信号、芯片都能够实现信号的读取,其中的MODE引脚能够和高电平相互连接,使其能够在Inter时序中工作。图1为CAN总线控制器的模块工作原理结构。

图1 CAN总线控制器的模块工作原理结构

1.2 CAN总线收发器模块的硬件设计

总线收发器属于总线控制器与物理总线的接口,其属于较为长线的总线收发器,其能够对总线提供差动发送能力,并且还能够对总线控制器提供相应的差动接收能力。其中的RS引脚主要是在高速工作及斜率控制两种模式中工作,因为系统总线比较短,并且波特率比较低,所以此引脚主要是利用外部链接47k电阻实现,从而使芯片能够在斜率控制模式中工作。

1.3 电平转换模块的硬件设计

因为FPGA中I/O口输入和输出电平都是标准信号,SJA引脚输入输出点评都是电平信号,两者无法实现直接连接及数据传输,要利用两片电平转换芯片,能够实现以上两个芯片的相互转换。因为总线控制器数据地址的复用总线总线不仅能够从FPGA中实现数据的接收,也能够对FPGA实现数据的发送。所以就将复用总线在芯片中连接,其他的控制信号在另外的芯片中连接,从而实现电平转换方向的控制。因为控制信号引脚要通过FPGA中进行命令的接收,所以就要将其方向引脚到低电平中接收。

2 FPGA和DSP下的数据通信系统软件设计

2.1 对DSP模块程序进行设计

在该系统中,对于数字信号处理芯片的选用,选择了具有高性能的TMS320C67x系列,其由TI公司推出,在工作频率方面能够达到1GHz,这种较强的数据处理能力,可以确保高速数据传输的要求得到基本满足。对于DSP来说,受其地址线与数据线是分开的影响,不能直接同DO-D7相连,因此将其地址线AO作为数据选择线,在AO=0情况下,以DSP数据线上的数据为地址对SJAl000进行写入,在A0=1情况下,以DSP数据线上的数据为数据对SJAl000进行写入。在该系统中,DSP模块主要负责对SJAl000初始化过程的完成及对发送过程的控制。因SJAl000内部大部分寄存器的读写必须处于复位模式,为此在对SJAl000实施初始化前,需对其处理使其处于复位模式。完成配置后,确保SJAl000重新进入正常操作模式,等待对数据进行发送或接收。对SJAl000进行发送时,需对状态寄存器sR中的值进行读取,主要为TCS和TBS位的值,保证在SJAl000最近一次发送上已经获得成功,同时需保证发送缓冲器处在释放状态。之后面向发送缓冲器TXB对TX标识码进行写入、对TX结构信息进行写入、对待发送的数据进行写入;在最后,需面向命令寄存器CMR的TR位,对1进行写入,对发送请求进行置位,对发送操作进行完成。

2.2 对FPGA模块程序进行设计

该系统在芯片的选择上,选择了低功耗处理器,即EPlC6Q240C8型芯片,其由Altera公司提供,可对185个I/0接口进行提供,在处理速度上较快,且具有灵活、可靠等优势。对于FPGA模块来说,其主要负责对SJAl000地址锁存信号ALE的时序控制,完成对芯片使能信号CS的时序控制,并完成对读有效RD的时序控制,以及完成对写有效WR的时序控制。在DSP向SJAl000对数据进行写入时,trl数值为0,对于3.3VTTL标准信号,会使其转换成5VCOMS电平信号;在DSP向SJAl000对数据进行读出时,trl数值为1,对于5VCOMS电平信号,会使其转换成3.3VTTL标准信号。

3 系统的测试

信息的完整性指的是信号线中信号的质量,信号破损并不是因为某个因素导致的,其是因为多种因素导致的,信号完整性问题和振铃、反射、串扰,实际上在对高速数字信息进行处理过程设计一直都是CAN总线通信系统的设计难点。信号通过PCB进行传输,在信号走线比信号波长要大的时候,此走线也可以称之为传输线,要对PCB线际互联及板层特性对于电气新能影响进行全面的考虑。对于本文所设计的总线通信系统进行调试,首先要实现电路的调试。在对系统调试之后,表示系统的总线节点能够实现数据测试的接收,并且还能够解决其他中断程序对CAN总线接收的干扰,表示本文所设计的CAN总线程序能够有效执行

4 结语

为了使CAN总线的能够实现多节点可靠高速性传输,本文基于FPGA和DSP对CAN总线通信系统进行了设计。FPGA和DSP下的CAN总线通信系统设计,在硬件部分对DSP+FPGA加以采用,将其作为核心通讯处理单元,在软件部分对DSP模块程序与FPGA模块程序进行设计,具有很好的实时性,还能够确保系统数据在传输过程中稳定可靠。