基于ARM和FPGA协同的高可靠性雷达双机冗余伺服系统

(南京恩瑞特实业有限公司,南京 211106)

0 引言

航空运输安全保障通常要求天气雷达24小时不间断或者允许短间断运行,这对雷达天线伺服系统有着高可靠性、高强度、高环境适应性等要求[1]。因此,伺服系统常采用冗余设计的方式。在现有的雷达伺服冗余方案中,航管二次雷达大多采用双机热备[2],即双电机双驱动器冗余配置,通过PLC或PCC实现热切换[3]。但二次雷达只有方位轴的转动,该方案需要复杂的机械或电磁离合装置,在通常为双轴的气象雷达上实施将大大增加设备量和系统成本,未见实际应用。胡芳芳等人[4]所采用的是继电器-接触器控制系统,内部全部电缆导线连接,布线量大,无智能化控制、反馈和BIT(机内自测试)功能,切换过程不区分大小信号,缺乏足够的保护机制,现场应用过程中一旦出现问题则难以诊断和排查。

以机场天气雷达为例,可靠性瓶颈点不在天线座电机和角码反馈环节,主要存在于室内伺服分机,尤其是电机伺服驱动器部分[5]。本文采用混合冗余配置,即天线座设备为单机,伺服分机为双机冗余的方案,在不大幅提高系统复杂度和成本的前提下,在很大程度上提升系统的可靠性。

1 双机冗余系统组成

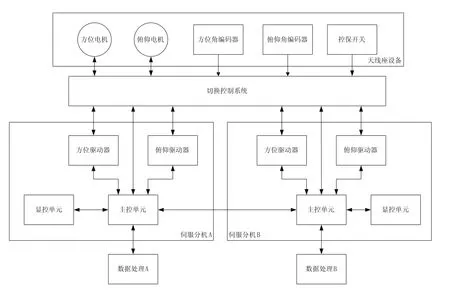

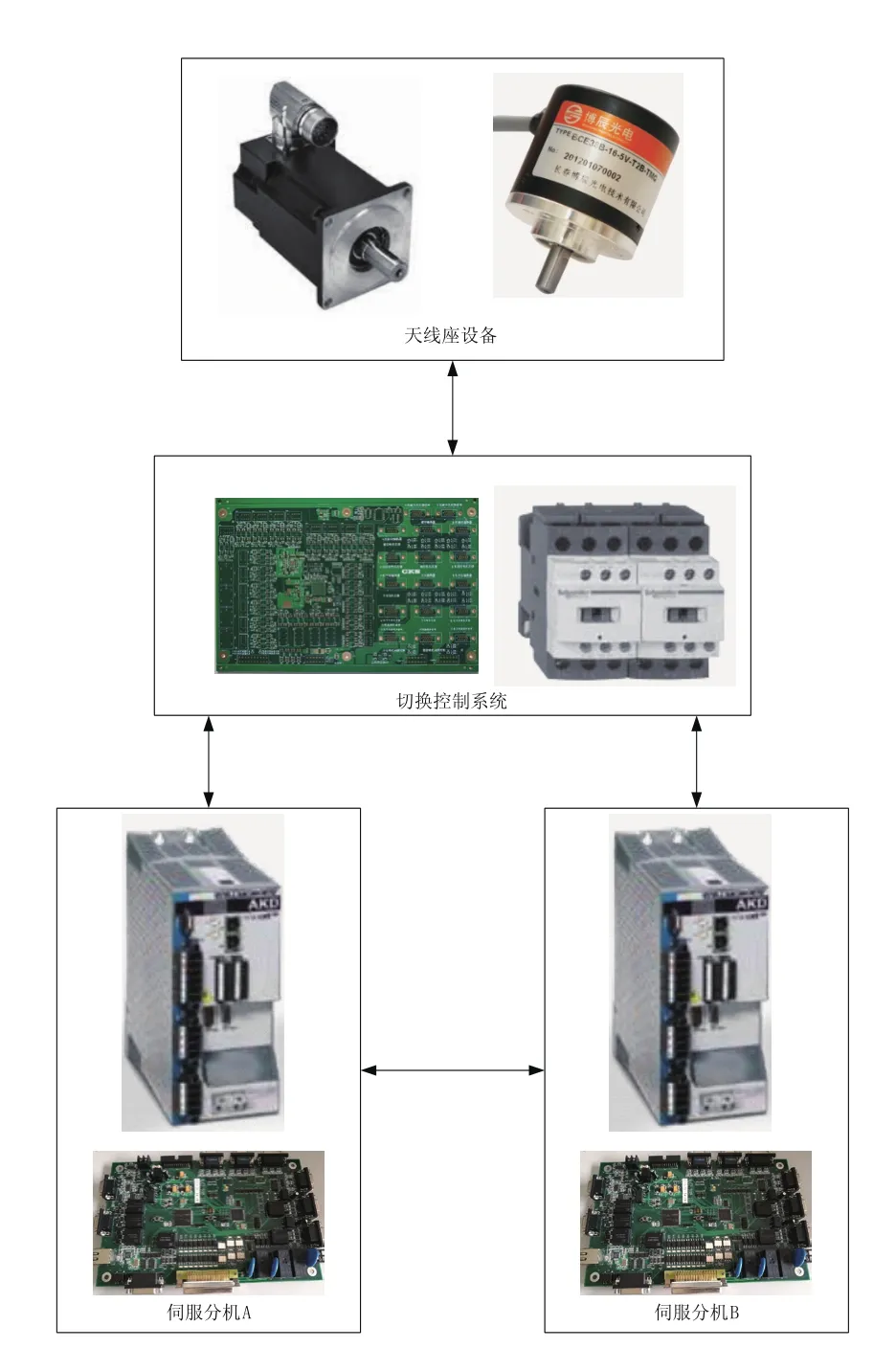

图1 双机冗余系统

如图1所示,伺服系统由两套相同的伺服分机A和伺服分机B(命名为A机和B机)、一套双机冗余切换控制系统(以下简称“切换控制系统”)以及一套天线座设备组成。对于单机来说,伺服主控单元接收到来自相对应上位机(通常为数据处理机)的工作模式指令,经过处理后发送运动指令到方位和俯仰电机驱动器,驱动电机使天线按要求运动;同时主控单元接收天线角编码数据和天线座控保信号,分别发送给信号处理和数据处理,通过显控单元显示当前的天线控制状态,并实现本控人机交互。

两套伺服系统完全等同且独立,同一时刻只有一个分机参与控制工作,所有的控制和功率信号都由该分机发出和接收,即“在线”,而另一台不参与控制工作的状态为“离线”。两套伺服分机只要有一套正常工作,就可以实现雷达伺服控制功能。当两个分机均处于正常状态下,可以通过人工进行切换,由数据处理对当前的“离线”方发出“在线”指令,在切换控制系统的流程配合下,等待另一方“离线”完成后,自动将自身切换为“在线”状态。当其中一个正常工作的分机出现故障后,可以由该分机自动发起切换流程,将自身“离线”,并通知对方“在线”。

2 硬件架构

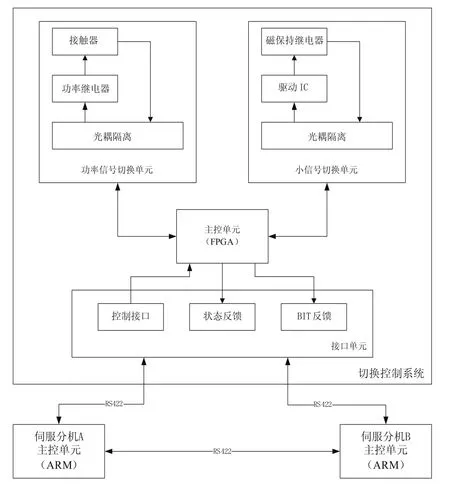

在硬件架构的设计上,充分考虑系统的可靠性和可扩展性。整个双机冗余切换由伺服分机内的主控单元和切换控制系统的主控单元相互协同实现。伺服主控单元负责整个伺服算法和与各个外设及分系统的接口,主控芯片选择基于C语言编程的ARM处理器,便于算法的实现。切换控制系统的主控单元一方面要完成各个继电器回路的切换时序等相对固化的逻辑控制,可靠性要求很高;另一方面需要进行智能化的BIT检测并与伺服分机通信,具有相对灵活性。因此,其主控芯片选择可运行IP软核的FPGA芯片。整体的硬件架构如图2所示,其中切换控制系统的硬件架构是本文的研究重点。

切换控制系统由一块基于FPGA的板载继电器组PCB,大功率接触器,以及辅助元件安装于控制插箱内,各个功能单元的组成和功能如下:

1)主控单元:主要由FPGA构成处理核心,采用Altera公司的Cyclone第四代FPGA芯片EP4CE10F17C8N,通过接口单元接收来自伺服分机的切换指令,通过光耦电路向功率信号切换单元和小信号切换单元发送切换控制信号并接收各路状态反馈,并通过接口单元向两个分机反馈当前状态和BIT。从FPGA片内结构规划上,对于功率信号切换和小信号切换单元的控制,属于逻辑控制,采用硬件描述语言将其固化在片内LEs中,形成硬件化的切换控制,保证高度的可靠性。与接口单元涉及到通信协议和BIT检测方式等需要灵活处理的软件化管理,采用在Nios II软核上用C语言进行用户自定义的方式进行设计编写。

图2 双机冗余系统硬件架构

2)功率信号切换单元:由4路功率继电器带动4路三相交流接触器,实现功率级即电机的切换。对于一个控制切换回路,如方位回路,对应的A机和B机功率接口接入切换单元,输出一路功率接口接入方位电机。功率继电器采用周期性脉冲驱动,从而大幅降低线圈吸合电流,延长工作寿命,提高系统可靠性。每1路功率继电器输出控制1个交流接触器线圈,并获得该路接触器辅助触点的反馈。更进一步地,除了在FPGA的控制输出上保证不会出现两路同时导通外,还利用交流接触器的辅助触点构成硬件互锁,确保不出现A机和B机的功率接口同时接入方位电机导致严重故障的情形。

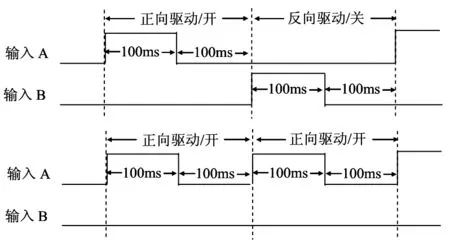

3)小信号切换单元:由驱动IC带动微型继电器,实现小信号(如电机旋变信号和电机抱闸信号)的切换,包含20路模拟信号和4路直流信号。对于一个控制切换回路,对应的A机和B机小信号接口接入切换单元,输出一路小信号接口接入方位电机。信号切换采用欧姆龙G6SU-2磁保持继电器,驱动IC均采用BL8023D,每个继电器为双刀双掷,其中1路做输出,另一路做状态反馈,FPGA到驱动IC,以及反馈信号到FPGA之间都经过光耦隔离。磁保持继电器提高整个系统的可靠性。驱动采用周期性脉冲驱动,A、B的输入状态每隔200ms刷新一次,驱动脉冲宽度为100ms,脉冲与脉冲之间间隔为100ms,如图3所示。

图3 磁保持继电器驱动脉冲

4)接口单元:通过接口芯片AM26C32获取伺服分机的2路RS422差分切换控制信号,分别代表A机离线/在线和B机离线/在线,将差分信号转换成单端电平并传递给主控FPGA,同时将FPGA给出的单端信号通过接口芯片AM26C31转化为RS422差分信号,向伺服分机反馈当前两个分机的在线/离线状态,并通过RS422串口与伺服分机通信反馈自身的BIT故障信息。

3 软件实现及系统验证

冗余系统的软件实现上包含两套完全相同的伺服分机的ARM软件和切换控制系统的FPGA逻辑程序。切换控制系统内部,两个分机之间,以及分机与切换控制系统之间的协同工作流程,是本文的重点研究对象。

3.1 切换控制系统FPGA软件实现

在片内LEs实现的硬件逻辑如下:

1)接口单元通过硬件获取切换分机的两路切换控制指令,A_CMD和B_CMD,分别代表A机离线/在线和B机离线/在线的控制指令;为了避免线路干扰导致切换错误, FPGA采取多次定时采样后确认并锁定输入;

2)FPGA每隔规定时间读取由微型继电器反馈的状态信号,多次采样锁定反馈状态,并且传递给内部的BIT;

3)FPGA每隔规定时间读取由接触器辅助触点反馈的“在线/离线”信号,其中,A机2路(分别为方位和俯仰回路),B机2路(分别为方位和俯仰回路),对于A机或B机来说,必须2路为相同状态才认为信号有效,多次采样并锁定反馈状态,同时通过接口单元输出2路差分信号A_FBK,B_FBK作为状态反馈给两个伺服分机,A机和B机均可获取两个分机的状态;

4)FPGA根据当前的控制命令,进行相应离线或者切换动作。其中,切换的动作为:先同时切换小信号继电器至在线一方,并检测全部信号的反馈已切换完毕之后,“在线”指令对应的接触器得电,同时相应的接触器反馈信号接入FPGA。

同时在IP库中调用Nios II处理器,挂载到32位Avalon总线上,利用软核进行自检测和故障上报,即BIT功能:

1)任意一个微型继电器的反馈与给定逻辑不一致,并且长达给定的时间后,强制A机、B机离线,BIT报故障;

2)任意一个功率继电器对应的接触器的反馈与给定不一致,并且长达给定的时间后,强制A机、B机离线,BIT报故障;

3)当2路切换控制指令均为“在线”(A_CMD=1,B_CMD=1),并且长达给定的时间后,强制A机、B机离线,BIT报故障。

3.2 协同软件实现

在系统工作逻辑的基础上,系统双机切换功能需要伺服分机(ARM)与切换分机(FPGA)协同工作来实现。三种典型场景分布以及具体实施过程如下:

场景1:A机和B机均正常,且均处于离线状态。当A机接收到数据处理的“在线”指令,并且通过控制切换系统的反馈检测到B机为“离线”,则A机发出A_CMD=1给切换控制系统,切换系统先后将小信号继电器和功率继电器切换至A机侧,当A机检测到反馈为A_FBK=1时,A机启动(加使能)正常投入工作。

场景2:A机和B机均正常,A机处于在线工作状态,B机离线。有如下两种情形:

1)当A机接收到数据处理的“离线”指令,A机停机,去使能,然后A机发出A_CMD=0给切换控制系统,进行A机离线动作,这种情形A机不主动通知B机在线;

2)当B机接收到数据处理的“在线”指令,通过之间的互联总线发送指令通知A机离线,A机接收到指令后发出A_CMD=0给切换控制系统,进行A机离线动作;当B机检测到A机的状态反馈A_FBK=0后,发出B_CMD=1给切换控制系统进行切换动作,使得B机在线,当B机检测到B机的状态反馈B_FBK=1后,B机启动(加使能)正常投入工作。

场景3:A机处于在线工作状态,B机离线,此时A机自身发生故障,A机停机,去使能,然后A机发出A_CMD=0给切换控制系统,进行A机离线动作,当A机检测到A机的状态反馈A_FBK=0后,通过互联总线发送指令通知B机在线,B机接收到指令后发出B_CMD=1给切换控制系统进行切换动作,使得B机在线,当B机检测到B机的状态反馈B_FBK=1后,B机启动(加使能)正常投入工作。

3.3 实现与验证

采用2套相同的伺服驱动系统(含ARM伺服主控板+科尔摩根AKD-00606伺服驱动器)和1套切换控制系统(含FPGA切换控制板和交流接触器)对应1套天线座设备(含科尔摩根AKM33伺服电机和BCE38BS6型绝对值编码器),通过电缆连接组成双机冗余伺服实验系统,如图4所示。

图4 双机冗余伺服实验系统

测试过程分为主动切换和被动切换。现令A机以PPI模式(即按给定速度连续扫描)工作,B机离线。主动切换测试中,将A机伺服驱动器电机反馈插头拔掉,人为制造A机故障。被动切换测试中,在数据处理机中向B机发送“在线”指令。经过多次重复测试,实验结果表明,切换触发后,均能够顺利实现A机停机、去使能、离线之后,B机小信号和功率信号先后切换,在线、加使能,并接管A机的工作模式实现PPI,切换过程柔性化,BIT反馈正常。

4 结束语

本文针对现有技术的不足,采用混合冗余配置,提出并研究一种基于ARM和FPGA协同的雷达伺服双机冗余切换控制系统,在讨论了其系统组成、硬件架构、软件流程后,通过搭建实验系统进行了功能验证。系统在设计上以高可靠性硬件为基础,结合严密的软件逻辑实现,并通过灵活的BIT反馈使故障排查可视化,大大降低后期维护成本,可推广应用至高可靠性要求的机场天气雷达系统和其他有相关要求的雷达系统中。