机载高速内存映射异构平台波形建模方法

李 鹏,孙 学,路小超

(中国电子科技集团公司第十研究所,四川 成都 610036)

0 引 言

如何实现标准化的波形建模方法,缩短系统开发时间,是目前机载传感器系统开发过程中需要解决的关键问题之一[1,2]。

国外F35采用开放式架构实现了机载传感器数字部分及射频前端的综合,通过标准的信号与数据处理单元完成传感器和任务设备的信号与数据处理,实现了通信导航识别、雷达及电子战等多项无线传感器功能[3,4]。借助开放性、模块化和通用化的硬件平台,F35进一步借鉴了软件无线电思想,将各种功能如工作频段、调制解调和通信协议等使用软件模块完成,以研制出具有高度灵活、开放性的新一代无线通信系统[5]。JTRS联合项目办公室发布的软件通信体系结构SCA2.2.2标准,标准化了波形的建模和开发流程。为了实现波形与硬件解耦,后续又发布了MHAL[6]和MOCB[7]规范,但是鲜有基于这些中间件的规范化波形建模与开发流程。

目前,机载平台中已大量使用如RapidIO等支持高速内存映射机制的数据总线。然而在大规模系统应用中,内存空间划分与地址规划复杂,缺乏规范化建模和管配方法,应用中还经常面临如下问题:①平台异构特性封装需求;②波形高带宽和动态部署需求;③标准化波形建模方法需求。本文将基于高速内存映射机制通信总线,结合JTNC MOCB标准,提出了一种规范化的波形建模方法,解决上述波形开发中面临的问题。

1 机载高速内存映射异构平台

机载高速信号处理机主要用于完成机载各种传感器的信号与信息处理及其它运算控制等功能,是航电系统的重要组成平台,通常具有如下特点:

(1)遵循标准的综合化开放式系统结构,采用通用化、多目的和标准化的数据和信号处理模块,支持资源冗余和灵活可变的硬件线程重组设计,提升系统的可扩展性和可靠性;

(2)集成通用的高性能异构类型处理单元,如MPC8640和P2020、TMS320C600系列多核DSP、Xilinx K7系列FPGA。在满足不同波形高性能信号解算、数据处理等运算需求的同时,避免器件种类的多样化;

(3)使用高性能的分布式互连总线,如RapidIO总线等[8,9]。RapidIO 1.x标准支持的信号速率为1.25 Gbps、2.5 Gbps和3.125 Gbps。借助高速交换芯片如CPS-1848(支持12路4x或18路1x)、TSI578(支持8路4x+8路1x或16路1x)和互联背板可以实现模块内部和模块间的高速数据传输,能够支持目前CNI、电子战和雷达的波形应用需求。后续发布的RapidIO 2.x标准在兼容RapidIO 1.x标准基础上,增加了支持5Gbps和6.25Gbps的传输速率[10],对满足未来机载波形高速通信需求提供了有效的技术保障。

虽然RapidIO规范支持消息通信、全局共享内存(GSM)和直接输入输出(DIO)等多种通信机制,为了支持高速机载波形的数据交互需求,本文采用RapidIO DIO内存映射通信模式构建高速的异构处理器互联通道,以满足波形的数据交互需求。

图1给出了基于RapidIO的机载高速信号处理机资源互联,其中包含了各类计算单元处理板,板内单元通过高速交换芯片进行互联,并通过交换芯片连接至交换模块,实现板间的数据通信。交换板预留与外部的互联接口,实现与射频系统以及其它高速处理单元的互联。

集成开放式体系架构、通用处理单元和高速互联总线的机载异构处理平台,为实现波形的建模开发,提高系统开发效率和波形复用率提供了一个更加标准化的运行环境。

图1 机载异构平台资源互联

2 E*MOCB硬件抽象层

JTNC办公室于2013年公布了MOCB 1.1.5版应用编程接口规范,用于支持GPPs、DSPs和FPGAs上波形组件间的高速数据互联通信[7]。区别于MHAL,MOCB是进一步对内存映射类型通信机制接口的封装和组件数据传输通信的规范,适用于高速、大数据量的数据通信需求。本文参照MOCB 1.1.5版规范,结合实际应用需求实现了E*MOCB硬件抽象层中间件。

2.1 关键概念

E*MOCB定义了如下关键概念:

逻辑地址(LD):表示波形组件的逻辑ID,与平台无关。波形组件间使用逻辑地址进行通信;

事件(Event):与波形组件相对应,当事件分发寄存器状态改变时需要触发事件发生;

子事件(SubEvent):对应于事件分发寄存器中的一个状态位,通常用于区分不同源端触发的相同事件信息。子事件与一个信号量关联,子事件状态的改变将触发事件的发生;

事件分发寄存器(EventMux):每个事件对应一个事件分发寄存器,用于存储子事件相关状态信息,寄存器的长度由关联的子事件个数决定;

占用状态位(IU):表示数据的忙闲状态,用于实现数据收发端的内存互斥访问和流控等操作;

连接(Connection):表示源端与目的LD之间的一条数据通路。对于每个处理单元上提供的LD,所有与其关联的子事件都对应一条连接。

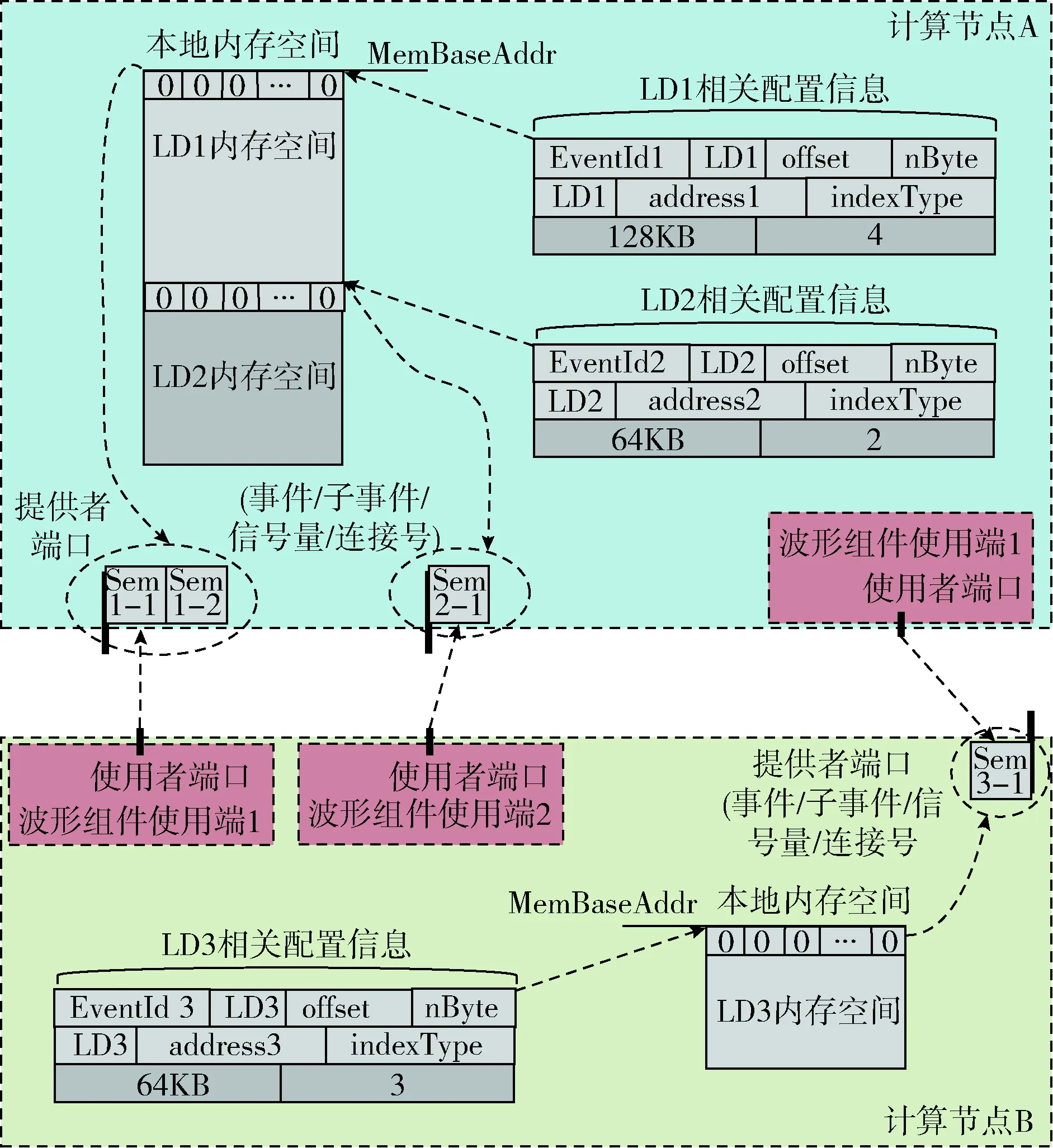

基于内存映射机制的波形组件数据交互,需要根据节点上波形组件的使用需求,完成内存块大小及地址的划分,避免出现数据重叠等问题。图2在上述概念基础上给出了接收端包含3个逻辑地址的内存划分的示例,以及关联的事件/事件分发寄存器映射配置信息。

图2 E*MOCB波形组件内存资源分配

2.2 波形侧与驱动侧接口规范

如图3所示,波形侧接口用于描述波形组件与E*MOCB之间的标准化通信接口规范,该部分接口在GPP和DSP、FPGA平台上保持一致;驱动侧接口用于描述E*MOCB与内存映射类型通信总线驱动之间的接口要求。为了适应不同内存映射机制总线差异,需要实现对应的驱动接口适配模块。

图3 E*MOCB波形与驱动侧接口使用场景

根据应用需求,本文实现如下波形侧C语言接口(FPGA部分接口与规范保持一致,这里不作说明),包括非阻塞读、阻塞读、非阻塞写、阻塞写、LD地址映射配置和事件配置等,具体接口定义及参数说明请参阅MOCB1.1.5版规范[7]:

mocbRead:实现本地组件的非阻塞数据读取;

readWait:实现本地组件的阻塞式数据读取,阻塞时间可以通过参数设置;

mocbWrite:实现对远端数据非阻塞写功能;

writeWait:实现对远端数据的阻塞写功能,阻塞时间可以通过参数设置;

configLDMap:配置LD与内存地址的映射关系;

registerEventMux:用于给波形组件使用的事件分配事件分发寄存器空间;

registerSemaphore:用于建立事件、子事件以及波形软件管理的信号量之间的关联关系;

unregisterSemaphore:用于注销信号量。

通过E*MOCB屏蔽了异构平台的硬件差异,波形的开发无需关注平台相关信息,从而提高波形的可移植性和可复用性。

然而,由于各平台提供的总线驱动接口可能存在差异,为了进一步提高E*MOCB的平台可移植性,适配不同的内存映射机制高速互联总线,这里进一步约束了GPPs和DSPs上驱动侧接口形式:

(1)事件发送接口:

MOCBErrorCodes eventIdWrite (

unsigned short eventId,

struct MOCBPhyAddr addr);

(2)子事件发送接口:

MOCBErrorCodes subEventIdWrite (

unsigned short subEventId,

struct MOCBPhyAddr addr);

(3)数据写接口:

MOCBErrorCodes dataWrite (

unsigned int dataLen,

unsigned char* data,

struct MOCBPhyAddr addr);

(4)数据读接口

MOCBErrorCodes dataRead (

unsigned int dataLen,

unsigned char* data,

struct MOCBPhyAddr addr);

对于异构平台,需要在不同的总线驱动上封装上述接口,并利用E*MOCB提供的注册接口完成不同类型总线收发接口的挂接,以避免由于驱动的不同对E*MOCB中间件带来的修改。

3 波形建模及描述方法

3.1 基于E*MOCB的波形建模方法

内存映射通信机制下的波形建模需要考虑内存划分、数据包缓存、流控和数据覆盖等问题,借助E*MOCB中间件,可以实现对内存区域的合理管控,满足高性能、灵活复杂的数据通信需求。基于E*MOCB的波形建模应遵循如下流程:

(1)采用自顶向下的方式进行波形资源需求分析,确定所需的计算资源类型和数量;

(2)采用逆向自底向上的原则进行每个计算单元上的波形组件建模,确定波形组件的划分方法,每个波形组件需要提供服务的端口数量、接收数据包的大小、缓存数据包的数量等;

(3)确定波形组件间的交互关系,建立提供者端口与使用者端口之间的连接关系,完成波形的数据通信关系建模。

图4给出了一个波形建模示例,由运行在计算节点A和B上的3个波形组件构成,其中计算节点A包括两个波形组件,对应于LD1和LD2,LD1具有两个提供者端口(即LD1对应的波形组件支持最多两个使用者),每个提供者端口支持的接收数据包长度最大都为128 KB,最多可以缓存4包数据,LD2包括一个提供者端口;计算节点B包括一个波形组件,对应于LD3,具有一个提供者端口。计算节点A需要使用B节点LD3的提供者端口,而计算节点B需要使用A节点LD1的第一个提供者端口和LD2的提供者端口。节点间使用端口和提供端口调用关系通过连接进行表示。

图4 基于E*MOCB的波形建模

3.2 波形描述方法

波形描述是将波形对象抽象并描述成具有逻辑关系的数据表达方式,其目的是在不同数据使用者之间共享数字化的事务描述,常用的描述方法如XML等。考虑机载环境的存储及解析复杂度问题,本文采用了更易于解析的Json格式进行波形模型描述。Json是一种更加简洁高效的形式化描述工具,允许通过使用自定义格式、标识、交换和处理数据库可以理解的数据,具有完善的解析和封装支持[10]。

波形描述分为波形、组件和连接关系描述3部分。波形描述是顶层描述,涵盖组件和连接等。波形组件描述项包括:事件、子事件、内存地址划分和内存大小等。连接关系描述项包括:使用端节点ID、提供者组件LD和子事件ID等。

如下给出了图4所示模型的部分描述示例:

/*波形描述示例*/

{ “wvID”: “DCE: WAVEDEMO”,

“wvName”: “WAVEDEMO”,

“wvDevice”: [ { “wvDeviceType”: “DSP”,

“wvDeviceID”: “DCE:A”,

“wvDeviceComponent”:

[/*组件描述*/]},

{ “wvDeviceType”: “PPC”,

“wvDeviceID”: “DCE:B”,

“wvDeviceComponent”:

[/*组件描述*/]}

],

“wvConnection”: [/*连接关系描述*/]

}

/*组件描述示例*/

{/*计算节点B上组件描述*/

“ComponentName”: “COMLD3”,

“MemSize”: 0x40000,

“MemAddr”: 0x80000000,

“ComponentLD”: LD3,

“EventID”: EventId3,

“RecvPktMaxLen”:0x10000,

“BufPktNum”:3,

“SubEventNum”: 1,

“SubEvent”:[{“SubEventId”:0,

“Connection”:0,

“Offset”:8}]

}

/*连接描述示例*/

{ ConnectionSum:3,

/*计算节点A到LD3提供者端口的连接描述*/

ConnectionInfo: [

{“ConnectionID”: 1,

“SrcDeviceID”: “DCE:A”,

“DstComponentLD”: LD3,

“DstSubEventId”: 0},

…]

}

波形建模时采用“接收方规划,告知发送方结果”的模式,每个组件规划自己的提供者端口实现,使用者通过连接关系获取提供者端口信息。在进行数据发送时,系统控管软件通过解析波形描述文件,同时结合组件实际部署位置信息,完成平台相关部分的配置。

4 波形动态部署运行

波形的建模与实现具有平台无关性,实际应用中需要根据物理资源状态信息完成波形部署运行[11]。

如图5所示,在逻辑层面,波形组件之间的数据收发仅需要通过调用E*MOCB提供的标准通信接口和逻辑地址完成,无需关注具体的实际部署情况;在物理部署层面,系统控制管理软件根据波形模型和组件部署位置信息计算并完成对组件所在节点E*MOCB的配置,建立逻辑地址到物理地址的映射关系,中间件通过调用具体的底层总线驱动将数据发送到对方,对方节点E*MOCB收到数据后根据LD等信息将数据路由给对应的波形组件,从而实现应用数据的通信。当波形组件部署位置发生变化时,只需要重新计算部署节点上的路由信息,并完成对E*MOCB的配置,就可实现波形的动态部署运行。

图5 异构平台的波形动态部署

5 实验验证与分析

如图6所示,实验部分使用由运行于PPC、DSP和FPGA这3类处理器上的6个波形组件构成的波形样例进行测试。

图6 测试波形样例

该波形的功能和运行流程如下:FPGA上的组件1作为测试数据源,调用组件2和组件4提供的端口,间隔向这两个组件发送长度为512 KB的数据,组件2(完成相邻奇偶位置数据相加后对16取模)和组件4,组件3(完成相邻奇偶位置数据相乘后对16取模)和组件5具有相同的处理功能,组件3和组件5将处理完的数据发送到组件6(具有两个提供者端口),组件6对组件3和5发送的数据进行对比。测试中数据的发送采用阻塞模式,以匹配不同类型处理器的运算速度差异。波形组件的关键配置信息见表1。

表1 波形组件关键配置信息

实验中,在某预研项目的综合信号处理机(ISP)中进行了测试。ISP内集成了通用的数据和信号处理模块,处理器包括P2020、TMS320C6678和Xilinx X7K325T等高性能处理单元,处理单元间通过高速交换芯片CPS-1848进行RapidIO总线互联,实现4×3.125Gbps模式高速数据传输。

测试时,首先由ISP控制管理程序对测试波形描述进行解析,接下来按照波形描述、所需物理资源及RapidIO连接关系进行波形组件部署及节点的E*MOCB中间件信息配置,最后根据组件间的逻辑连接关系建立节点间的RapidIO链路层连接关系。

完成部署和配置后,启动各节点的程序,并触发COM1组件发送数据。通过测试结果可知,波形运行正常,组件6从组件4和5接收的处理结果数据相同。测试中,所有组件都采用了阻塞式流控发送模式,如果接收端处理速度慢,且缓冲已满,则触发发送端进行流控。测试的整体数据带宽受RIO总线性能以及各节点处理性能的影响。因为使用了流控机制,因此不存在数据包丢失的情况。据测试,对于512 KB数据,中间件收发数据带宽可达7 Gbps以上,为更好实现机载传感器功能集成提供了保证。

测试用例中,在各组件中实现了数据的加、乘和对比等运算,通过更改组件功能就可快速构成其它的波形功能。通过本文提出的方法,在完成波形数据通信流程建模后,波形开发者只需要在组件内添加具体功能实现,无需关注通信细节,可以显著提升波形复用率和软件开发效率。

6 结束语

本文针对机载高速内存映射异构平台,分析了大规模机载波形建模的应用需求,针对异构平台的建模环境,提出了基于E*MOCB硬件抽象层的内存映射总线底层封装方法和标准化的波形组件以及波形建模、描述方法,实现了波形与平台的解耦和规范化的设计与开发,规范了基于高速内存映射机制通信总线的机载异构平台波形建模,能够推进模型驱动的软件开发实践,提升波形软件的复用率。