FPGA图像边缘检测系统的设计与实现

叶惠娇 冉 全 成 果

(武汉工程大学计算机科学与工程学院 湖北 武汉 430205)

0 引 言

图像作为人类感知世界的视觉基础,是获取、表达及传递信息的重要媒介。其中,边缘信息是图像的基本特征之一,在实现特征提取、机器视觉等过程中起着关键作用[1]。

随着图像数据规模日渐庞大,其处理算法日益复杂,传统通用的软件处理平台逐渐满足不了处理速度及实时性的需求。FPGA具有流水线结构,在并行处理数据方面有一定的优势,可极大程度提高数字图像处理的速度[2]。本文设计一种基于FPGA的图像处理系统,集图像数据采集、存储、算法处理、显示等功能于一体。同时,针对传统Sobel算法需要人为设置阈值所带来的缺陷,引入中值滤波的思想来生成自适应动态阈值,更加准确地提取图像边缘信息[3]。

1 系统架构设计

硬件平台可分为图像采集模块、存储模块、处理模块及显示模块。选用Altera公司的Cyclone IV 系列FPGA芯片为控制核心,协调控制SD卡和LCD显示屏的驱动、SDRAM存储器的数据转存,并且实现对图像数据的算法处理。系统总体框架如图1所示。

图1 系统总体框架

(1) 数据获取模块 通过计算机将图像数据存储到片外SD卡后,将SD卡插入硬件平台的卡槽中。在SPI模式下,SD卡采用发送应答机制,通过时钟、片选、数据输出、数据输入4条总线以串行方式与FPGA进行数据传输,其时钟控制频率为25 MHz[4]。

SD控制器由初始化和读写操作组成,表1是系统需要用到的SD卡控制命令。FPGA向SD卡发送CMD0命令以进入初始状态,发送CMD8、CMD55和ACMD41命令并返回无误后确定SD卡的协议,完成SD卡的初始化;发送CMD17命令,以扇区为单位连续读取SD卡中的数据,直至读到结束字节0xFE[4]。

表1 SD卡常见命令

(2) 存储模块 存储模块由RFIFO、WFIFO和片外芯片SDRAM组成。FIFO是一种顺序读写的数据缓存器,由于没有外部读写地址线,所以使用简单,同时能解决不同时钟频率模块间传输数据的问题[5]。SDRAM存储器的时钟控制频率为100 MHz,内存大小为256 MB,其中含有4个Bank存储块,每个Bank的内存为4 MB,数据位宽为16 bits,能满足显示模块对数据传输速率的需求。

在FPGA的控制下,SDRAM存储模块中的WFIFO将SD卡中的图像数据写入片外的SDRAM芯片中进行缓存,RFIFO则将SDRAM芯片中的数据以串行方式读出,这个过程中的数据都是16 bits。

(3) 处理模块 当存储模块接收到来自显示模块的“读数据请求”信号时,RFIFO将16 bits数据从SDRAM中读出传输至算法处理模块。但是,图像边缘检测一般是对像素的灰度值进行处理,即需要将24 bits的真彩色图像数据转换为8 bits的灰度图像。转换方法有浮点算法、整数方法、均值法、移位法以及仅取绿色五种。本文直接提取每个像素的绿色通道的数据作为其灰度值[6],使用一个数据转换模块将其转换为24 bits数据后,再提取其中的绿通道数据传递给图像处理模块进行数据处理。

(4) 显示模块 显示模块所采用的LCD液晶屏的大小为4.7英寸,可显示分辨率为480×272的彩色图像。因此,本文将480×272大小的真彩色图像作为研究对象,每个像素由R、G、B三个颜色通道,每通道一个字节数据共同控制色彩信息。LCD显示器采用SYNC接口模式,由行同步信号HSYNC和列同步信号VSYNC共同控制数据传输的时序[7]。即当LCD控制器完成行扫描和列扫描,HSYNC和VSYNC同时有效时,显示模块会向存储模块发送“读取数据请求”信号,以驱动数据的传输。

2 自适应阈值Sobel算法分析与实现

数字图像可被看作二维离散矩阵,使用MATLAB软件可得到图像的像素矩阵。图2是一幅分辨率为480×272的真彩色图像的像素矩阵。其中,每个数值代表一个颜色通道的分量,图2方框中的三个数据依次是一个像素点的R、G、B三个通道的数值。

图2 图像像素矩阵

2.1 传统Sobel算法

边缘检测是将一幅图像中亮度变化明显的点标识出来,剔除不相关信息,同时保留图像重要的结构属性。Irwin Sobel提出的Sobel边缘检测算法属于查找类算法[8-9],通过计算每个像素的灰度值的一阶梯度变化来判断边沿的位置。采用两组3×3模板作为水平卷积核和垂直卷积核,对图像的每一个像素点的灰度值,计算它的邻域像素与卷积核的卷积,分别得到图像在该点的水平梯度Gx和垂直梯度Gy:

(1)

(2)

式中:A是3×3像素矩阵,然后将两者结合求出其均方根作为实际梯度:

(3)

最后将梯度与人为设定的阈值θ相比较,确定其是否为边缘:

(4)

Sobel算法原理较为简单,易于在FPGA上实现。但是,该算法需要人为设定阈值,并通过大量实验进行验证,以确保选择最合适的阈值,取得良好的检测结果。在实际情况中,对于不同图像而言,取得最佳效果所需要的阈值各不相同[10-11]。因此,本文引入中值滤波的思想,根据被测图像的局部像素信息生成自适应动态阈值,有效解决以上两个问题,进一步提高检测精度。

2.2 自适应阈值

中值滤波算法使用一个奇数窗口,如3×3窗口、5×5窗口,对图像进行扫描,将窗口内的所有像素灰度值进行大小排序后,取中值作为该窗口中心点的灰度值,从而抑制噪声。

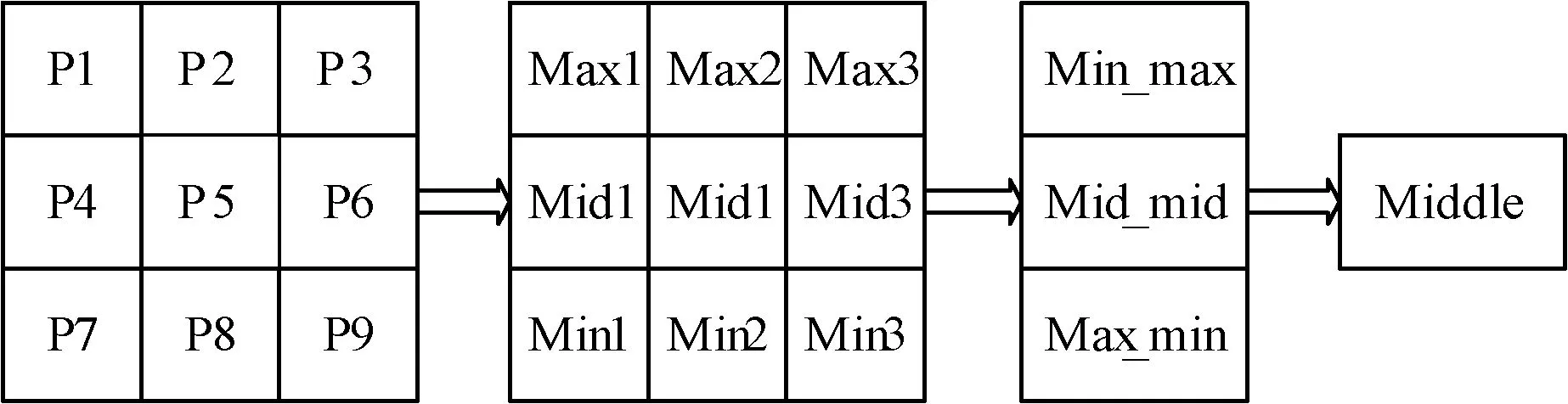

张琪等[12]采用中值滤波思想生成自适应动态阈值,本文在此基础之上做出了改进,其过程如图3所示。首先,按列对3×3窗口像素进行排序,得到每一列的最大值、中间值、最小值,将第一行像素归为Max组,第二行像素归为Mid组,第三行像素归为Min组;其次,再一次排序,依次提取Max组像素的最小值Min_max、Mid组像素的中间值Mid_mid、Min组像素的最大值Max_min;再次,求出这三个值的平均值Middle作为阈值,与对应的梯度值G(x,y)进行比较,以确定是否为图像的边缘点[13]。随着像素位置的改变,阈值也会发生变化,因此,可直接将其应用到对不同图像的边缘提取中,所取得的图像边缘信息具有良好的适应性。

图3 中值滤波算法步骤

2.3 算法的HDL实现及仿真

2.3.1 生成3×3窗口

3×3像素矩阵是卷积运算和中值滤波的基础。调用Quartus库中的移位寄存器Shift-Register(RAM-based)IP core将数据转化模块输出的串行数据,以三行并行数据输出,其原理图4所示。其中,模块输入8 bits灰度数据,每行数据的长度定义为图像的宽,即480。同时寄存两行,以保证移位寄存器能并行输出三行数据。

图4 Shift-Register原理图

图5是Model Sim仿真软件对移位寄存器的工作过程进行仿真的结果。可以发现,数据从data_in接口连续进入移位寄存器,然后并行从tap2、tap1、tap0接口流出,每列有480个数据间隔,以确保并行数据与图像像素相对应。

图5 移位寄存器工作仿真结果

2.3.2 卷积与梯度合成

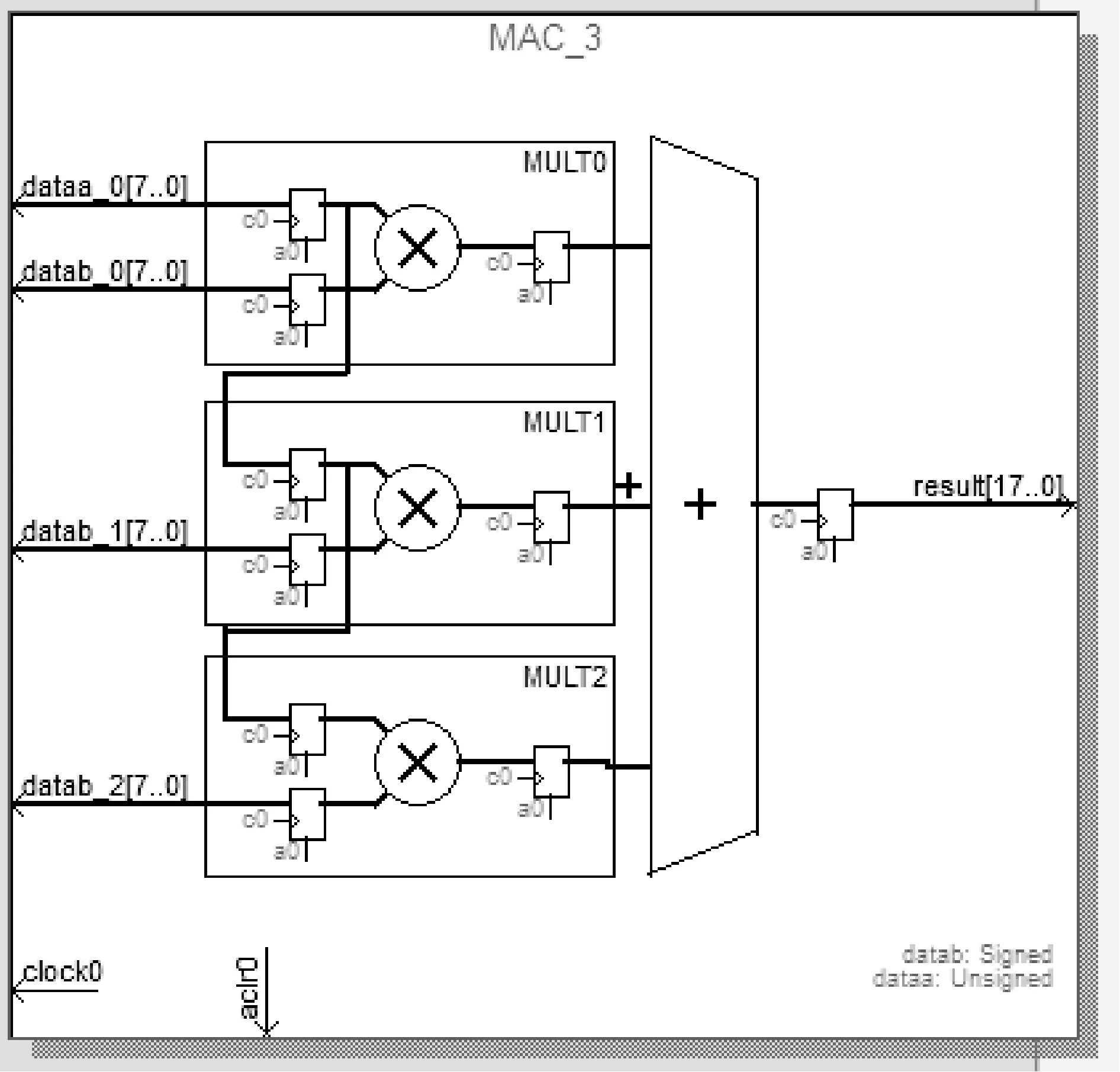

ALTMULT_ADD模块由乘法器和加法器组合而成,其原理如图6所示。数据流dataa_0分别与datab_0、datab_1、datab_2相乘之后,再相加。其中,当dataa_0与移位寄存器的数据输出端口tap0连接获取图像数据时,datab_0、datab_1、datab_2分别赋值为X9、X8、X7,实现像素矩阵的第三行数据与对应的水平Sobel算子的部分卷积。依此类推,完成一个像素矩阵与两组算子的卷积需要6个ALTMULT_ADD模块。

图6 ALTMULT_ADD模块

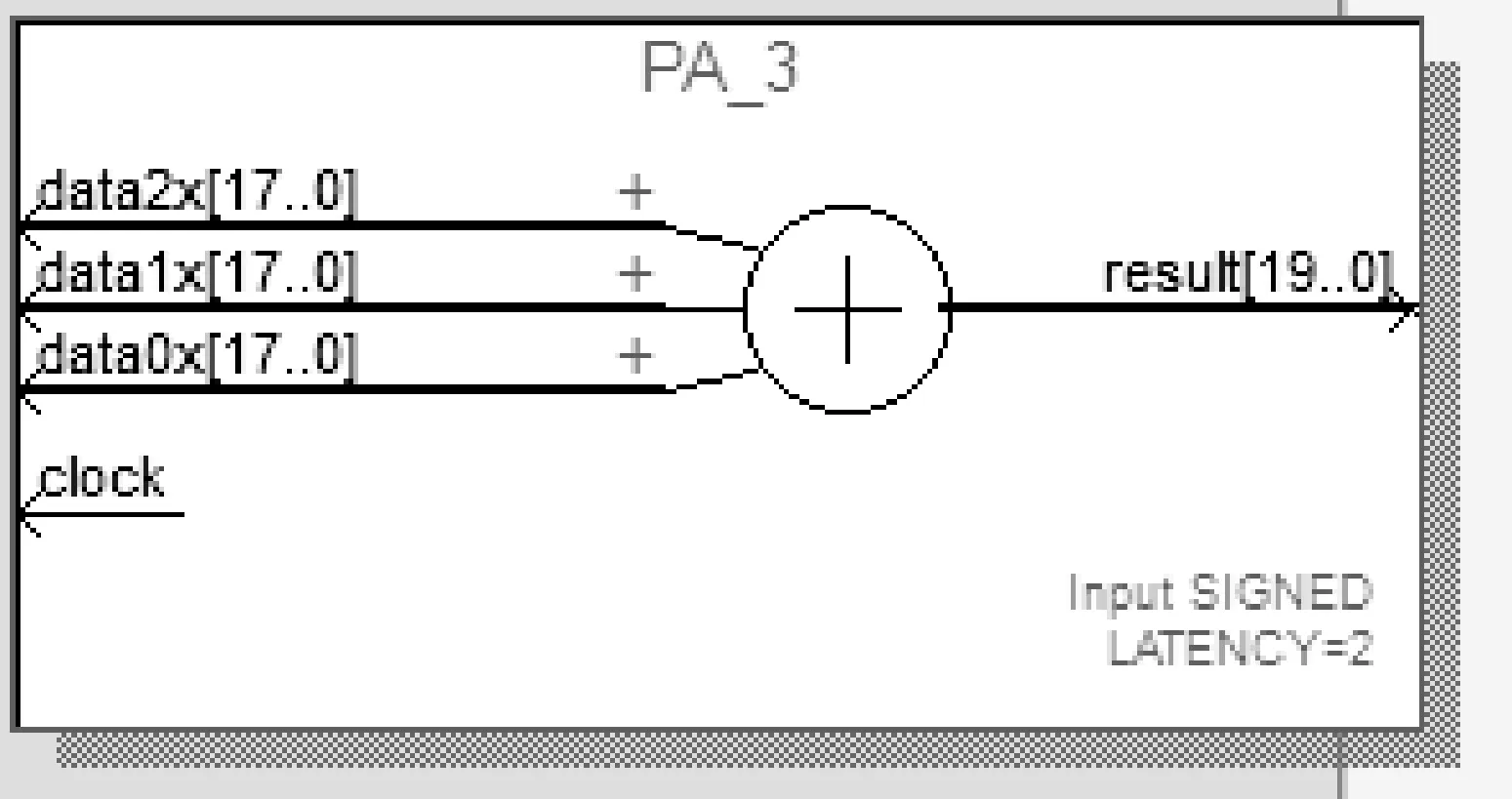

PARALLEL_ADD模块的核心是一个三路加法器,用于对ALTMULT_ADD输出的数据进行加法处理,如图7所示。因此,同时调用三个ALTMULT_ADD和一个PARALLEL_ADD则可实现一个Sobel算子与像素矩阵的卷积运算,得到水平梯度或垂直梯度。

图7 PARALLEL_ADD模块

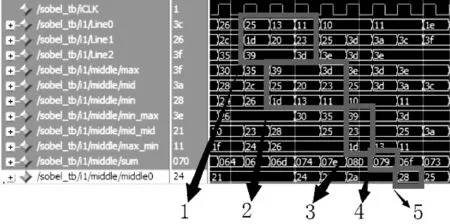

最后直接调用ALTSQRT模块,求得水平梯度与垂直梯度的均方根,即为图像的实际梯度G(x,y)。图8是卷积运算与梯度合成的Model Sim仿真图。其中,方框1是移位寄存器模块生成的一个3×3像素矩阵,中心像素为18。ALTMULT_ADD模块经过3个时钟周期,并行完成像素矩阵与Sobel算子每一行元素的累积运算,其结果分别为方框2和方框3。PARALLEL_ADD模块经过2个时钟周期,并行完成数据累加,其结果分别为方框4和方框5。ALTSQRT模块经过2个时钟周期求取实际梯度。该过程共消耗7个时钟周期,运算过程采用流水线结构。

图8 卷积运算仿真结果

2.3.3 生成自适应阈值

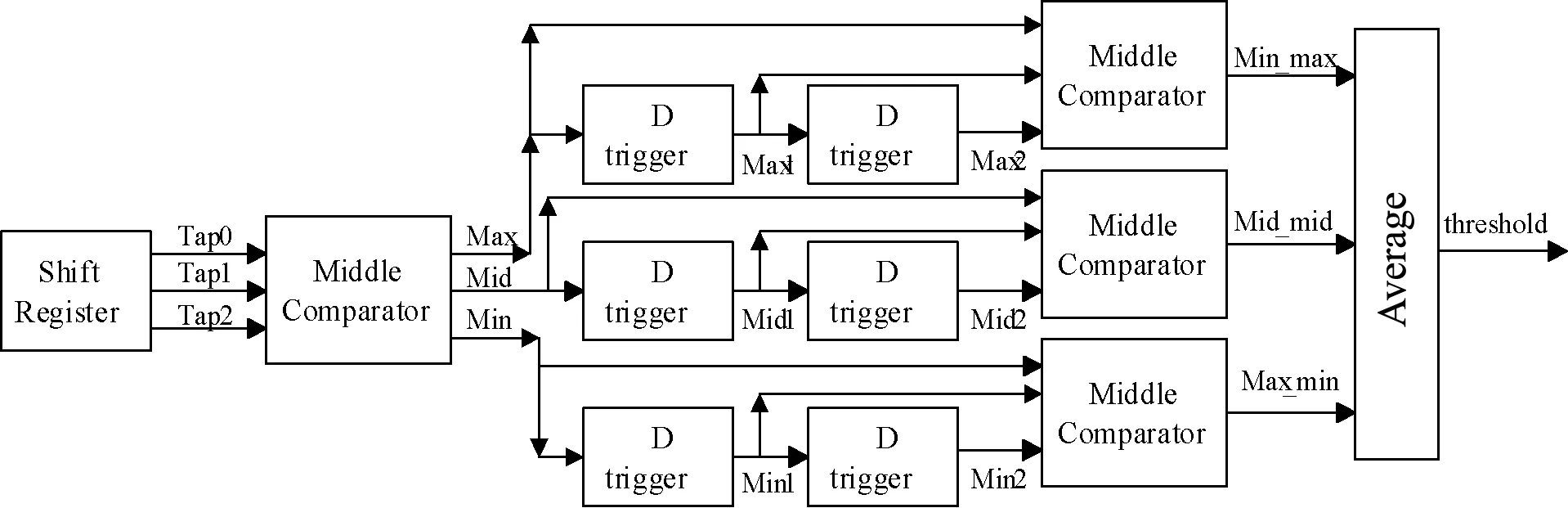

首先使用中值滤波器对移位寄存器输出的列数据tap0、tap1、tap2的大小进行排序,如图9所示,得到Max、Mid、Min三行数据。随后对每一行数据分别使用两个D触发器进行数据缓存,同时获取相邻的三个数据。使用滤波器对其进行排序,则可以得到Max组的最小值min_max、Mid组的中值mid_mid以及Min组的最大值max_min。最后求出三者的平均值作为局部区域的阈值。

图9 中值滤波模块

图10是中值滤波模块的仿真结果。其中:方框1是移位寄存器生成的3×3像素矩阵;方框2是第一次排序结果;方框3是第二次排序结果;方框4是min_max、mid_mid、max_min三者之和;方框5是最后生成即局部阈值,可以看出每一步消耗了1个时钟周期。因此,生成阈值后需要再次使用3个D触发器进行延时,以确保阈值与梯度的同步性。仿真结果表明,当使用50 MHz的时钟频率处理一幅分辨率为480×272的图像时,算法处理模块共消耗2.640 ms,流水线结构可有效提高算法处理的速率。

图10 中值滤波仿真结果

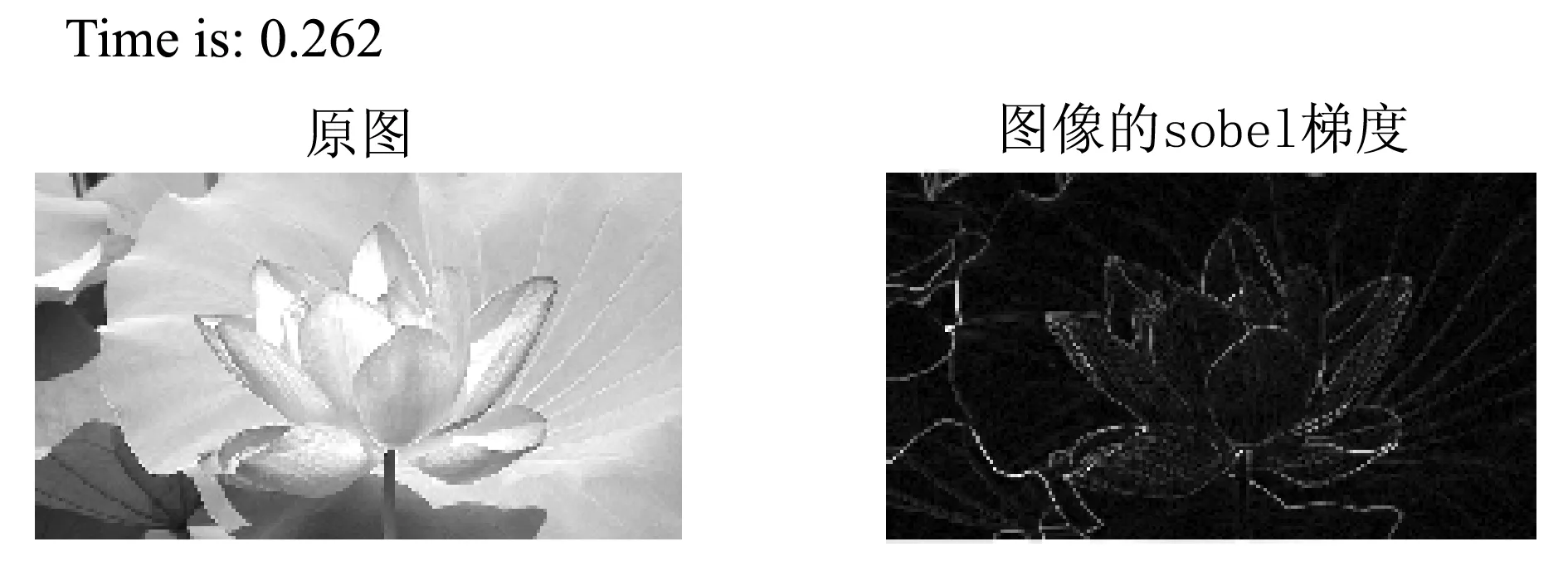

3 板级测试

为进一步验证系统的有效性,可在硬件平台上进行板级测试。图11是LCD屏幕显示的原始图像。图12是改进的自适应阈值Sobel算法检测的结果。其中:数码管显示了系统的运行时间,最高位“1”表示完成“读取图像数据——算法处理——显示检测结果”这一过程,最后两位“24”表示该过程共耗时24 ms。图13是使用MATLAB软件平台处理同一幅图像,共耗时约0.262 s,即262 ms。对比可知,两者都能完整地检测出图像的边缘信息,然而,以FPGA为控制核心的硬件平台处理图像的速度比软件平台快10倍以上。

图11 原始图像

图12 改进算法检测结果

图13 MATLAB仿真结果

4 结 语

本文采用硬件方案实现了并行的图像边缘检测算法,快速而准确地提取图像的边缘信息,为FPGA硬件平台实现更复杂的图像处理算法提供了基础。仿真及测试结果表明,硬件平台对图像的处理速度远远高于软件平台,系统实用价值较高。