基于预布去耦电容的片上电源噪声抑制策略

高成振,马永飞,孙战先,柯希明

(上海高性能集成电路设计中心,上海 201204)

0 概述

随着超大规模集成电路发展到纳米级工艺,集成电路的电源完整性越来越受到关注。特征尺寸的降低促使芯片在获得更高性能和集成度的同时,供电电压逐渐降低,电源网络中的Ldi/dt噪声变得越来越严重,最终导致芯片的可靠性设计面临具大挑战。

过高的电源噪声会降低晶体管性能,甚至导致逻辑失效,从而影响整个电路的可靠性。为将电源噪声控制在一定范围内,设计人员通常会在电源供电网络的多个层次(如板级、封装级和芯片级)选择性地添加去耦电容(decoupling capacitor,简称decap)[1-2]。每个去耦电容在局部相当于一个储能的电源,可以通过充放电调节局部电流,同时降低电源网络的阻抗,从而起到抑制电源噪声的作用。越靠近芯片,去耦电容容值越小,谐振频率越高,因此,片上去耦电容可以有效抑制高频电源噪声。

在28 nm工艺之前,考虑到去耦电容的添加容易增加芯片的泄漏功耗,大部分去耦电容插入算法都是在芯片的布局布线完成后进行的,目的都是用尽量少的去耦电容来达到有效降低电源噪声的效果。而在28 nm工艺之后,新型材料和结构的应用可以大幅削弱晶体管的泄漏功耗[3-4],因此,添加去耦电容时不必严格控制其数量。在此背景下,本文提出一种在布局布线之前预布一定数量去耦电容的策略,并设计多组实验探究工艺角、预布量、芯片利用率等因素对预布效果的影响。

1 相关研究

关于decap的插入和优化算法主要分为2类:基于敏感度的优化算法和基于电荷量的优化算法。

基于敏感度的优化算法以电源噪声较大的节点对decap的敏感度为约束条件进行优化。计算各节点的敏感度需要在优化过程的每一步都对电路进行瞬态仿真,因此,该类算法时间复杂度较高,中途需要存储的信息量也很大。文献[5]使用二次规划方法处理敏感度问题,并用分段线性化方法进行敏感度信息压缩存储,以减轻存储量的负担。文献[6]提出共轭梯度方法。文献[7]引入多重网格概念,简化了问题规模,并使用序列二次规划(Sequential Quadratic Programming,SQP)方法解决问题。文献[8]使用分治法将大规模电路划分为多个小模块。文献[9]在分治思想的基础上引入随机游走算法,其能够更合理地对整体电路进行划分。

2 片上去耦电容预布策略

2.1 去耦电容泄漏功耗

如前文所述,目前关于片上decap的研究多数集中在布局布线完成后解决decap的优化分配问题,其目的都是在有效抑制电源噪声的前提下尽量减少decap的添加量。

在CMOS工艺下,decap通常使用MOS管栅电容实现[15]。考虑到MOS管的结构特点,需要较大的栅电容来吸引电荷进入沟道,这就导致栅氧电介质必须很薄。随着特征尺寸不断变小,栅氧层越来越薄,栅极的泄漏电流将变得很大。在100 nm工艺以下,栅氧厚度每减小0.2 nm,栅极泄漏就增大10倍[16]。另外,MOS管尺寸按比例缩小还会使栅极的控制能力减弱,此时无法完全关闭沟道,最终导致漏极到源极的亚阈值漏电流增大。

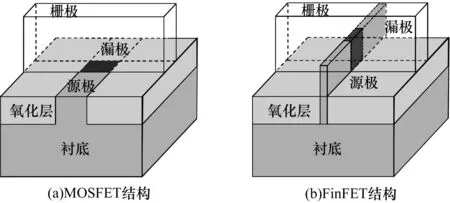

在工艺达到28 nm以后,由于采用了高介电常数电介质(high-k材料)和FinFET结构,MOS管泄漏电流过大的问题得到了极大缓解[17]。使用high-k材料能有效抑制栅极漏电流,而FinFET结构则将栅极做成类似钳子的排列结构,如图1所示,在MOSFET结构中,栅极与源漏区域间仅有一个平面接触,这能够限制栅极对沟道的控制;而在FinFET结构中,源漏区域在硅的表面形成了鱼鳍状结构,栅极包围了垂直鳍状源漏的3个面。这种结构增加了栅极的控制范围和控制能力,能够大幅缓解亚阈值漏电流过大的问题。

图1 MOSFET和FinFET结构示意图

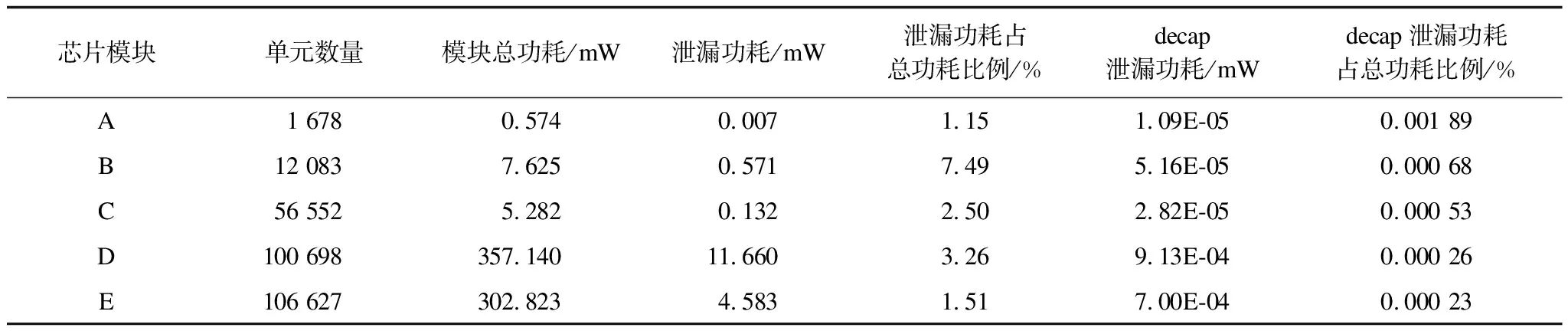

表1列出了28 nm工艺下某芯片不同模块的decap泄漏功耗占芯片总功耗的比例。在这些模块的设计过程中,布局布线完成后,decap被添加到所有的空闲区域,占整个模块面积的20%~30%。从表1可以看出,在28 nm工艺下,即使有大量decap被插入到芯片中,其泄漏功耗也仅占模块总功耗的0.000 2%到0.002%,几乎可以忽略。尤其是在计算量十分密集的高性能处理器中,decap引入的额外泄漏功耗与芯片总功耗相比更微不足道。

表1 decap泄漏功耗占模块总功耗比例

2.2 片上去耦电容预布流程

由于decap泄漏功耗的影响可以忽略,因此在进行decap插入时,不必刻意控制decap的插入量,即不必等到布局布线完成后才添加decap。为使decap得到更充足地插入,从而更有效地发挥降噪效果,本文提出在物理设计的早期,即布局布线完成之前“预布”decap的策略。虽然预布的decap占据一定的空间,会给单元布局带来影响,但由于decap只用到一层金属,并不影响后续的高层金属布线,同时decap的插入使其附近的单元布局不至于过度紧密,从而可以为布线预留足够的空间。

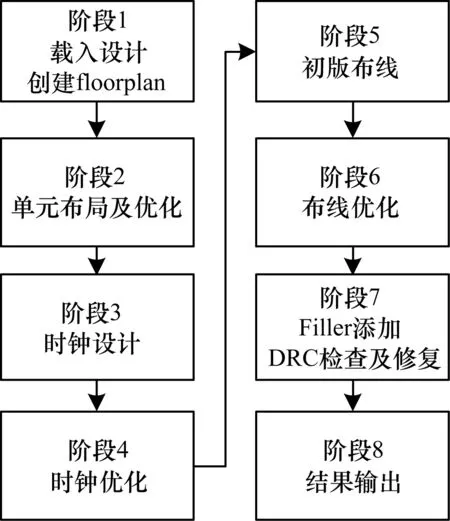

图2所示为芯片设计中的物理实现流程,即综合流程。在第1阶段生成floorplan和powerplan后,有规律地均匀添加少量的decap,即预布decap。预布的decap不宜过多,以免影响到后续的布局和布线。选取decap时,通常选用驱动能力强、等效电容(ESC)大、等效电阻(ESR)小的decap用于预布。如图3所示,预布decap需均匀且有规律。

图2 芯片物理设计流程

进入综合流程中的布局布线阶段后,如果整体设计的利用率较高,或者在某个区域集中分布着关键的时序网点,导致预布的decap影响到了时序,可以适当移除该位置的decap。布线优化完成后,进行空单元Filler插入和decap后补流程。后补流程将多种驱动能力的decap添加到模块的剩余空间中,按照面积由大到小的顺序依次添加,尽可能地铺满空闲区域。在通常情况下,后补的decap占模块总面积的10%~30%。

2.3 list-decap策略

如第2.2节所述,通过“预布+后补”的decap插入策略,可以在保证一定均匀性的基础上,尽可能多地插入decap。但同时,在逻辑密集区域或者某些大电流大翻转区域,可能出现由于没有剩余空间导致无法插入decap的情况。

图4所示为某触发器密集区的decap插入情况,其中,深色为触发器单元,白色为插入的decap单元。由图4可以看出,频繁翻转的触发器紧密地排布在一起,导致decap只在较远的空闲处有零散的插入,而这些较远的距离将大幅降低decap的实际使用效果。

图4 某触发器密集区decap插入情况

为解决上述问题,本文引入list-decap策略,即预先设定一个敏感单元列表,列表中包含大电流大翻转的单元(如正边沿非扫描触发器,大于18倍驱动倍数的单元等)。在插入后补decap之前,先在这些列表中指定单元的两侧插入指定的decap,确保这些敏感单元附近一定有decap单元分布。

如图5所示,增加了list-decap流程后,逻辑密集区的大驱动单元附近均匀地分布着decap单元。

图5 list-decap插入效果示意图

综上,根据decap插入的不同时机,可以将decap插入策略总结为以下3种:

1)pre-decap,即预布decap策略,在布局布线之前均匀预布指定的decap单元,以保证分布的均匀性。

2)list-decap,设置一个敏感单元列表,对列表中指定的逻辑密集区域,在其大电流大翻转单元的两侧插入decap单元。

3)post-decap,即后补decap策略,在布线优化完成后按照面积由大到小的顺序依次插入decap单元,将剩余的区域尽可能地填满。

pre-decap、list-decap、post-decap三种策略相互独立,在模块的设计中可以根据需要选择一种或多种策略。其中,pre+list+post的组合方案是decap插入中数量最多且最均匀的策略。在单一的策略中,post-decap策略能填满模块的所有空闲区域,因此,其插入的decap数量最多。本文将针对这3种decap插入策略的不同组合方式展开对照实验,以探究不同策略的效果并重点研究预布decap的降噪特性。

3 实验设置

3.1 实验环境

本次实验使用Synopsys公司的Design Compiler和IC Compiler工具进行芯片模块的逻辑综合和物理设计。采用TCL脚本辅助实现decap的3种插入策略。物理设计完成后,使用Apache公司的RedHawk工具评估芯片的功耗、瞬态电压降等情况。

3.2 实验方案

本次实验分为如下3个方案:

1)针对电路模块M,在SS、TT、FF三种工艺角下分别尝试3种decap插入策略的不同组合方式,比较最终的功耗及瞬态电压降情况。模块M的基本信息和仿真参数如表2所示。

表2 模块M基本信息及仿真参数

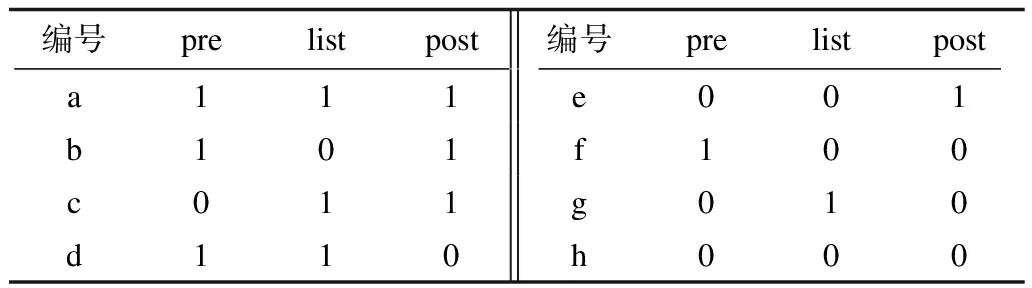

表3列出了3种插入策略8种不同的组合方案,其中,“0”表示未采用该策略,“1”表示采用了该策略,如“a(111)”表示采用pre+list+post三种策略的组合方案,“h(000)”表示未采用任何decap插入策略的方案。本次实验中,在进行decap预布时,预布的decap面积占模块总面积的2%。

表3 3种decap插入策略的不同组合方案

2)针对电路模块M,在综合中预布不同比例的decap,比较不同比例的decap对最大电压降的抑制作用。

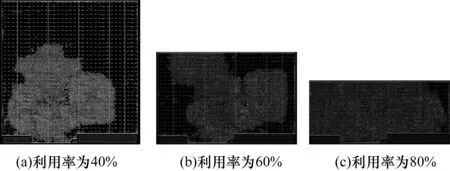

3)针对电路模块M,在利用率分别为40%、60%、80%的情况下进行decap的插入,比较不同利用率下decap的插入效果。

3.3 性能评估方法

在模块综合完成后,使用RedHawk工具对模块进行功耗分析,比较不同综合条件下模块的功耗、最大瞬态电压降等情况。由于decap主要用来抑制高频噪声,对静态电压降的抑制效果并不明显,因此可用RedHawk动态分析结果中的瞬态电压降以评估decap的降噪效果。模块的最大瞬态电压降越小,说明decap对电源噪声的抑制效果越好。

4 实验结果与分析

4.1 不同decap组合方案对电源噪声的影响

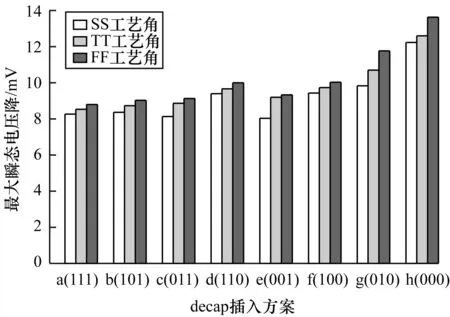

图6对比了SS、TT、FF工艺角下8种decap组合方案的最大瞬态电压降情况。从图6可以看出,与无decap插入的方案,即h(000)相比,其他decap插入方案都能够改善模块的平均电压降。其中,采用3种插入策略,即a(111)的插入方式能够取得最均匀完善的效果,因此,该方案降噪性能最好。当采用单一插入策略时,由于post策略插入的decap数量远远超出pre和list策略(以pre+list+post的情形为例,pre-decap占decap总量的14.3%,list-decap占11.83%,而post-decap占73.87%),因此,post策略的效果相对最好,甚至比采用pre+list时降噪效果还明显。当仅采用2种策略时,pre+post的效果相对最好。

图6 不同decap策略组合下模块最大瞬态电压降对比

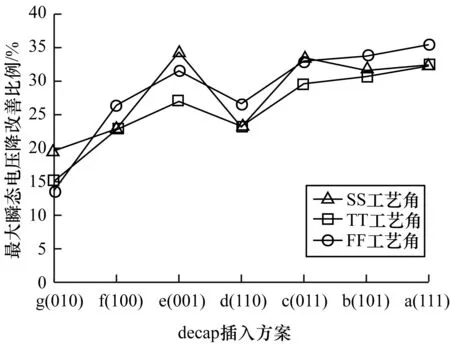

图7对比了SS、TT、FF工艺角下,不同decap插入方法相对未插入decap,即h(000)时最大电压降改善比例。由图7可以看出,在FF工艺角下,decap的插入对电源噪声的整体改善效果最好。原因是FF工艺角下工作频率高,而片上decap用于抑制高频噪声,因此,在FF工艺角下decap能更好地发挥作用。

图7 不同工艺角下最大瞬态电压降的优化比例

4.2 预布流程增加后的性能改善

图8显示了有无pre-decap情况下的降噪性能对比结果。图8(a)、图8(b)分别列出不同组合方案下decap插入总量和最大瞬态电压降情况。由图8可以看出,在所有组合方案中,增加了pre-decap策略后,最大瞬态电压降都有所降低。其中,a(111)的pre+list+post方式与c(011)的list+post方式相比,decap的插入总量仅增加了1%,却使最大瞬态电压降降低了7.2%。

图8 有无pre-decap情况下降噪性能对比

4.3 预布decap比例对结果的影响

在pre+list+post组合方案下,由于后补decap是在模块的空闲区域见缝插针地插入,几乎会填满所有剩余空间,因此无论预布decap的比例有多大,最终pre+list+post所插入的decap总量都不会有太大变化。

在插入decap总量几乎不变的情况下,本文尝试调节预布decap的比例,观察decap预布比例对电源噪声抑制效果的影响。图9显示了预布decap面积占模块总面积的比例不同时最大瞬态电压降的变化情况。实验中,decap的插入采用pre+list+post的组合方案。

图9 最大瞬态电压降与decap预布比例的关系

由图9可以看出,预布decap的比例较低时,降噪性能随预布比例的变化有所波动,预布比例在5%左右具有最优的降噪效果。当预布比例增大到10%以上,降噪性能逐渐饱和。原因是过多的decap会影响到单元的布局和时序收敛,给布线带来困难,尤其会影响关键的时序网点。影响时序的decap会被移除,最终并不能实际插入,因此,实际所能预布的decap比例是有限的。在预布时设置太大比例不仅不能改进降噪性能,反而会增加运行时间。

图10所示为在不同的模块利用率下最大瞬态电压降随decap预布比例的变化趋势。图11所示为模块在不同利用率下的单元布局和pre-decap插入情况。由图11(a)可以看出,当模块的利用率较低时,decap大量分布在周围的非功能区域,因此,其能够起到的降噪作用非常有限,几乎无法改善模块的最大瞬态电压降。但由于模块利用率低,有充足的布局布线空间,因此模块的最大瞬态电压降也较低。当利用率提高到60%以上,布局布线的空间被压缩,模块的最大瞬态电压降有所升高,但此时decap能够有效地分布于功能单元附近,从而可以较好地发挥作用,decap的降噪效果即显现出来。由图11(b)、图11(c)可以看出,模块利用率在60%和80%时,最大瞬态电压降随decap预布比例的变化具有相似的趋势,预布比例在4%~6%时,模块具有最低的瞬态电压降。

图10 不同利用率下最大瞬态电压降与decap预布比例关系

图11 不同利用率下单元布局和pre-decap插入情况

5 结束语

本文提出一种预布decap并在大翻转单元两侧插入decap的方法。实验结果表明,在decap后补策略的基础上引入decap预布流程后,能够以较小的decap插入量取得较大的瞬态电压降减小量,且芯片模块的峰值和均值电流都得到了较好的抑制,当预布decap占模块总面积的4%~6%时,可以得到最佳的降噪效果。今后将增大电路模块的规模并进行实验,根据实验结果对本文方法作进一步优化,并将其应用到工程实践中。