多ADC并行实时采样方法研究

宋问远

(中国电子科技大学自动化工程学院仪器科学与技术系,四川成都, 611731)

0 引言

通常来讲,模拟波形的数字测量涉及最重要的环节之一就是对波形的采样,其效果的好坏直接影响后续的波形重构过程和最终波形显示。而对于波形采样,核心环节就是模拟信号到数字量的转换,因此,如何良好设计模-数转换电路、实现高速准确采样在波形的数字测量技术中至关重要。

实时采样是在触发信号到来后的一个周期内,连续进行采样,一次捕获完这个周期内信号全部波形数据的一种采样方式。传统的宽带数字示波器常利用并行比较式ADC或并串比较式ADC组成高速的模-数转换器来完成非实时的采样,其电路设计复杂,速度慢,量化误差大,且不能实时跟踪波形。本文探讨如何采用高速ADC芯片,分别通过延迟信号采样和并行时间交替采样两种方法完成波形的实时采样及显示,并借助Multisim电路仿真软件搭建电路并仿真采样结果。

1 多ADC并行采样原理与实现手段

1.1 多ADC并行采样原理

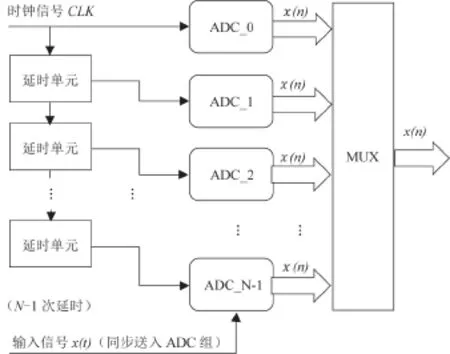

将N片ADC并列在一起,用同一时钟频率0f驱动其工作,但每片ADC开始采样的时间与前一片保持固定的时间差0/T N,或者信号被每片ADC采样的位置保持固定的相位差,从而使信号输进ADC组后在一个时钟周期内被完全分相成N部分,进而使得采样率从单片ADC的0f提升至N片ADC的等效采样率0Nf。

基于这一设想,有两种方法可以达到ADC间隔性工作的目的,分别是延迟输入信号到达每片ADC的时间和产生时钟间隔延迟每片ADC开始工作的时间,即信号分相和时钟分相。

1.2 基于延迟线的延时采样

在由N片ADC组成的采样系统中,先将待采信号直接送入采样通道,让其依次通过(N-1)个精准延时单元,每个单元延时量为0/T N,即信号被均等分相成N部分。再将频率为0f的时钟信号同时送给N片ADC驱动其同步开始工作,对被分相后的输入信号进行采样。这样,信号到达每个ADC的时刻都不相同,整个采样系统在一个时钟周期内可以等间隔地采到N个点,等效采样率为N0f。

图1 基于延迟线的多ADC并行采样系统

1.3 并行时间交替采样

与延时采样原理不同的是,交替采样将待采信号同时送入ADC组,而让时钟信号通过固定间隔0/T N后依次使能各ADC,从而使每片ADC在信号的不同时刻对信号进行采样。显然,根据运动的相对性,交替采样和延时采样效果相同,都可以将单片ADC的采样率0f通过并行提升至N0f。

图2 多ADC并行时间交替采样系统

2 Multisim电路仿真设计及采样结果

2.1 电路设计

2.1.1 延时采样电路设计

图3 基于Multisim的信号延时采样电路图

图4 基于Multisim的并行时间交替采样

鉴于电脑软件在空间与资源上的局限性,本仿真选择采用4片通用8位ADC组成采样系统,且延时单元为理想延时单元。在实际的工程运用中,ADC的选型极为重要,应从分辨率、转换速度、精度等多方面进行考虑。总的来说,ADC可分为直接比较型和间接比较型两大类。直接比较型,就是将输入的采样模拟量直接与作为标准的基准电压相比较,得到可按数字编码的离散量或直接得到数字量;而对于间接比较型,输入的采样模拟量不是直接与基准电压比较,而是将两者都变成中间物理量再进行比较,然后将比较得到的时间(t)或频率(f)进行数字编码。[1]

在本设计中,ADC的直流供电电压为5V,被测信号为频率12Hz、峰峰值10V的正弦波,时钟信号频率为640kHz。由于一个时钟周期内要有4片ADC依次采样,一个延时单元延时量应为时钟周期的1/4,约0.39μs。

2.1.2 交替采样电路设计

电路元件参数与延时采样一致,不同的是交替采样中被延迟的是时钟信号。在实际工程运用中,这个时间间隔不一定用延迟时钟的方法来实现,一般可以通过程序来控制时钟信号进入各ADC的时间。

2.2 采样信息的处理与波形显示

在数字存储示波器(Digital Storage Oscilloscope,DSO)中,经采样系统模-数转换后的波形数字量在触发信号的配合下被存入存储器。当存储器存储满了后,系统则停止采集,然后从存储器中读出存储的采样数据,处理器对读出的数据进行一系列运算和处理后,最后将处理好的数据转换为与显示屏对应的波形图像,送到显示器进行显示。[2]

基于并行时间间隔交替采样的方法,在Multisim中处理并显示波形的原理为:在每个时钟周期内,4片ADC共采集到4个不同步的波形数据,将其按采样先后顺序从高位到低位依次送入多路复用器,再经数-模转换送入示波器进行显示,显示的顺序应该既是实时采样的顺序,也是信号的时序。图5、图6分别为原始信号和采样处理后的信号波形,可以看出,在Multisim本身无法进一步对波形进行抽样、插值等实际DSO中必不可少的波形重构环节的情况下,单纯的采样信号就已具备了良好的显示效果。

3 结语

本文通过对多ADC并行采样原理的研究,探讨了两种在波形的数字测量中实现高速率实时采样的方法——基于延迟线的延时采样和并行时间交替采样,并借助电路仿真软件Multisim分别搭建了相应电路,完成了从信号采样到波形显示的过程,验证了利用多ADC并行采样的模式实现实时采样的可行性。该模式可以克服传统高速采集系统成本高、速度慢、对ADC芯片要求过高等缺陷,而基于该模式的实时采样也更加容易跟踪一些复杂任意的波形,丰富了波形数字测量技术可测的信号类型,提高了测量的整体质量。

图5 原始信号波形

图6 高速多ADC并行采样信号波形