浮栅器件和普通NMOS器件总剂量效应对比研究

董 艺,沈鸣杰,刘 岐

(上海复旦微电子集团股份有限公司,上海 200433)

0 引言

卫星集成电路在空间环境中会受到电离辐射的影响,产生总剂量效应[1]。总剂量效应会在集成电路的二氧化硅层产生大量的电子−空穴对并导致界面态效应。集成电路中的NMOS器件对这些效应比较敏感,在总剂量效应下,NMOS器件会出现漏电流增加以及阈值电压变化,严重影响器件特性,并使得集成电路的性能和功能出现异常,进而导致卫星系统无法正常工作[2]。

普通集成电路中的器件以PMOS和NMOS器件为主,但对于Flash[3-5]产品来说,其主要组成单元是存放数据的浮栅器件,围绕浮栅器件的电路称为外围电路。外围电路主要包括用于算法控制的数字电路和用于高压擦写的高压电路,前者主要由低压MOS器件组成,后者主要由高压MOS器件组成。以上不同类型的器件在电离辐射条件下会产生不同的特性变化,特别是Flash产品所特有的浮栅器件的总剂量效应,需要抗辐射Flash产品的设计者予以特别关注。

本文对Flash产品中的多种器件开展总剂量辐照试验,搜集数据,以展示不同类型器件对总剂量辐照所产生的不同效应,特别是浮栅器件在总剂量辐照下产生的独特效应。

1 低压NMOS器件总剂量效应

选取某应用NOR Flash工艺的低压NMOS器件作为试验对象。该NMOS器件栅氧化层厚度为7 nm,测试芯片中采用100个NMOS器件进行并联,每个 NMOS 器件的W/L=4 μm/0.39 μm。卫星长期稳定在轨工作,至少要能耐受31 krad(Si)的总剂量,再考虑到设计余量,会要求宇航用器件的抗总剂量辐射能力至少达到100 krad(Si)[6]。因此本试验累计总剂量做到100 krad(Si),并再追加50 krad(Si)到累计150 krad(Si)。试验中采用的剂量率为50 rad/s。总剂量辐照后进行100 ℃的退火,退火时间依次为24、72、168 h。试验采用加电辐照,对器件的栅端施加3.6 V电压,辐照后分别对低压NMOS器件的漏电流和阈值电压进行测量。以上试验方法依据了相关航天标准[7]。同时高/低压NMOS器件和浮栅MOS器件在工艺上同属于NMOS结构类型器件,因此试验可采用同样的方法进行。整个试验过程为:总剂量辐照在中国科学院上海应用物理研究所进行,辐照时器件放置在自制偏置板上以保证偏置;辐照完成后回上海复旦微电子集团股份有限公司的测试间进行器件性能测试。主要试验设备包括钴60射线源、PK2存储器专用测试机和稳压电源E3631A。试验测试内容包括静态总剂量试验下被测NMOS器件的主要表征参数,如漏端电流、MOS器件阈值电压。

低压NMOS器件漏电流在总剂量辐照前后的试验结果如表1所示。漏电流测量时NMOS器件的栅端接0 V,漏端接3.6 V。试验样品中,1#和2#没有采用任何抗总剂量加固设计,3#和4#采用了环栅的抗总剂量版图加固设计。

表1 低压NMOS器件漏电流的总剂量效应试验结果Table 1 TID test result of low voltage NMOS leakage current

测试数据中的负值是由于在所测量电流过小接近于0 nA的情况下,PK2机台测试电流会由于精度问题出现不低于-20 nA的负值。从表1试验结果看出,采用环栅加固后的低压NMOS器件在总剂量辐照后漏电流没有任何增加,但不进行加固的器件在总剂量100 krad(Si)和150 krad(Si)下漏电流增加剧烈[8]。该试验中对漏电流上限进行了2.5 μA的限流,因此测试值最大只到2499 nA。未加固的低压NMOS器件经过总剂量辐照后只要经过24 h以内的退火,漏电流即迅速恢复到辐照前的量值。

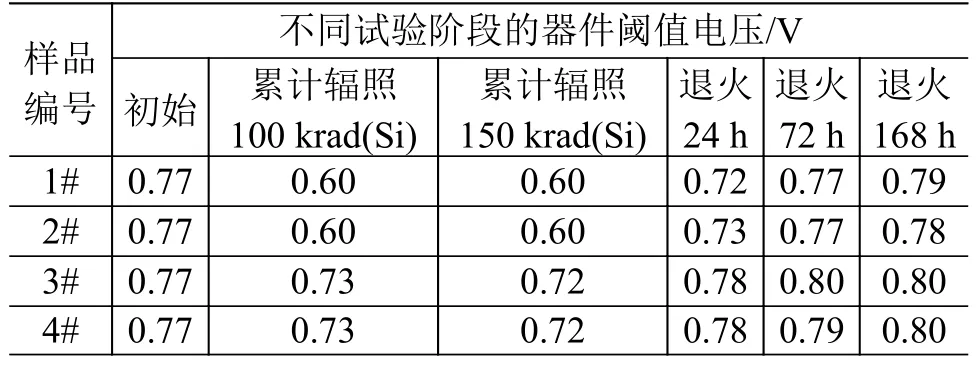

表2 低压NMOS器件阈值电压的总剂量效应试验结果Table 2 TID test result of low voltage NMOS threshold voltage

从表2试验结果看出,采用环栅加固后的低压NMOS器件在总剂量辐照后,阈值电压几乎无变化,不进行加固的器件在总剂量100 krad(Si)辐照后在漏电流的影响下其等效阈值电压有明显下降,继续追加辐照剂量到150 krad(Si)后其等效阈值有轻微下降。未加固的低压NMOS器件经过总剂量辐照后只要经过24 h以内的退火,其阈值电压即迅速恢复,恢复的机理是由于总剂量辐照过程中产生的氧化物陷阱电荷在退火过程中消失[9]。同时试验数据也证明了环栅设计对低压MOS器件总剂量效应的抑制作用,为相关产品的抗总剂量设计提供了参考。

2 高压NMOS器件总剂量效应

选取某NOR Flash工艺的高压NMOS器件作为试验对象。该NMOS器件栅氧化层厚度为16 nm,测试芯片中采用100个NMOS进行并联,每个NMOS 的W/L=4 μm/0.62 μm。整个总剂量试验方法和第1章低压NMOS器件的相同。

高压NMOS器件漏电流在总剂量辐照前后的试验结果如表3所示。漏电流测量时NMOS器件的栅端接0 V,漏端接9 V。试验样品中,1#和2#没有采用任何抗总剂量加固设计,3#和4#采用了环栅的抗总剂量版图加固设计。

表3 高压NMOS器件漏电流的总剂量效应试验结果Table 3 TID test result of high voltage NMOS leakage current

从表3试验结果看出,采用环栅加固后的高压NMOS器件在总剂量辐照后漏电流没有任何增加,但不进行加固的器件在总剂量100 krad(Si)和150 krad(Si)的辐照下漏电流增加剧烈[8]。该试验中对漏电流上限进行了2.5 μA的限流,因此测试值最大只到2499 nA。未加固的高压NMOS器件经过总剂量辐照后进行24 h以内的退火,漏电流无法恢复到初始值,在退火进行到168 h后漏电流能恢复到初始值。

高压NMOS器件阈值电压在总剂量辐照前后的试验结果如表4所示。阈值测量方法同低压NMOS器件。

表4 高压NMOS器件阈值电压的总剂量效应试验结果Table 4 TID test result of high voltage NMOS threshold voltage

从表4试验结果看出,采用环栅加固后的高压NMOS器件阈值电压在总剂量辐照后有轻微下降,随着退火的进行,器件阈值电压会恢复且最终会高于初始值。不进行加固的器件在总剂量100krad(Si)辐照后由于漏电流的影响其等效阈值电压有明显的降低,追加辐照总剂量到150 krad(Si)后其等效阈值电压不变。未加固的高压NMOS器件随着退火的进行,其阈值电压会恢复且最终会高于初始值,恢复的机理是由于总剂量辐照过程中产生的氧化物陷阱电荷在退火过程中消失[9]。但该器件退火恢复所需要的时间比低压NMOS器件的要长。同时试验数据也证明了环栅设计对高压MOS器件总剂量效应的抑制作用,为相关产品的抗总剂量设计提供了参考。

3 浮栅器件总剂量效应

选取某NOR Flash工艺的浮栅器件作为试验对象。浮栅器件结构基于NMOS器件,在单栅的NMOS器件结构中加入了一个被隔离的浮栅作为电荷存储介质。浮栅下面的隧道氧化层是编程和擦除时电子出入浮栅的通路。浮栅器件结构如图1所示。试验所用的浮栅隧道氧化层厚度为10 nm。整个总剂量试验方法和前文的低压NMOS器件相同。

图1 浮栅器件结构图Fig. 1 Structure of the floating gate device

进行试验的浮栅器件编号为5#和6#,均没有进行任何抗总剂量加固设计。浮栅器件电流在总剂量辐照前后的测试结果如表5所示。测试中对浮栅器件的栅端加2.8 V电压,漏端加0.1 V电压以测量浮栅器件的电流。

334例住院患者地高辛血药浓度监测结果及影响因素分析…………………………………………………… 钱懿轶等(13):1816

表5 总剂量辐照前后浮栅器件的电流值Table 5 TID test result of floating gate device current

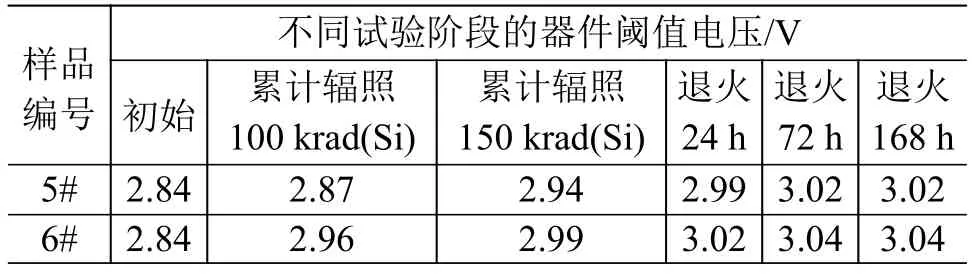

表5中电流的变化反映了浮栅器件阈值随着总剂量辐照试验进行而产生的变化趋势。为了更直观地看出浮栅器件阈值电压的变化,采用扫描浮栅器件栅端电压的方式来得到浮栅器件的阈值电压,阈值判断点为漏端施加0.1 V电压时电流达到1 μA(浮栅单元尺寸小且是单一器件,因此判断点电流小于第1章低压NMOS器件的)。由此得到的浮栅器件阈值电压在总剂量辐照前后的测试结果如表6所示。

表6 总剂量辐照前后浮栅器件的阈值电压Table 6 TID test result of floating gate device threshold voltage

对于该工艺的NOR Flash浮栅器件,器件初始阈值2.84 V是处于低阈值的擦除状态,即处于“1”状态;相对的,器件阈值如果处于高阈值的编程状态则被定义为“0”状态。通过试验发现,处于擦除态的浮栅器件的总剂量效应明显不同于普通的NMOS器件。普通NMOS器件的阈值电压会随着辐照总剂量的增加而降低,但浮栅器件的阈值电压会随着辐照总剂量的增加而持续升高,阈值变化幅度和辐照总剂量成正比;总剂量试验后的退火无法使得器件阈值向着初始阈值方向降低,反而随着退火的进行持续升高(在退火过程中没有施加任何擦写电压)。高、低压NMOS器件和浮栅器件的阈值电压在总剂量试验中的变化趋势对比见图2。

图2 总剂量辐照中各种器件阈值电压变化对比Fig. 2 Comparison among threshold voltage of floating gate device and MOS devices after TID irradiation

4 对比分析

浮栅器件在总剂量辐照后产生的效应完全不同于普通NMOS器件。这主要是由于两方面的原因造成的:

一方面,总剂量效应在二氧化硅中产生大量电子−空穴对,电子会被快速扫出氧化层。本试验结果不能确定全部电子都定向进入浮栅,但从浮栅器件阈值电压持续升高的现象能确认,其中一部分电子会注入浮栅。对于浮栅器件来说,将电子进入浮栅从而提高浮栅器件阈值电压称为编程效应,而将电子离开浮栅从而降低浮栅阈值电压称为擦除效应,因此以上效应相当于对浮栅器件产生了编程并提高了浮栅器件的阈值电压。随着总剂量的增加,电子−空穴对不停地产生,电子持续注入浮栅。总剂量试验停止后,由于浮栅保存电子的特性,所以浮栅内的电子数量永远保持在总剂量试验停止的那一刻,后续即使进行退火,也不可能将浮栅内的电子赶出浮栅,因而退火后浮栅器件阈值电压继续升高。总剂量试验中会采用过辐照50%加退火进行试验[9];但对于浮栅器件来说,过辐照50%产生的影响是完全无法通过退火恢复的,因此过辐照50%加退火的总剂量试验对于浮栅器件来说是过严的试验。

另一方面,浮栅器件的浮栅下存在隧道氧化层,会在总剂量下产生和普通NMOS器件相同的效应,即NMOS器件的氧化层中由于电子−空穴对的产生出现氧化物陷阱电荷和界面态陷阱电荷,会造成浮栅器件的阈值电压降低;但对于起始阈值为2.84 V的浮栅器件来说,电子注入浮栅造成的阈值电压升高幅度大于陷阱电荷造成的阈值电压降低幅度,因此表现出浮栅器件整体阈值升高。和普通NMOS器件相类似,陷阱电荷引起阈值电压降低的效应能通过高温退火恢复。正是由于这个特性,造成了经历150 krad(Si)总剂量试验后的浮栅器件在退火过程中其阈值电压表现为继续持续上升。

由于以上两方面的原因,在对浮栅器件进行总剂量并追加退火的试验过程中,器件表现出随着总剂量的增加以及退火的进行,其阈值电压一直持续上升且不会出现向初始态恢复降低的现象。相对而言,NMOS器件在同样的试验条件下则表现出随着总剂量的增加其阈值电压降低;但随着退火进行,阈值电压会恢复升高。

对该NOR Flash工艺上的实际产品进行普通编程操作可以发现,施加2 μs的电编程脉冲可以将2.8 V的浮栅器件阈值电压提高到6 V以上。而经过总剂量150 krad(Si)辐照并追加退火后浮栅器件的阈值电压从2.84 V仅提高到3.04 V,相对于一般的电编程操作,总剂量辐照引起阈值电压提升的幅度小得多。因此在总剂量辐照下,浮栅器件所产生的编程效应是一种弱编程效应。该弱编程效应引起擦除态浮栅器件阈值提高的效应符合相关文献的试验结果[10]。产品设计师可参考该浮栅器件阈值电压变化的幅度,在进行NOR Flash产品的抗总剂量设计时选择合适的浮栅器件阈值窗口以及合适的非挥发配置位结构等。

5 结束语

本文针对NOR Flash工艺中的几类代表性器件进行了总剂量辐照试验,对试验数据进行比对发现,NOR Flash工艺中高压NMOS器件在总剂量试验后通过退火恢复所需的时间比低压NMOS器件的要长,采用环栅加固可以有效抑制高、低压NMOS器件的总剂量效应。而浮栅器件由于其特有的隔离浮栅结构,会在总剂量辐照中被注入电子而产生特有的弱编程效应,并且退火不能使得该效应所产生的影响恢复,即浮栅器件表现出明显不同于其他NMOS器件的总剂量效应。

本文的试验结果可以作为抗辐射Flash器件抗总剂量加固设计的依据。