基于FPGA的扩跳频信号源的设计与实现

牛强军, 孙会超, 张 强

(1.郑州大学,郑州 450001; 2.空军工程大学航空机务士官学校,河南 信阳 464000)

0 引言

为满足部队开展基层级技术状态检查、中继级巡修和基地级应急抢修时对扩跳频电台进行快速检测的需求,需要一种便携、性能可靠、使用方便和集成化的扩跳频信号源,为电台测试提供激励信号,以提高部队快速保障能力。传统的战术扩跳频电台信号源大多采用模拟电路合成,这种电路在信号合成、调制和功率控制的每个环节都会引入各种噪声,降低信号源的性能指标。为了解决该问题,国内学者提出了一些方案:文献[1]提出了基于FPGA思想的跳频调制实现方案,系统结构较传统结构得到简化,性能得到增强[1],但系统使用DDS+PLL结构,使得系统体积不利于设备小型化和规模化;文献[2]完成了跳频系统体系架构,结构化设计[2],但同样存在设备体积大的问题;文献[3]在传统的跳频通信基础上提出了变速跳频机制,在抗干扰性能方面得到提升[3],但跳速偏低,缺乏硬件实现验证。针对以上问题,结合电台测试的要求,提出了一种基于FPGA+AD9915的扩跳频信号源实现方案。

1 系统方案设计及硬件介绍

1.1 系统方案设计

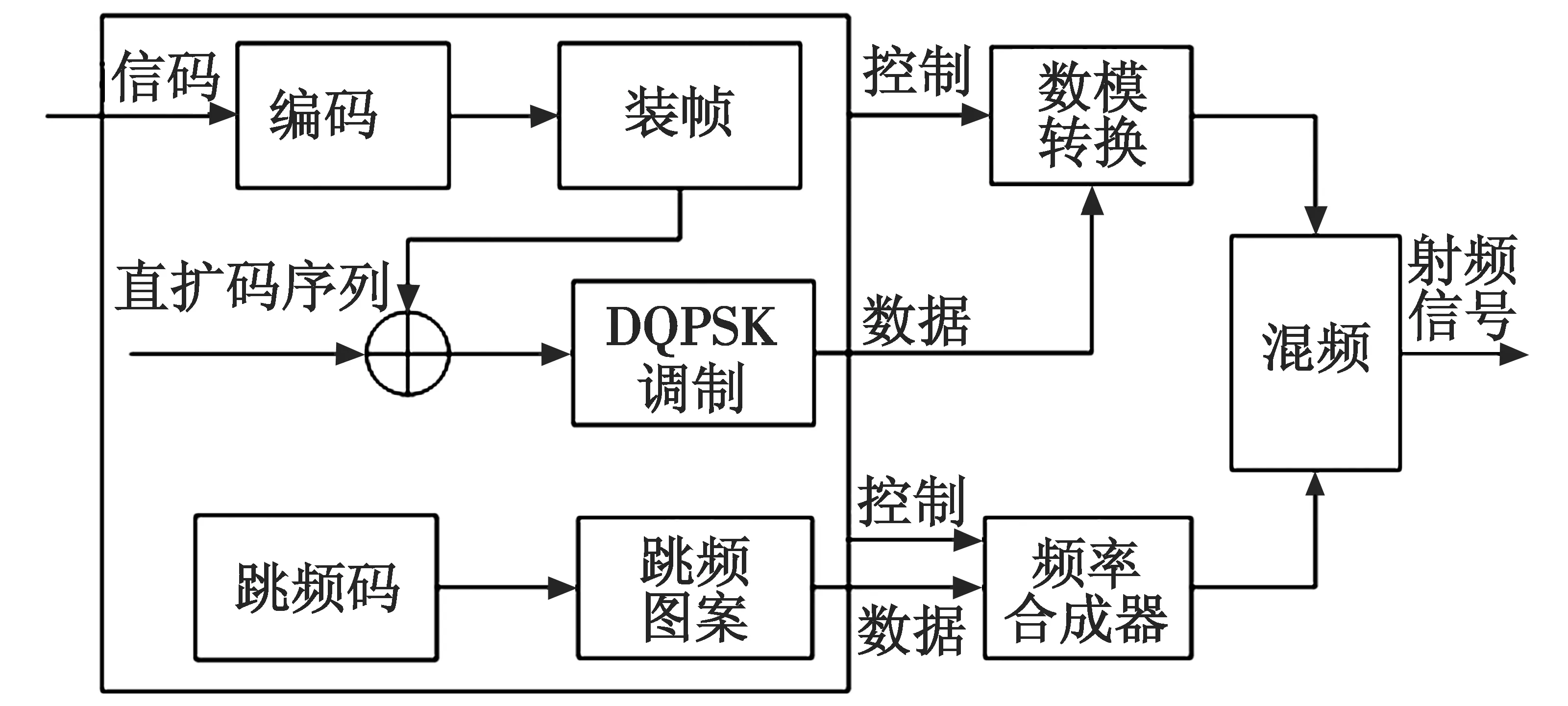

根据信号源需求,结合扩跳频原理,构建系统总设计方案如图1所示。

图1 扩跳频系统方案图Fig.1 Diagram of the DS/FH system scheme

FPGA从主控单元接收含有数据信息的二进制信码,芯片内部进行卷积编码,编码后的信息输入到缓存器中,达到指定长度后与当前跳频同步信息组帧完成一个完整的跳频帧,再将这些数据进行扩频调制、串并转换后完成π/4-DQPSK调制,控制数模转换芯片实现中频调制;同时,FPGA通过跳频码实现对频率合成芯片的控制,产生跳频载波;将两路模拟信号混频实现扩跳频信号[4]的产生。

依据方案将系统硬件分为基带数据信息处理模块、数模转换模块、频率合成模块、混频模块和电源模块共5个模块,本文主要介绍前3个模块的设计。

1.2 基带数据信息处理模块

方案选用的是美国Altera公司的EP4CE6E22C8高性能芯片,芯片内部集成了24 624个逻辑单元,内嵌66个乘法器,超过600 kbd RAM和内嵌了4个锁相环电路,拥有144个用户I/O口,满足数字基带信号处理的要求。

该模块在FPGA中主要完成系统时钟的分频倍频、基带数字信息处理、扩频处理、DQPSK调制、跳频图案的生成、AD9915控制和数模芯片的控制。系统运行后,FPGA首先进行初始化操作,随后将接收到的信息数据进行基带信息处理[5]完成DQPSK调制,将信息数据调制到中频载波上,通过12位数据总线完成对数模转换芯片的控制,同时FPGA根据跳频图案生成控制指令,通过32位并行数据总线对DDS芯片进行控制。

1.3 数模转换模块

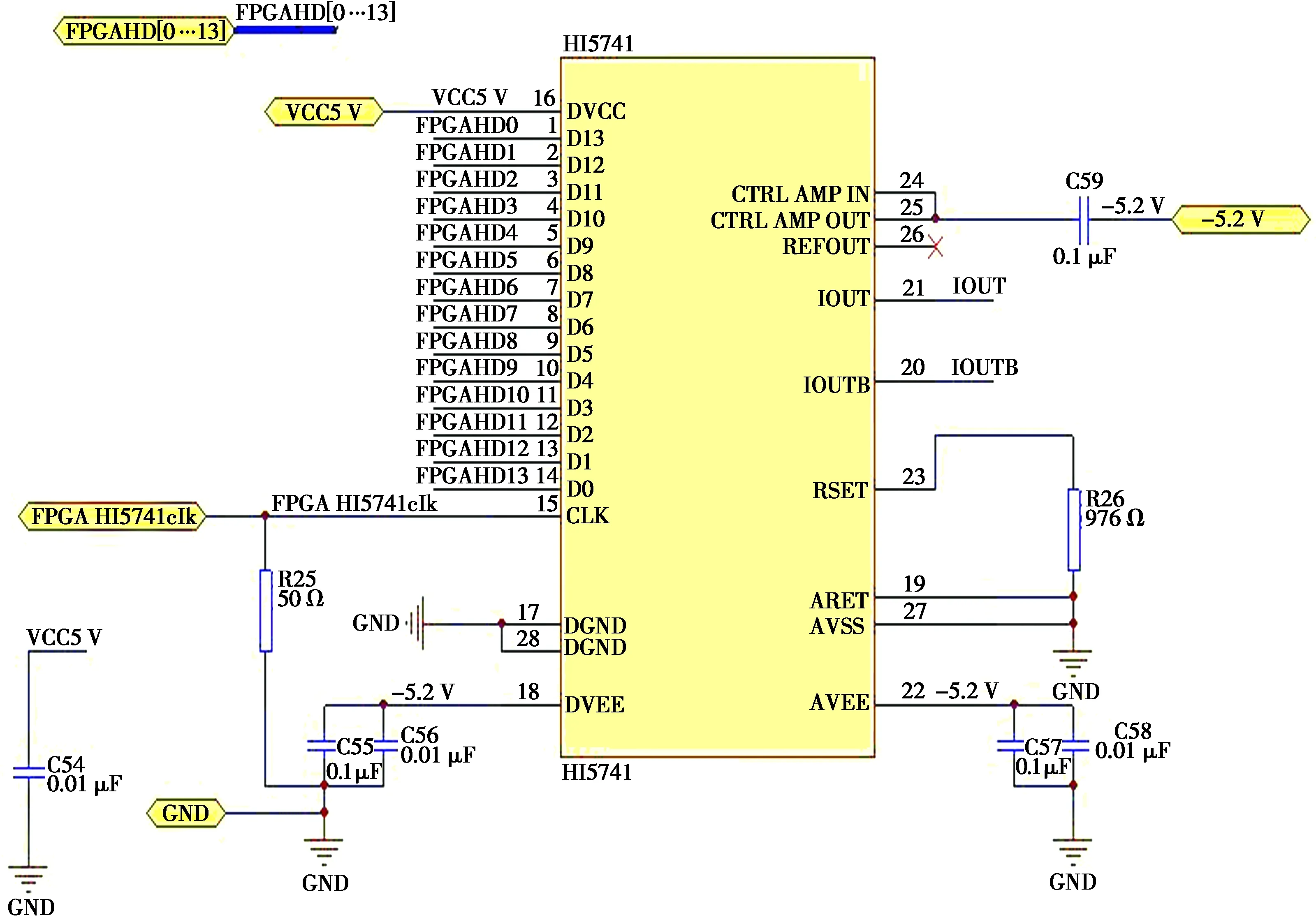

方案选用美国Harris公司的HI5741芯片,具有14位D/A数据转换接口,+5 V和-5.2 V电源供能,最高转换速率可达100 MHz,具有优良的频域性能。

FPGA完成DQPSK调制,最后加法器输出的是16位数字信号,为了完成对HI5741的控制,就需要进行截断,选择输出的高14位作为控制信号,因此FPGA与HI5741之间具有14位数据总线。HI5741的使用方法和接口时序比较简单。HI5741芯片受时钟控制,只要在时钟的上升沿将14位数字数据输入到输入锁存器中,芯片内的模拟数据就会立即更新。电路原理如图2所示。

图2 HI5741连接图Fig.2 Connection of HI5741

1.4 频率合成模块

频率合成选用直接数字合成法(DDS),这种方法简单可靠、控制方便,高性能芯片具有很短的频率转换时间和很高的频率分辨率,频率稳定度满足设计要求,很适合跳频信号源的设计[6]。DDS的原理如图3所示,包含相位累加器、波形存储器、数模转换器3个部分。

为得到输出为理想单频信号U(t)=Asin(2πf0t)的信号,用采样频率为fc(Tc=1/fc)的时钟信号进行采样,则相位增量Δθ1=2πf0Tc。将一个理想正弦信号等分2N份,量化为16进制数存放在波形存储器中,则相位增量为Δθ2=2π/2N。

如果两个相位增量相等,得到输出信号频率为f0=fc/2N,此时输出的频率最小,作为DDS芯片的频率分辨率。如果控制两个相位增量的比例k=Δθ1/Δθ2(k为频率控制字),就实现了对输出频率的控制,此时的输出频率f0为

(1)

这里可以看成输出频率是频率分辨率的k倍。

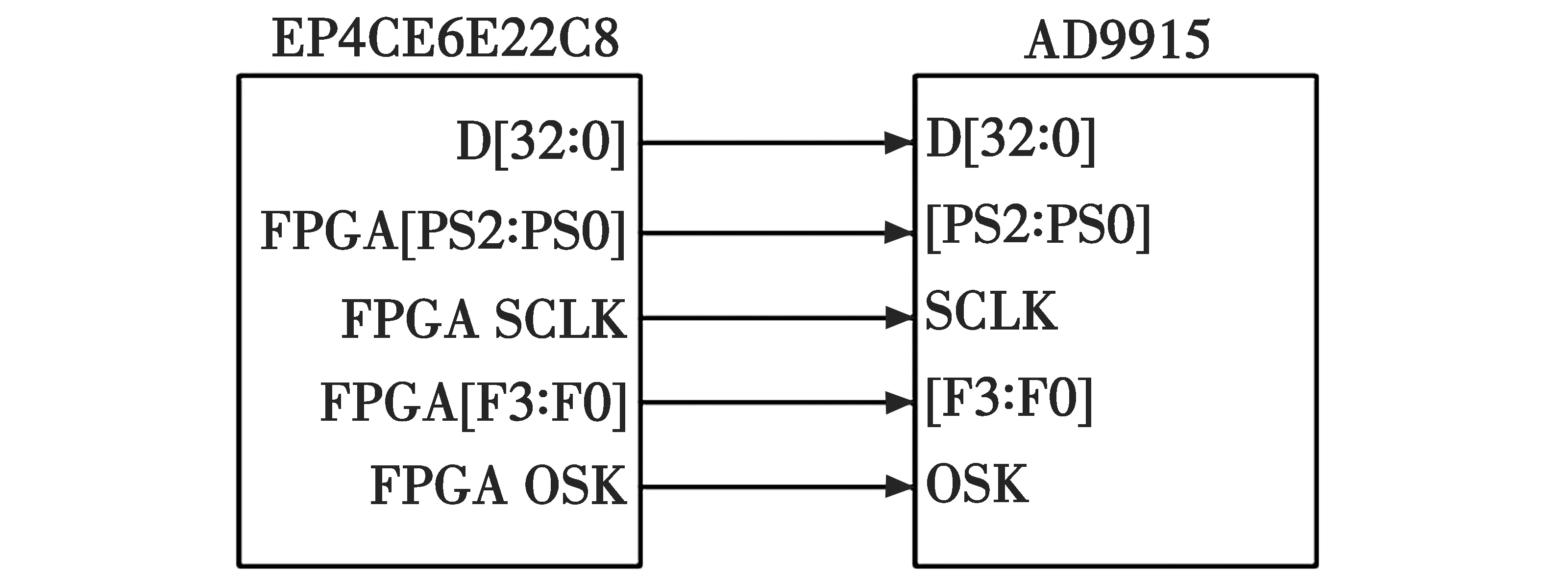

DDS芯片选用的是美国ADI公司的AD9915高性能芯片,2.5 GHz时钟速度,内部集成12位DAC,具有32位并行数据接口,频率转换时间达到纳秒级。FPGA与AD9915的硬件连接方法如图4所示。

图4 FPGA与AD9915的硬件连接图

2 软件设计

依据软件无线电的思想,通过软件控制硬件,只需要改变数据总线上的控制数据,即可控制芯片完成频率跳变,提高跳频速率,简化硬件结构的组成。

基于FPGA的模块化思想,软件编程是遵循先分调,再总调的思想。在Quartus Ⅱ平台采用Verilog语言实现分模块的仿真,部分主要的分模块仿真结果会做具体介绍。仿真结果正确后将分模块移植到一起进行总体仿真,最后将程序下载到PCB板芯片上进行测试。

2.1 π/4-DQPSK调制

π/4-DQPSK调制是一种线性窄带数字调制技术,是在QPSK技术的基础上改进的,在非线性信道中可以获得比QPSK 更高的频谱效率,具有频谱特性好、频谱利用率高等优点[8]。π/4-DQPSK调制相位变化是π/4的整数倍,不会出现因相位突变导致的频谱偏移。

k-1时刻的载波传输信号Sk-1可表示为

Sk-1(t)=cos(ωt-φk-1)

(2)

式中,φk-1为绝对相位。k时刻的绝对相位载波传输信号Sk为

Sk=cos(ωt-(φk-1+Δφ))

(3)

式中,Δφ为相位变化,φk-1+Δφ=φk,将Sk展开得到

Sk=cos(φk-1+Δφ)cosωt+sin(φk-1+Δφ)sinωt=

Ikcosωt+Qksinωt

(4)

式中:

Ik=cos(φk-1+Δφ)=

cosφk-1cos Δφ-sinφk-1sin Δφ=

Ik-1cos Δφ-Qk-1sinΔφ;

(5)

Qk=sin(φk-1+Δφ)=

sinφk-1cos Δφ+cosφk-1sin Δφ=

Qk-1cos Δφ+Ik-1sin Δφ。

(6)

这是π/4-DQPSK调制的数学基础,式(5)、式(6)表明Ik和Qk不仅和输入数据有关,而且与前一时刻Ik-1和Qk-1有关[9]。由式(4)构造如图5所示的DQPSK调制器。

图5 DQPSK调制系统组成框图Fig.5 Block diagram of DQPSK modulation system

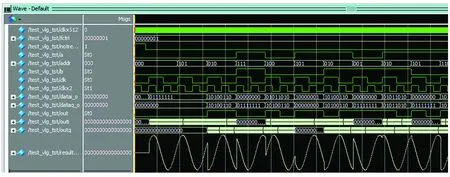

在Quartus软件中编程实现调制的仿真如图6所示。图中可以看出第3个波形的相位为3π/2,第4个波形的相位为3π/4,两个波形之间的相位差为5π/4,此时输入的两路数据为(0,0),与理论输入结果一致,说明仿真结果正确。

图6 π/4-DQPSK调制仿真结果图Fig.6 π/4-DQPSK modulated simulation results

2.2 跳频码

跳频码的设计是一个跳频系统的关键核心,一个跳频码的设计好坏直接关系到这个跳频系统的抗干扰性能。根据跳频图案随机性好、产生电路简单等的抗干扰性能要求,采用对偶频带法和L- G模型,构造出一种宽间隔跳频图案。算法在FPGA中具体实现步骤如下。1) 基于m序列,利用非连续抽头模型,建立区间跳频序列,同时通过对偶频带的关系,建立对应的跳频序列,将跳频频带分成两个对偶的区间频带。2) 根据前一时刻生成跳频码的标志位,选择在对应区间频带内做比较,计算出前一时刻频点和当前时刻频点之间的距离。3) 如果频点间的距离满足要求,选择在同一区间频带内跳变;如果不满足跳变距离的要求,则改跳到对偶频带上,依次延续下去,保证前后两个频率点满足宽间隔要求。

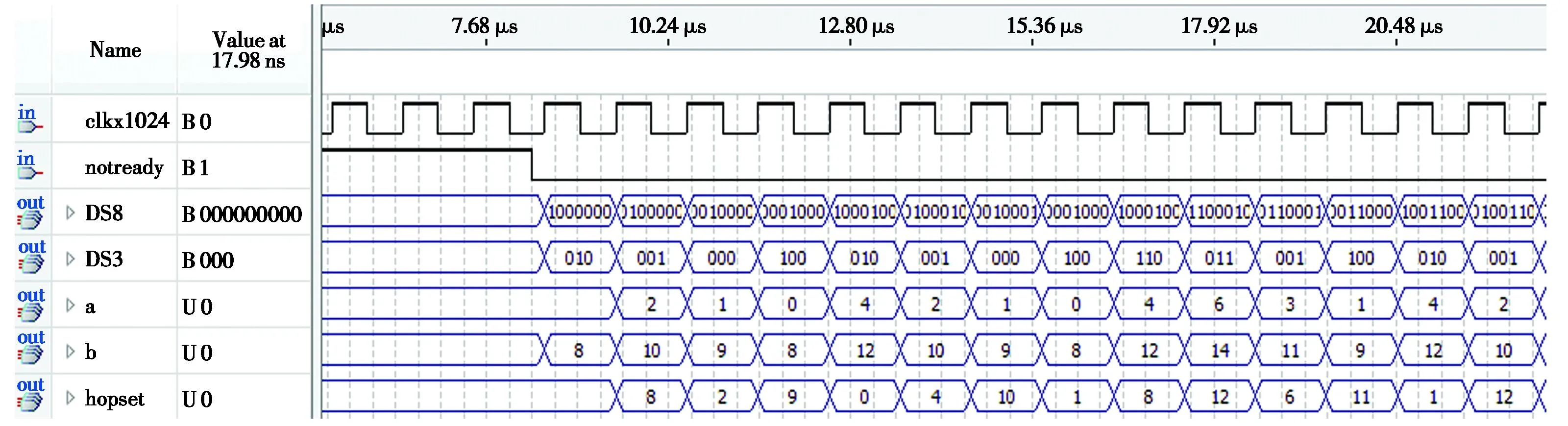

依据以上思路,设计频率数目为q=16、跳频间隔为d=3的宽间隔跳频序列[10]。采用本源多项式为x9+x4+1的m序列设计跳频序列。跳频序列仿真如图7所示。仿真输出的跳频码间隔大于3,满足设计要求,频率在16个跳频点之间跳变,仿真结果达到预期要求。

图7 对偶宽间隔跳频序列仿真图Fig.7 A simulation diagram of frequency hopping sequences for dual width intervals

2.3 跳频控制模块

由于中频调制输出的频率为定值,所以系统频率的跳变主要通过FPGA对AD芯片的控制来完成。在时钟的控制下 ,FPGA更新AD9915的频率控制字来变换频率输出。芯片控制流程如图8所示。

图8 芯片控制流程图Fig.8 Flow chart of chip control

芯片上电后先进行主机复位,使芯片内部寄存器恢复至默认值。根据芯片特点,上电后还需将DAC校准使能位手动置1,然后清零,这会启动内部校准程序,优化DAC时序建立时间。随后进行芯片的基础配置,配置[F3∶F0]引脚,设置芯片的工作模式为Profile调制模式;利用外部引脚[PS2∶PS0]选择指定的寄存器,采用乒乓操作[11]配置寄存器的DDS数值,随后在SYNC_CLK时钟上升沿下使用指定的Profile寄存器中的参数更新数据,完成频率的切换。

3 系统调试

基于软件无线电的优势,只需改变开发平台上的设置数据,就可改变跳扩频系统的m序列、跳频点数、频率间隔等数据,进而控制跳频系统的参数。为了方便系统性能测试,选择在超短波108~118.9 MHz的带宽内测试,使用频谱仪观察输出信号频谱,如图9所示。根据跳频序列生成算法在带宽内分配了16个跳频点,频谱仪显示16个频谱清晰的尖峰,说明信号性能良好。中心频率显示为113 MHz,频率间隔为625 kHz,达到跳频信号源的频率间隔要求。

图9 跳频频谱图Fig.9 Frequency hopping spectrogram

4 结论

针对目前扩跳频信号源携带不便和集成度低等问题,依据扩跳频通信信号的要求,构建了以FPGA和DDS为核心的扩跳频信号源。系统设计采用软件无线电技术和直接数字频率合成技术,具有体积小、重量轻、性价比高和集成度高的特点。实验结果表明,该跳频信号源能够在软件参数可控的条件下,稳定地输出携带数据的全频段跳频信号,系统整体发送数据速率4.8 Kibit/s,跳频速度为1000 hop/s,满足机载电台测试过程中对跳频信号源的性能要求。该信号源除了满足部队外场电台性能测试外,还可推广到航修厂、研究所和部队修理厂等单位,具有较高的推广应用价值。