彩色线阵CCD实验系统研制

朱 正, 张 杨, 孙晶华, 刘 禄, 王德兴

(哈尔滨工程大学 理学院, 黑龙江 哈尔滨 150001)

CCD(charge coupled devices,电荷耦合器件)具有光电转换、信息存储等功能,而且分辨率高、动态范围大、信噪比高,在图像传感、光谱分析、产品分选和非接触测量等领域得到了广泛的应用[1-4]。CCD作为典型的光电器件在光电信息科学与工程专业的专业课中从原理、驱动信号时序到应用都得到的详细的介绍,但是缺乏实验教学的支撑,学生对CCD理解得并不深刻,因此在后续的光电综合实验课程中开设了关于线阵CCD的实验内容,研制了彩色线阵CCD实验教学系统。

CCD光电器件只有在合适的时序驱动下才能输出稳定可靠的信号,因此驱动电路的设计也就成为其应用中的关键问题之一。由于不同厂家生产的 CCD其驱动时序不尽相同,而且同一厂家的不同型号的 CCD 其驱动时序也不完全一样,因此CCD的驱动电路很难规范化、产品化,许多 CCD 用户必须面对驱动电路的设计问题。CCD时序脉冲信号是一组周期性的、关系比较复杂的脉冲信号,它是影响CCD器件的信号处理能力、转移效率、信噪比等性能的一个重要因素。线阵CCD驱动电路通常有4 种方式实现[5-8],即IC 驱动法、E2PROM 驱动法、单片机驱动法以及可编程逻辑器件(CPLD或FPGA)驱动法。其中基于可编程逻辑器件设计的CCD驱动电路具有体积小、功耗低、速度快、抗干扰强的特点,可减小电路的体积,工作频频高等优点,而且在设计完成后,如果想更改逻辑设计,不必再更改任何硬件电路,只须将可编程逻辑器件内部逻辑重新编程即可。基于可编程逻辑器件技术的CCD驱动电路的设计具有普遍性[9-10],本文研制的彩色线阵CCD实验教学系统就是基于CPLD芯片来实现CCD的驱动的。

1 彩色线阵CCD——TCD2564DG

TCD2564DG是一种高灵敏度、低暗电流,三行各为5 400像元的彩色线阵CCD,主要用于彩色图像扫描。像元为光电二极管,单像敏元尺寸为7 μm×7 μm,像元间距为7 μm,像元行间距28 μm,有效长度为37.8 mm,内置嵌位电路,封装类型为22-pin CERDIP,色彩滤光片为红、绿、蓝;两相5 V脉冲驱动,10路驱动信号的最高频率为30 MHz,理论上最高行频约为11 000;红绿蓝三色信号分奇偶并行输出,共6路输出信号;供电电源为10 V。扫描A4页面可以有24线/mm的分辨率。

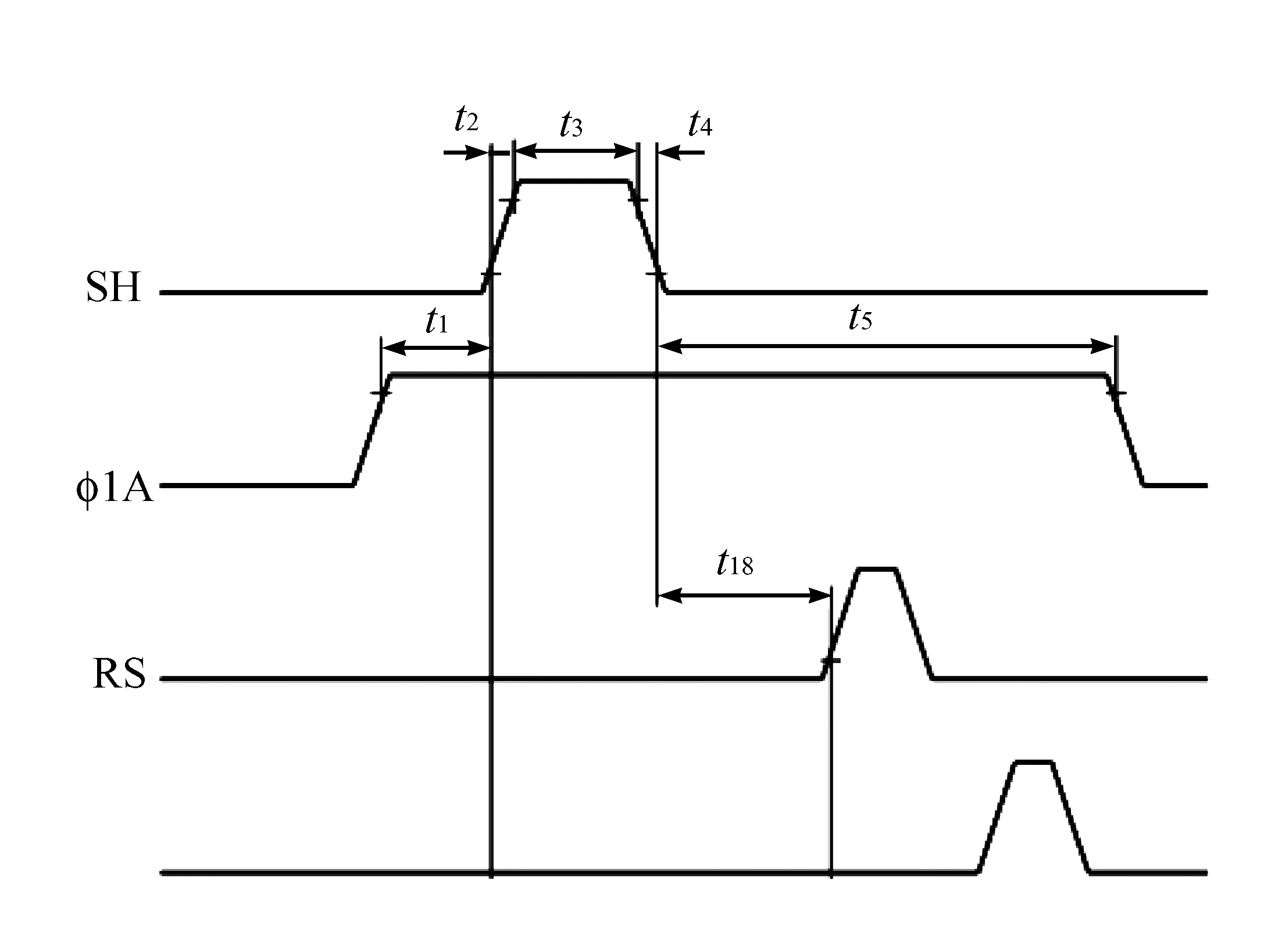

TCD2564DG正常工作时一共需要10路驱动信号,即两相各4路时钟信号 φ1A1、φ1A2、φ2A1、φ2A2以及一路φ2B、像元复位信号RS、嵌位脉冲CP、三路行同步信号SH。整个驱动信号的工作过程如下:当 SH 的高电平到来时,CCD传感器曝光的光敏单元会将采集到的光信号转移到相应的移位单元中。SH 为低电平时上述转移过程完成,光敏单元进入下一行周期感光积分,而进入移位单元中的信号将在两相操作时钟的作用下移出。RS信号的作用是减小两像元之间的相关信号,可在当前像元信号输出后至下一个像元信号到来前,对残余信号进行清除[11]。各驱动脉冲必须严格满足相位时序要求,才能保证高速CCD 器件TCD2564DG的正常工作,其依据除了其时序关系图之外,更主要的是各时序信号的时间关系要求。图1和图2给出了主要的时序关系图,表1给出了图1和图2各个时间量的典型值。其中所有的典型值都是在工作频率为1 MHz的时候的数值。视频数据的延迟时间是在负载电阻为100 kΩ时的数值。

图1 SH、φ1A与RS的时序响应图

图2 φ2B、RS、CP与OS的响应图

特性量符号最小值/ns典型值/ns最大值SH和φ1A的脉冲时间t11201 000—t51 0001 200—SH脉冲上升时间,下降时间t2,t4050—SH脉冲宽度t31 0005 000—φ1A,φ2B脉冲上升时间,下降时间t6,t7050—RS脉冲上升时间,下降时间t8,t10020—RS脉冲宽度t98100—CP脉冲上升时间,下降时间t11,t13020—CP脉冲宽度t128200—φ2B和CP的脉冲时间t14040—RS和CP的脉冲时间t1500—t168100—视频数据的延迟时间t17—6.7—SH和RS的脉冲时间t181 000——

注:—表示无上限。

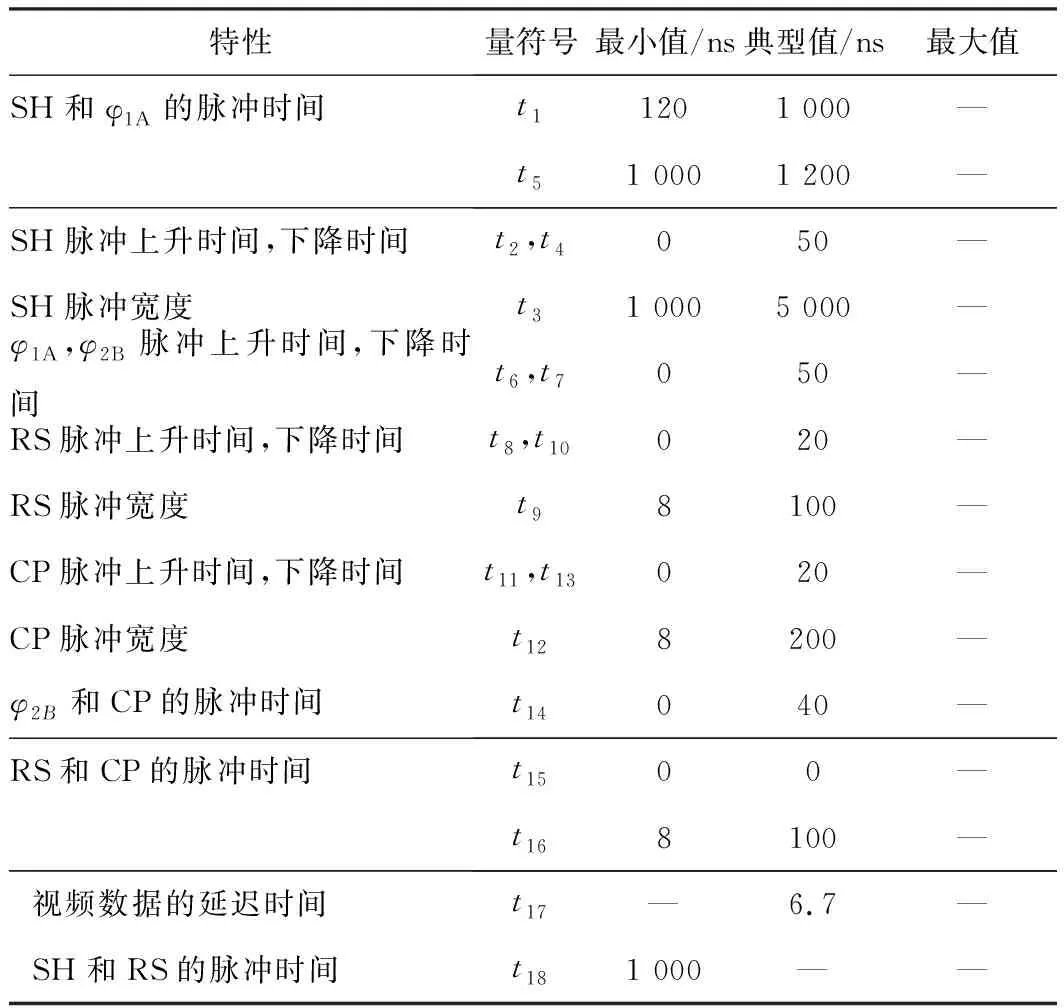

2 硬件电路设计

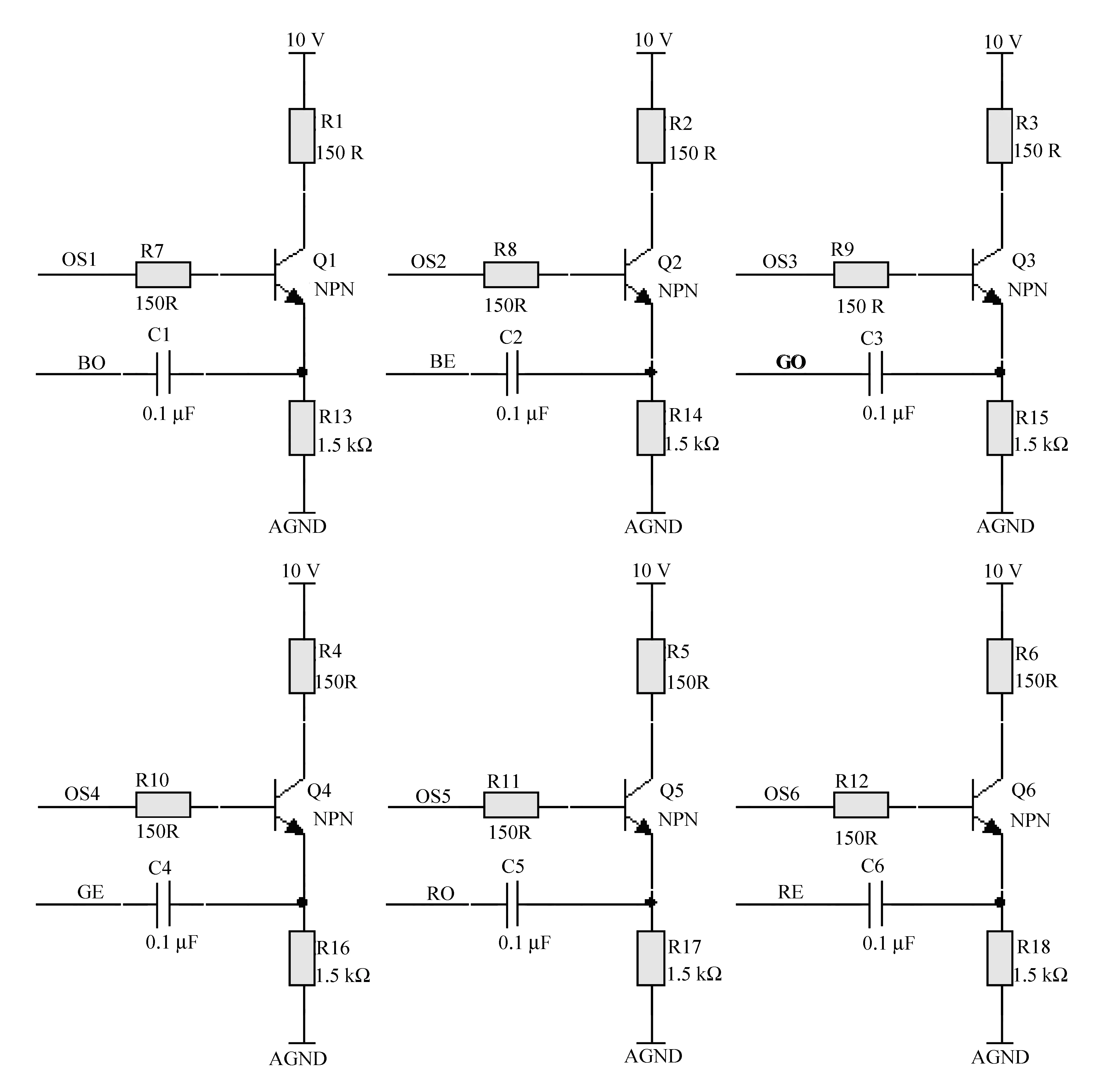

彩色线阵CCD实验教学系统使用CPLD芯片EPM240T100I5N来产生TCD2564DG正常工作所需要的驱动信号,而EPM240T100I5N工作电压标准为3.3 V,其输出的驱动信号电平标准也为3.3 V,不满足TCD2564DG的5 V脉冲驱动标准,因此使用了缓冲器74ACT11244将驱动脉冲提升到5 V的电平标准,同时增强对CCD信号的驱动能力。TCD2564DG供电电源要求为10 V,因此该系统至少需要3.3 V、5 V和10 V 3种电源。电源电路部分采用12 V直流电源供电,由于缓冲器74ACT11244的工作电压为5 V,所以通过芯片TPS54331将12 V的电源电压降至5 V。由于TCD2564的工作电压为10 V,所以通过芯片LM1117MPX-ADJ将12 V的电源电压降至10 V。用同样的芯片只需改变电阻便能将5 V电压降至3.3 V,用来给CPLD的提供3.3 V的工作电压。整体设计为晶振提供时钟信号CPLD,CPLD通过缓冲器74ACT11244将3.3 V电平提升到TCD2564的两相时钟电平5 V,然后连接信号调理电路,使TCD2564DG通过输出驱动电路输出正确的波形。系统的总体框图见图3。

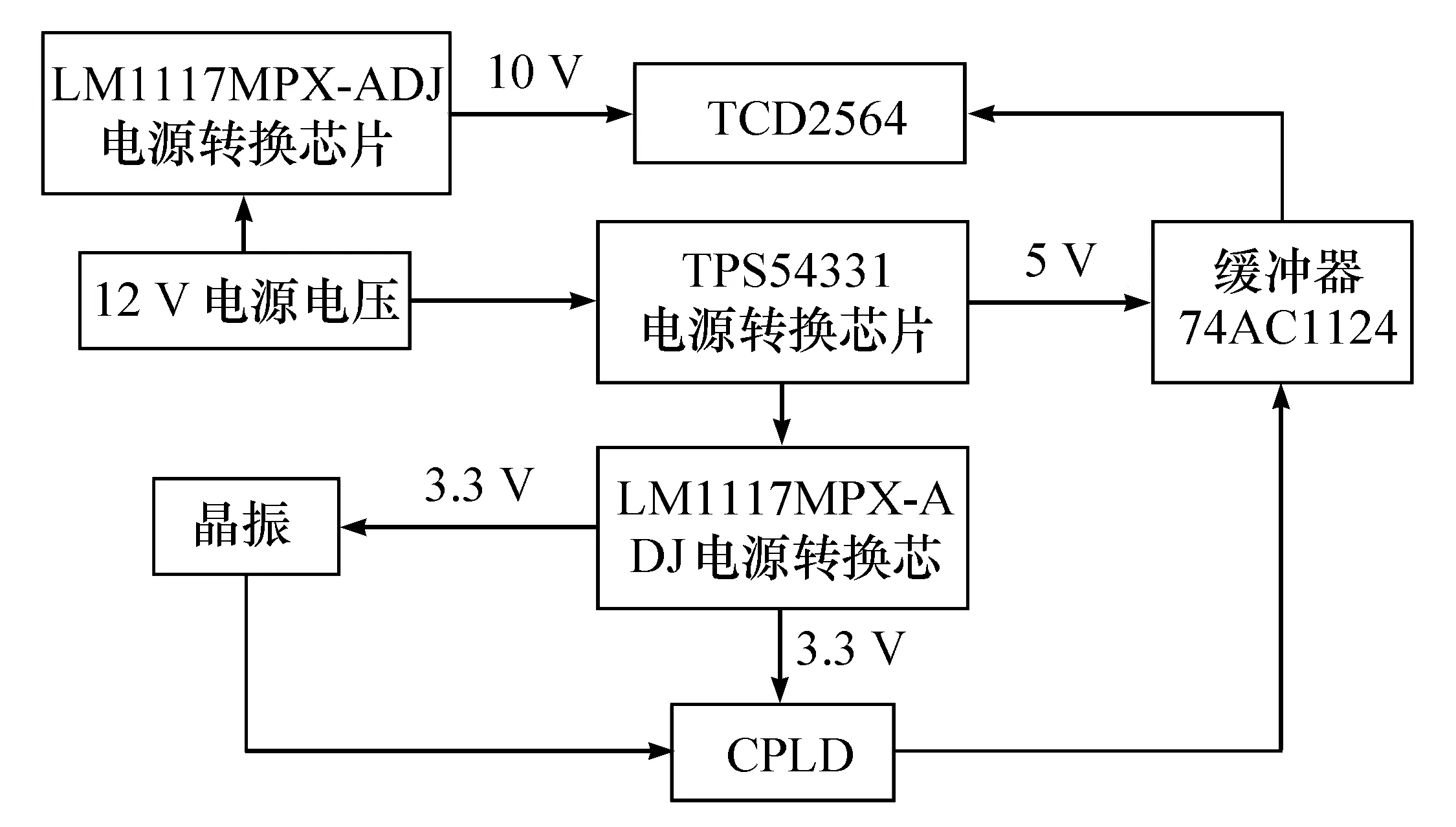

TCD2564DG红、绿和蓝3分量信号分奇偶并行输出,其输出信号驱动电路如图4所示。

图3 系统总体框图

图4 TCD2564输出信号驱动电路

图4中OS1—OS6分量为TCD2564DG管脚的输出信号,每个输出信号都包含了一个比较高的直流电平,因此这些分量信号经过三极管放大电路、再经过一个电容就输出了包含信息的交流信号。图4中R、G和B分别代表红、绿和蓝3分量,O代表偶数像元的输出,E代表奇数像元的输出。

3 CCD驱动信号设计及实验验证

TCD2564DG工作所需要的驱动信号由CPLD芯片EPM240T100I5N产生,EPM240T100I5N属于Altera公司目前市场上性价比较高的MAXII系列的CPLD,该芯片的封装为TQFP100,有100管脚,应用级别为工业级,速度等级为5,符合无铅标准,编程方式为ISP,存储器类型为Flash,工作核心电压和IO电压都为3.3 V,工作温度为-40~100 ℃,该CPLD的引脚到引脚的逻辑延时为4.7 ns,工作频率最高可达 300 MHz。

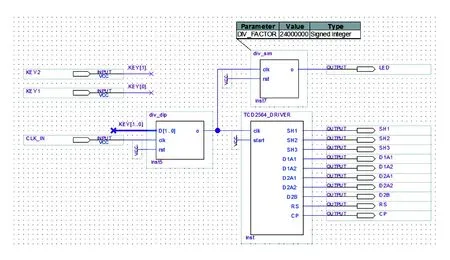

Altera公司的CPLD开发环境为QuartusⅡ软件,QuartusⅡ下有原理图输入方式、状态图输入方式、硬件描述语言输入方式等多种输入方式[12-13]。为了直观体检出驱动信号的各个模块,采用了原理图输入和硬件描述语言输入相结合的方式,总体框图由以原理图的方式提供,而原理图中的各个模块由Verilog语言编写。CCD驱动信号工程的原理图见图5。

图5 CCD驱动信号工程原理图

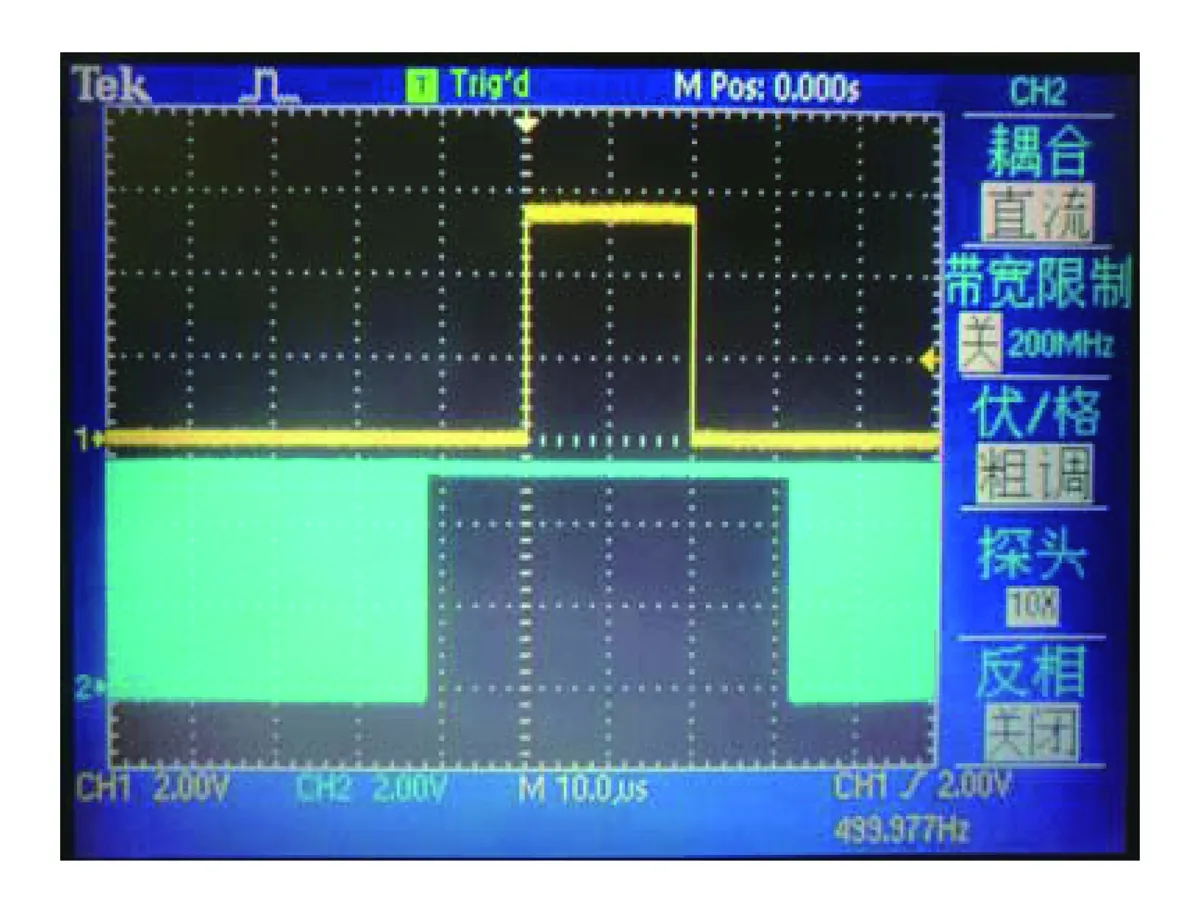

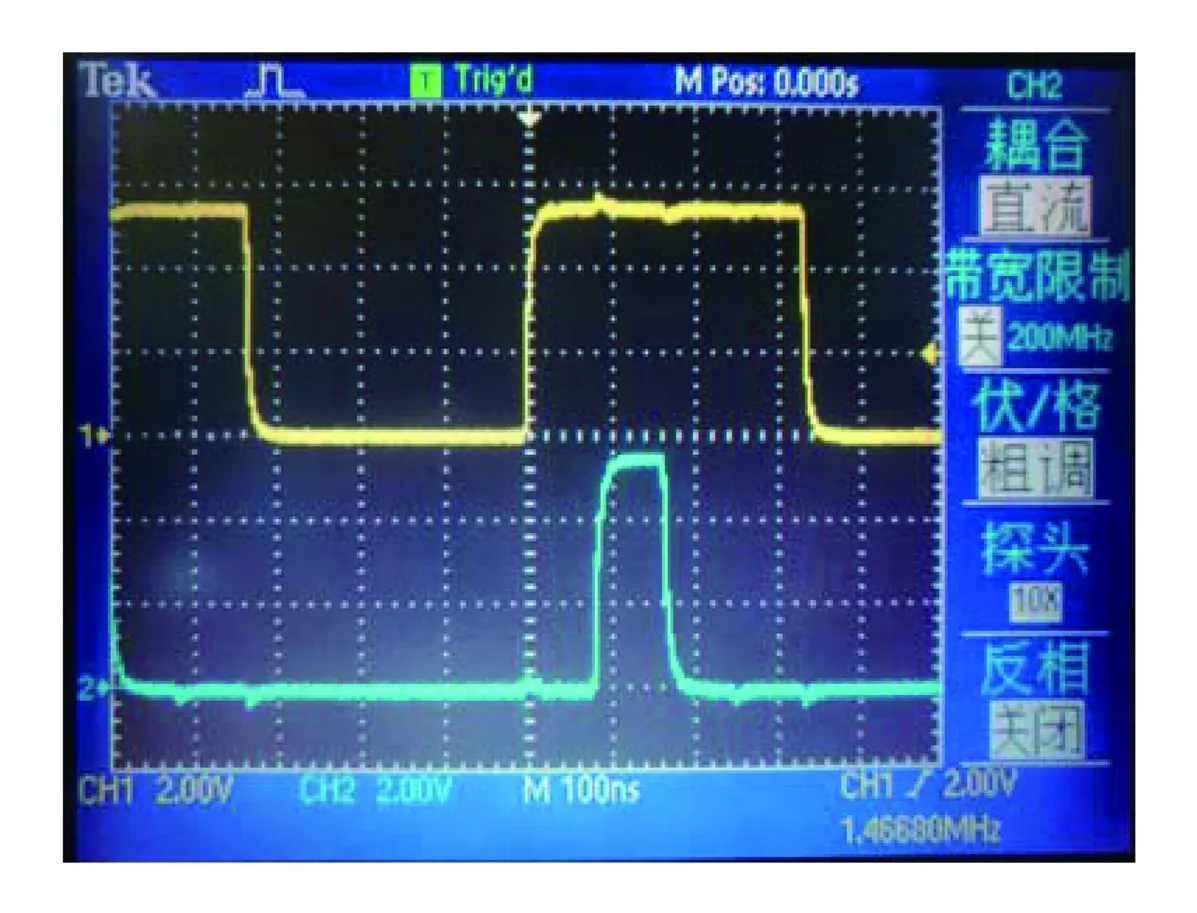

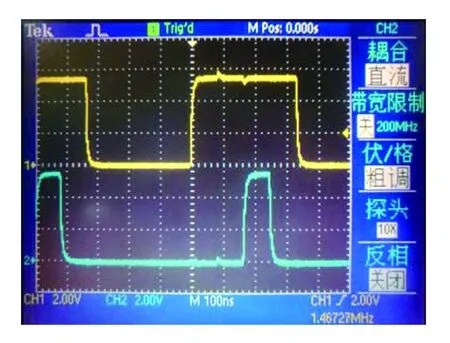

为CPLD提供时钟信号的有源晶振为48 MHz,从图5中名为CLK_IN的端口输入,模块div_dip的作用是根据外部2位拨码开关的拨码状态来对输入时钟进行分频,可以进行1分频、2分频、4分频和8分频,分频后的时钟被输给div_sim模块和TCD2564_DRIVER模块。其中div_sim模块将输入的时钟再进行分频,在输入1分频的情况下生成2 Hz的信号,通过输出端口输出给外部的LED,使LED闪烁,标志着系统的正常工作。TCD2564_DRIVER模块用于生成严格满足TCD2564相位时序要求的10个驱动脉冲信号。TCD2564_DRIVER模块的输入时钟为48 MHz的情况,4路两相时钟信号 φ1A1、φ1A2、φ2A1、φ2A2以及一路φ2B为频率6 MHz,占空比1∶2的方波信号,而像元复位信号RS、嵌位脉冲CP由于需要满足与SH的时序关系,故生成的RS和CP信号为频率略小于6 MHz,占空比1∶8的脉冲信号,3路行同步信号SH均为频率2 kHz的脉冲信号。TCD2564_DRIVER模块中各个信号之间的时序关系是按照系统的最高时钟频率,即输入时钟为48 MHz的情况设计的,当外部拨码开关的值使输入时钟被分频的情况下,时钟变慢,因而各个信号之间的时序关系依然会满足表1中各时序信号的时间关系要求。光积分时间为SH下降沿与SH上升沿之间的时间,因而时钟频率不同,则积分时间不同,可以研究积分时间对CCD输出信号的影响。当外部拨码开关的值使输入时钟4分频的情况下,4路两相时钟信号及φ2B频率应为1.5 MHz,RS和CP信号频率应略小于1.5 MHz,行同步信号SH频率应为500 Hz。时钟4分频的情况下由示波器测得的典型信号时序关系如图6—图9所示。

图6 SH和φ1A的波形图

图7 φ2B和RS的波形图

图8 φ2B和CP的波形图

图9 RS和CP的波形图

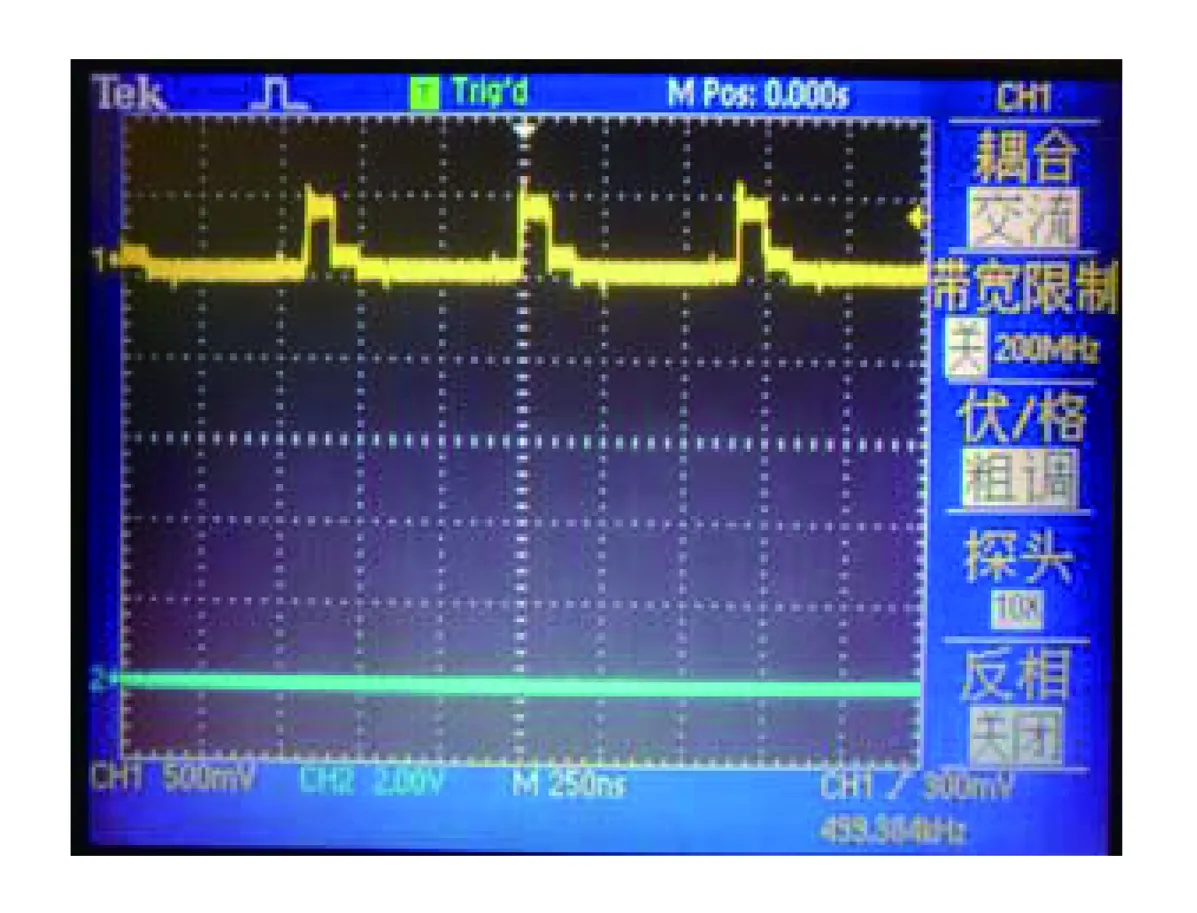

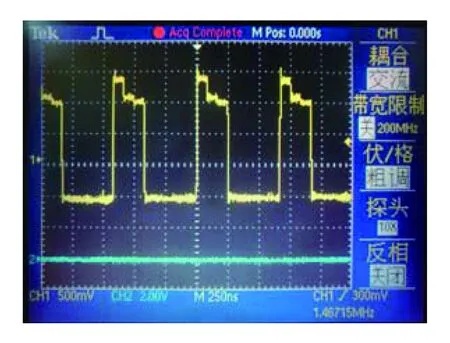

在此频率下的无光照时TCD2564DG输出信号和白光强光照射的饱和输入信号分别如图10和图11所示。

图10 无光照时的CCD输出信号

图11 白光强光时的CCD输出信号

4 基于彩色线阵CCD实验系统的实验教学内容

基于彩色线阵CCD的实验教学系统可以满足光电信息科学与工程专业光电综合实验课程的需要,在实验教学中可以开设以下内容:

(1) 利用示波器观测TCD2564DG驱动脉冲的时序和相位关系观测,并测量其驱动脉冲的频率、幅度、周期和各路驱动脉冲之间的相位关系,理解线阵 CCD的基本工作原理,尤其是复位脉冲在CCD输出电路中的作用,转移脉冲与驱动脉冲间的相位关系,掌握电荷转移过程。

(2) TCD2564DG输出信号的观察。可以观察TCD2564DG在白光光源照射下红、绿、蓝3分量各自的输出,在利用光谱仪测量出光源的光谱的情况下,得到TCD2564DG的响应度曲线,利用光源光谱与响应度曲线的乘积,将计算结果与实际输出做对比。可以连续调整光源强度观察TCD2564DG各个分量输出信号随光强变化关系;还可以在使用红、绿、蓝单色滤光片遮盖于TCD2564DG上,观察在单色光照下红、绿、蓝3个分量各自的输出信号。

(3) 通过TCD2564DG在不同驱动频率和不同积分时间下的输出信号测量,进一步掌握线阵CCD的有关特性,加深对积分时间的理解,以及驱动频率和积分时间对CCD输出信号的影响,找出积分时间、驱动频率、输出信号幅度间的关系。

(4) 实验教学系统提供了程序下载接口,学生可以自己编写TCD2564DG的驱动程序,通过QuartusⅡ软件下载到实验仪的CPLD芯片中,硬件实测线阵CCD的驱动情况,可以很好锻炼学生的编程能力。

5 结论

本文研制的基于彩色线阵CCD的实验教学系统,主要用于光电信息科学与工程专业光电综合实验课程,帮助学生实现光电检测理论与实验的结合。利用该系统可以针对彩色线阵CCD进行丰富的实验,帮助学生加深对CCD原理及驱动信号时序等理解,并可自己编写TCD2564DG的驱动程序进行实际验证,培养学生的编程能力和动手能力,为将来线阵CCD在工程项目中的应用打下坚实的基础。