3.3 V CMOS工艺下5 V电源轨的ESD箝位电路

陈迪平,董 刚

(湖南大学 物理与微电子科学学院,湖南 长沙 410082)

随着互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,CMOS)集成电路工艺发展到深亚微米阶段,静电放电(ElectroStatic Discharge,ESD)保护在可靠性设计方面愈加重要[1].为了准确评估芯片的鲁棒性,在实际测试中创建了不同模型模拟可能存在的威胁形式,主要分为: 人体模型(Human Body Model,HBM)、机器模型(Machine Model,MM)和充电器件模型(Charging Device Model,CDM)[2].一般民用芯片人体模型耐压标准为 2 kV,测试电压抬升率为 2 kV/ 10 ns.美军军标MIL-STD-883J/method 3015.9规定了军用芯片标准,耐压为 4 kV,测试电压抬升率为 4 kV/ 10 ns[3].

全芯片静电放电防护电路分为电源轨静电放电箝位电路和I/O端口静电放电箝位电路[4].目前,用于I/O端口的静电放电防护技术已较为成熟.受限于应用场合的特殊性及工艺限制,适于电源轨到地的静电放电箝位电路往往存在触发电压高、开启速度慢以及自身易损坏等缺点[5].文献[6]采用 0.18 μm CMOS标准工艺,通过对传统静电放电电源箝位电路改进,提出了一种动态侦测防护电路,具有漏电流低的优点; 文献[7]采用 0.18 μm CMOS标准工艺,基于传统接地N沟道金属氧化物半导体(Gate-Ground N-channel Metal Oxide Semiconductor,GG-NMOS)结构,提出了一款正常工作电压为 3.3 V 的静电放电电源箝位电路,具有耐压值高的优点.受工艺限制,上述文献中的设计均不适于 5 V 电源轨的静电放电箝位保护.

对于通用串行总线(Universal Serial Bus,USB)等5 V供电情况,利用 0.18 μm CMOS标准工艺实现时,需专门设计适于 5 V 电源轨的静电放电箝位电路和低压差稳压器(Low DropOut regulator,LDO)电路.基于此,笔者折中考虑了电源电压、工艺、耐压值及面积等,从整体静电放电电源轨防护网络[8]出发,利用 0.18 μm 3.3 V CMOS工艺,通过采用电平移位及低漏电流续流措施,实现了一款适于 5 V 电源轨的新型静电放电箝位电路,避免了高压工艺造成的成本增加.该电路利用分级驱动措施避免了泄放电路误触发,同时加强了对泄放管的驱动能力,正常工作时关断更彻底,减小了泄放通路的漏电流.

1 传统静电放电电源箝位电路

1.1 静电放电电源防护简介

静电放电是一个瞬态大电流事件,特点是放电电流大、速度快.静电放电防护电路设计的目的是在静电放电事件发生时,确保芯片引脚电压有适当的箝位措施,避免静电放电事件对芯片内部电路造成损坏.在设计中,静电放电防护分为器件级防护、电路级防护和系统级防护.静电放电电路级防护在保护内部电路的同时,需保证器件本身的鲁棒性,以确保芯片可靠地运行.在高电压脉冲作用下,静电放电电源箝位电路将电源轨电压箝位,避免电压过载而导致内部电路受损,同时其具备足够的电流泄放能力,吸收静电放电事件引起的瞬态大电流.静电放电防护电路在正常工作时需具备高稳定性,保证关闭; 在静电放电事件发生时,能迅速响应.静电放电电源箝位电路用于基于电源轨的静电放电系统级防护网络设计和基于PAD的静电放电系统级防护网络设计,位于电源轨之间,能及时消除电源总线和PAD高电压脉冲对内部电路的影响[9],有效地实现不同放电模式下全芯片静电放电防护.

1.2 传统静电放电电源箝位电路

早期静电放电电源防护电路多采用GG-NMOS结构,通过大尺寸的栅极接地NMOS管实现电源轨间静电放电脉冲泄放,金属氧化物半导体(Metal Oxide Semiconductor,MOS)管栅极、源极和衬底同时接地,漏区作为阳极接VDD,开启电压为漏区和衬底间PN结的反向击穿电压,漏源电压被箝位于寄生双极晶体管(Bipolar Junction Transistor,BJT)回扫电压点上,实现对内部电路的保护.但其存在触发电压高、保护能力弱以及GG-NMOS管工艺特殊/不采用最小间距设计规则等缺点.

图1 改进型GG-NMOS电路实例

基于上述不足,目前常用改进型GG-NMOS静电放电电源箝位结构.较传统结构,加入了静电放电事件动态检测电路,以控制泄放通路通断.因泄放管是由栅极控制导通而非雪崩击穿导通,导通电压较低,能够对静电放电事件迅速响应.图1所示为典型的改进型GG-NMOS静电放电电源箝位电路,其中电阻R和MOS电容M1构成动态检测电路,控制泄放管M4的导通或关断.图1所示电路的HSpice仿真波形如图2所示.图2(a)对于静电放电脉冲,节点A电压不能及时跟随电源轨静电放电脉冲的变化,正静电放电脉冲使M2导通,在保证M2导通能力强于M3的情况下,VB上升,致使M4导通,静电放电泄放通路打开,完成静电放电脉冲泄放; 图2(b)是正常工作时,A点电压有充足的时间上升,使B点电压为低,泄放通路关闭,不影响电路正常工作.

图2 改进型GG-NMOS电源箝位电路的瞬态响应

在USB等 5 V 供电场合,为避免高压工艺所造成的成本增加,采用 0.18 μm CMOS标准工艺实现时,因工艺限制,器件正常工作电压多为 1.8 V 和 3.3 V,图1所示结构不适于 5 V 电源轨的静电放电箝位防护.基于此,笔者在传统静电放电电源箝位电路的基础上,采用电平移位以及低漏电流续流措施完成了一种适于 5 V 电源轨的静电放电箝位电路设计,同时利用分级驱动强化了正常上电时泄放通路的关闭程度,降低了该电路正常工作时的漏电流,可靠地实现了 0.18 μm CMOS标准工艺下 5 V 电源轨的静电放电箝位设计.

2 3.3 V CMOS工艺下5 V电源轨的静电放电箝位电路

2.1 电路设计

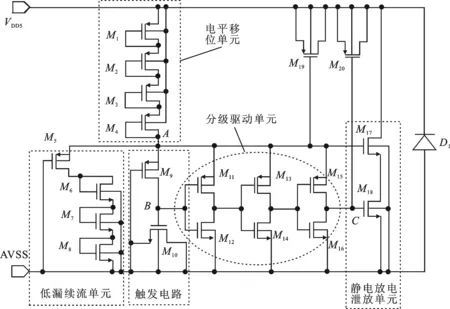

基于工艺限制以及上述电路的不足,笔者设计了一种适于 3.3 V CMOS工艺的 5 V 电源轨静电放电箝位电路,如图3所示.设计分为5个部分: 电平移位单元、低漏续流单元、RC触发电路、分级驱动单元以及静电放电泄放单元.

图3 3.3 V CMOS集成电路工艺下5 V电源轨的静电放电箝位电路

正常上电响应:MOS电容M10两端电压VB逐渐抬升;当上电完成后,VB为高电平,经分级驱动单元对B点电压波形整形,分级驱动单元输出可靠的逻辑低电平(地电位),使M18关闭,切断了泄放支路漏电流通路.在设计中:

(1) 工作于亚阈值区的电平移位单元M1~M4.完成VDD5(5 V) 到 3 V 左右的电平移位(一般地,亚阈值工作区MOS场效管过驱动电压约为 -100 mV,考虑到实际工艺下P沟道金属氧化物半导体(P-channel Metal Oxide Semiconductor,PMOS)阈值电压约为 -600 mV,故采用四管予以实现),以确保正常工作时,3.3 V 工艺晶体管长期可靠地工作.据文献[10],亚阈值系数为

C=ID/[I0(W/L)] ,

(1)

(2) 低漏续流单元M5~M8.在电路正常上电时,为电平移位单元提供适当的亚阈值电流.亚阈值区晶体管漏极电流ID与柵源电压VGS的近似关系为[11]

(2)

其中,VT=KT/q,为温度电压;n=1+Cdep/Cox;Cox=ε0εr/tox,为栅氧化层单位面积电容,ε0为真空介电常数,εr为栅介质材料相对介电常数,tox为栅氧化层厚度;Cdep为单位面积沟道耗尽层电容;μ为载流子表面迁移率;VTH为阈值电压.据式(1)和式(2),M5~M8采用大比值倒比管实现,以降低正常电源电压下的漏电流.

(3) 分级驱动单元.完成对泄放管M18的驱动电压波形整形,产生驱动逻辑电平,使得M18迅速彻底地关断,降低泄放通路的漏电流.为降低正常上电过程中以及稳态时的漏电流,设计中,M11和M16采用长沟道晶体管予以实现.

正静电放电脉冲响应:当电源正常工作时,泄放管M17导通,起分压作用,正脉冲通过电平移位单元M1~M4迅速耦合到节点A.由于RC延迟以及分级驱动单元延迟作用,M15对正脉冲的响应快于对节点B电位变化的响应,正脉冲使M15导通并迅速传输到节点C,致使泄放管M18导通,泄放通路形成.为确保泄放通路的响应速度,电平移位单元及晶体管M15均采用较大的宽长比予以实现,以保证静电放电事件到来时,泄放通路迅速彻底地导通.当电源未上电时,因电平移位单元M1~M4的响应速度过慢,采用MOS电容M19和M20,迅速将正静电放电脉冲耦合到节点A和节点C,以确保泄放通路及时可靠地导通.此举亦有助于正常上电时,静电放电电源箝位电路对正静电放电脉冲的响应.为确保泄放通路电流容量充足,静电放电泄放单元采用大的宽长比予以实现.

负静电放电脉冲响应:在负静电放电脉冲作用下,晶体管M17的漏区—衬底二极管正向导通,形成有效的泄放通路.在设计中,M17采用宽沟道管予以实现,以确保充足的电流容量,实现对内部电路的保护.此外,负脉冲会通过电平移位单元以及MOS电容M19、M20耦合到节点A和节点C,在脉冲到来时,该电路形成M17栅极—PMOS电阻(M5)—M6漏极(N)—M6衬底(P)—AVSS(地)的有效泄放通路,以避免M17的栅氧化层被击穿.同理,可形成M18栅极—M16漏区(N)—M16衬底(P)—AVSS(地)的有效泄放通路,以避免泄放管M18的栅氧化层被击穿.

文献[12]中提出,测试系统引入的电源轨残留电荷会影响静电放电箝位电路正常工作,导致泄放通路MOS场效管电压回滞先于RC触发单元响应而开启.笔者利用二极管D1消除电源轨残留电荷引起的MOS场效管回滞电压响应的偏移.在回滞电压响应存在偏移时,正静电放电脉冲作用下D1反向击穿,负静电放电脉冲作用下D1正向导通.此举在泄放通道因偏移而未开启的情况下,实现对内部电路保护,避免电源轨残留电荷造成静电放电电源箝位功能失效.相对于多晶硅电阻,PMOS电阻响应更快,因此笔者采用PMOS电阻代替多晶硅电阻,以提高电路的灵敏度,此举亦有利于减小芯片的面积.一般地,静电放电事件上升时间约为 2~ 10 ns,持续时间约为 150 ns; 正常快上电时间约为 100 μs,慢上电时间约为 1 ms.考虑分级驱动单元反相器延时,在设计及仿真模型搭建中,RC时间常数介于 0.5~ 50 μs 之间,以确保电路在正常工作及静电放电事件作用下工作合理.

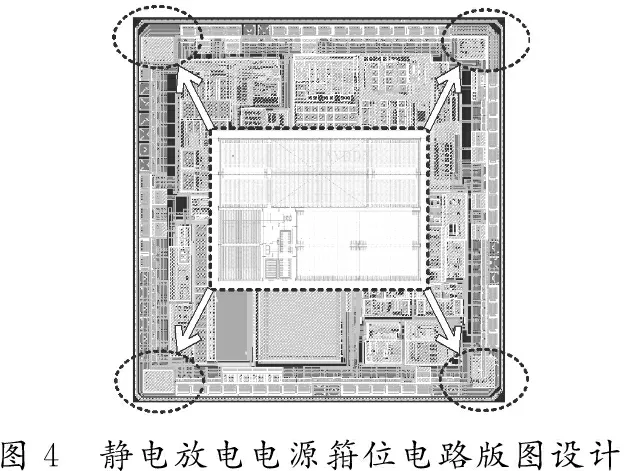

图4 静电放电电源箝位电路版图设计

2.2 仿真分析

静电放电电源箝位电路版图设计如图4中虚线区域所示.CMOS集成电路中器件隔离主要由反偏PN结实现.当负静电放电脉冲放电时,电路中反向隔离的PN结处于正向偏置,具备很强的泄放能力.因此,在电路设计中主要考虑正静电放电脉冲放电的情况.设计采用HSpice仿真工具,基于SMIC 0.18 μm CMOS工艺库模型,对笔者设计的静电放电电源箝位电路进行了仿真分析.

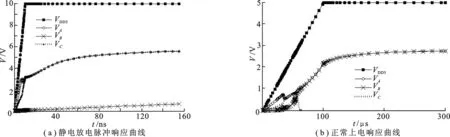

用上升时间为10 ns、脉宽为150 ns、幅度为0~10 V的方波脉冲模拟静电放电电压.笔者设计的静电放电电源箝位电路中各节点的电压波形如图5(a)所示.正静电放电脉冲作用下,节点A和节点C电位迅速上升并超过 5 V,使得泄放晶体管打开,形成有效的泄放通路,实现对静电放电脉冲的泄放.用上升时间为 100 μs、幅度为 0~ 5 V 的分段线性电压源模拟电源正常上电的情况,仿真结果如图5(b)所示.当电源电压正常工作时,VA和VB约为 2.8 V,保证了静电放电电源箝位电路所有器件的正常工作.VC为地电位,使M18关断,有效地切断了泄放通路,降低了漏电流.比较图2,图5所示结构在保证静电放电事件和正常上电情况下,在保证电源轨箝位保护电路的正确性和有效性的同时,确保了电路核心节点的电压低于工艺要求,验证了该电路的可靠性.由此可见,笔者所设计的新型 5 V 电源轨静电放电箝位电路可靠地实现了 3.3 V CMOS工艺下,5 V 电源轨静电放电箝位防护,并通过HSpice仿真验证了笔者设计的静电放电电源箝位电路的正确性和有效性.

图5 笔者设计的静电放电电源箝位电路响应波形

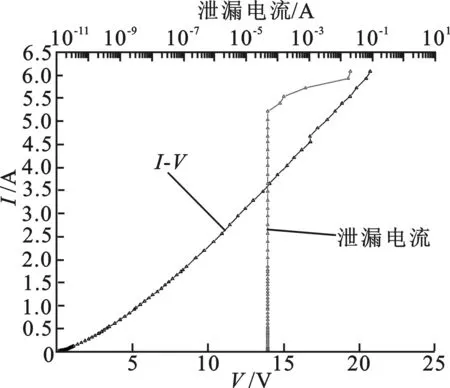

图6 TLP测试结果

3 测试结果

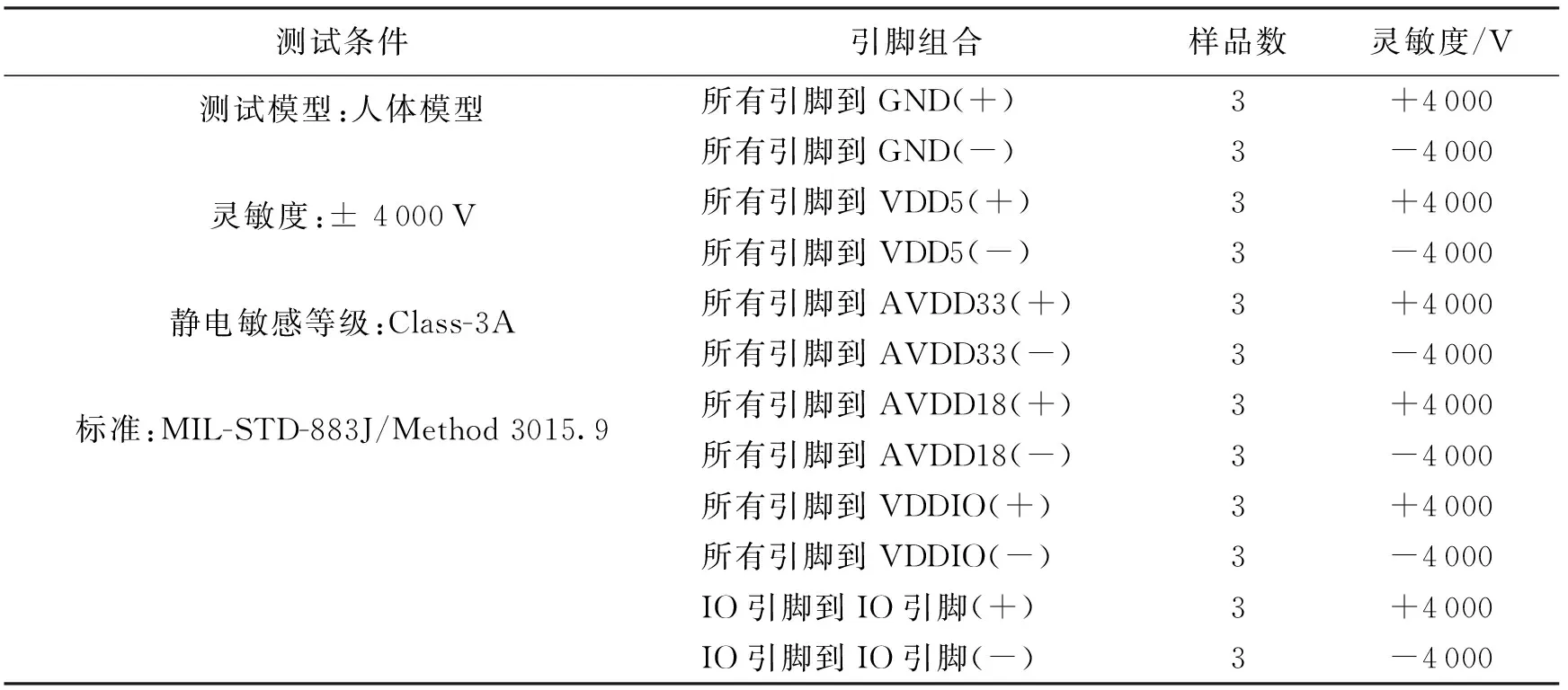

为验证上述 5 V 电源轨静电放电箝位电路的性能,利用中芯国际集成电路制造(上海)公司(Semiconductor Manufacturing International Corporation,SMIC) 0.18 μm CMOS工艺对该电路进行了流片.流片后的整体芯片可正常工作,笔者设计的静电放电电源箝位电路不影响整体芯片的正常工作.图6所示为该电路在传输线脉冲(Transmission Line Pulse,TLP)测试平台测得的曲线,其二次击穿电流It2约为 5.2 A,正常工作时泄漏电流约为 28 μA.较整体芯片而言,正常工作时该电路静态功耗影响较低,满足设计要求; 基于人体模型静电放电标准MIL-STD-883J/Method 3015.9,对流片后的芯片样品进行测试,结果如表1所示.测试结果表明,笔者设计的静电放电电源箝位电路达到静电敏感等级Class-3A级,即达到设计要求,适于民用芯片静电放电防护设计.

表1 静电放电测试结果

4 结 束 语

通过对传统静电放电电源箝位电路的结构和工作原理分析,针对其不足及工艺限制,笔者设计了一种适于 3.3 V CMOS工艺的 5 V 电源轨静电放电箝位电路.基于SMIC 0.18 μm CMOS工艺库模型,使用HSpice工具仿真验证了该电路的正确性.笔者设计的静电放电箝位电路已在一款自主芯片中实际应用.设计采用 0.18 μm CMOS工艺下的普通器件,降低了电路成本.流片结果通过了人体模型 ±4 000 V 测试,达到静电敏感等级Class-3A级,满足设计要求.