高符号速率16APSK信号解调器的设计与实现

何朝玉,彭战武

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.陆军北京军事代表局,北京 100012)

0 引言

随着我国高分辨率遥感卫星的发展,遥感数传速率需求已达3 Gbps,因此有必要进行超高速率的高速解调器研究。文献[1]采用QPSK调制方式实现1 Gbps高速数据的传输,通过提高带宽实现高速传输。文献[2]采用16APSK调制方式,双通道传输,实现2 Gbps高速数据的传输。相对于QPSK,16APSK调制方式在带宽不变的情况下将传输速率提高1倍;双通道传输节省了传输带宽,但是需要2套接收设备。随着V频段等更高载波频率的使用,很大程度上解决了传输系统的带宽受限问题,高频段功放器件的出现也解决了高阶调制方式的传输功率问题,这都使高符号率高阶调制方式的实现成为可能。

对于解调器的实现方式,一般有数字化中频解调和模拟中频解调。数字化中频解调的采样方式为中频采样,比模拟中频解调节省了微波模块,采样后的信号正交性好,但软件处理复杂度提高,且处理高速信号需要考虑AD采样能力。

本文通过提高传输带宽和采用16APSK高阶调制方式,使传输速率达到3.72 Gbps,重点研究高速解调器的关键技术实现。

1 总体设计

遥感数传高速解调器用于完成接收信号的解调同步和信号均衡等功能,本文接收信号的符号速率为930 MS/s,调制方式为16APSK,接收中频为1.2 GHz。首先,在考虑工程实现的基础上,综合接收信号的速率、中频、格式和帧结构等,制定合理的实现方案,实现信号的可靠接收。

1.1 信号模型

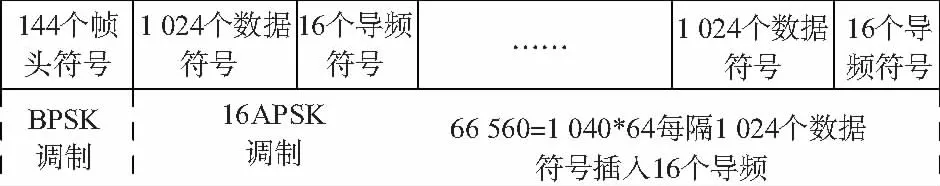

16APSK映射采用文献[3]中的4-12APSK映射星座图。接收数据帧由帧头、导频和数据符号组成,如图1所示。帧头符号为144个,可用于信号的频偏估计[4],帧内分散插入64组导频符号用于辅助同步处理,帧头和导频符号均为BPSK调制[5]。按以上设计的数据帧符号长度为66 704个,帧效率为98.24%。

图1 帧结构示意

1.2 信号处理方案

目前,信号处理方案主要有2种:中频采样[6]和基带采样。2种方案对比,中频采样方案不需要模拟正交下变频模块,将中频信号采样后全部由FPGA处理,避免模拟器件带来的IQ正交不平衡问题,且集成度高、灵活性高;但是在信号带宽比较高时,为了避免采样后信号出现混叠,要求采样频率很高,这对AD芯片采样频率指标提高了要求,此时AD芯片和FPGA的接口调试更加困难。采用基带采样的方案,AD采样频率大于等于2倍的符号速率即可[7],模拟器件带来的IQ正交不平衡问题可以由FPGA内信号均衡模块进行补偿。

本文中接收信号中频为1.2 GHz,符号速率为930 MS/s,采用中频采样时AD的采样频率最低为3 060 MHz,采用基带采样时采样频率为1 860 MHz即可。采用基带采样的方案可以降低对AD芯片的采样频率要求,且解调同步的算法实现简单。

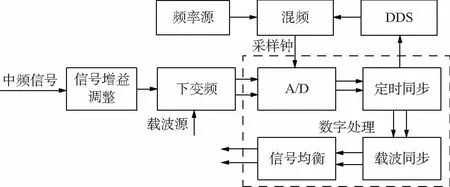

信号处理方案的框图如图2所示。中频信号经过增益调整、下变频[8]和AD采样后送入FPGA内进行同步和信号均衡处理。

图2 解调信号处理原理

经过下变频后的信号,由于信道的影响,产生了严重的码间串扰,采用矢量信号分析仪测试EVM[9]达到20%,接收信噪比很低,因此需要考虑在低信噪比条件下进行解调同步处理。

2 关键技术

2.1 时钟同步

时钟同步采用Gardner环[10]实现,AD芯片以2倍符号速率进行采样,每符号采样2次,在时钟同步时,一次采样在符号峰值点,另一次采样在相邻符号的过零点。此算法适合于数字实现,2倍采样使运算量不会过大,且算法独立于载波同步,定时同步可先于载波同步建立。

Gardner算法最初用于BPSK/QPSK[11]信号同步,文献[12]证明Gardner算法与调制方式无关,因此Gardner算法适用于16APSK调制方式。Gardner算法提取出的误差,经过环路滤波后控制DDS的频率调整[13],DDS的输出与固定的频率源混频后作为AD的采样钟。总的来看,由定时误差控制AD采样钟的频率调整从而实现定时同步。

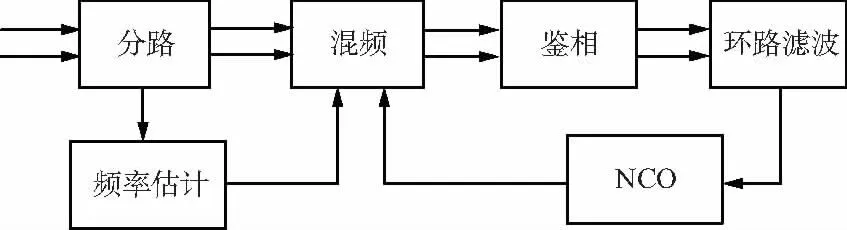

2.2 载波同步

载波同步可以先利用已知的帧头数据进行频率估计[14]和补偿,经过频率补偿后的数据仍然存在残余的频偏。残余频偏可以利用数据帧内插入的BPSK导频,利用判决反馈环算法[15]进行跟踪补偿,实现接收信号低信噪比情况下的载波同步,实现框图如图3所示。

图3 载波同步实现

假设信号经过理想定时同步,无码间串扰,则存在频偏和相偏的帧头数据可以表示为:

rk=akej(2πΔfkT+θ)+nk,

(1)

(2)

(3)

估计分辨率由FFT运算的点数决定,在帧头符号确定情况下,可以通过补0的方法提高FFT估计的分辨率[16]。

帧头为144个符号,对其补0做8 192点的FFT变换,则其估计分辨率为1/8 192,进行频偏补偿后的归一化残余频偏小于1/16 384,经过校频之后,利用帧内插入的导频,采用判决反馈环路对残余的频偏进行跟踪补偿[17]。

2.3 信号均衡

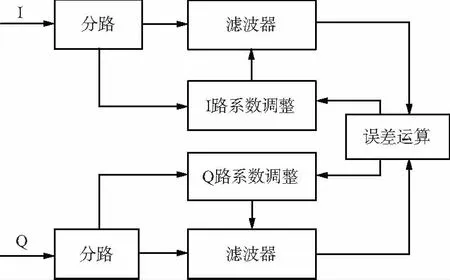

高符号速率信号在带限信道中传输时,存在码间串扰[18]现象,造成传输误码率的提高。码间串扰主要来源于信号传输群时延不理想、传输信号幅度不平衡和下变频模块带来的IQ不平衡。考虑信道的影响因素,本文采用基于最小均方误差算法的线性均衡器,对同步后的信号进行均衡补偿。为了消除IQ正交不平衡[19]的影响,在进行误差运算时,将IQ两路均衡后的数据同时引入误差运算模块与理想的星座点进行硬判决比较,实现框图如图4所示。

经过调试,滤波器采用33阶FIR滤波器实现,滤波器的抽头量化为16位,利用输入信号和判决后的误差控制滤波器的抽头调整,实现自适应均衡。

图4 均衡实现框图

3 性能测试

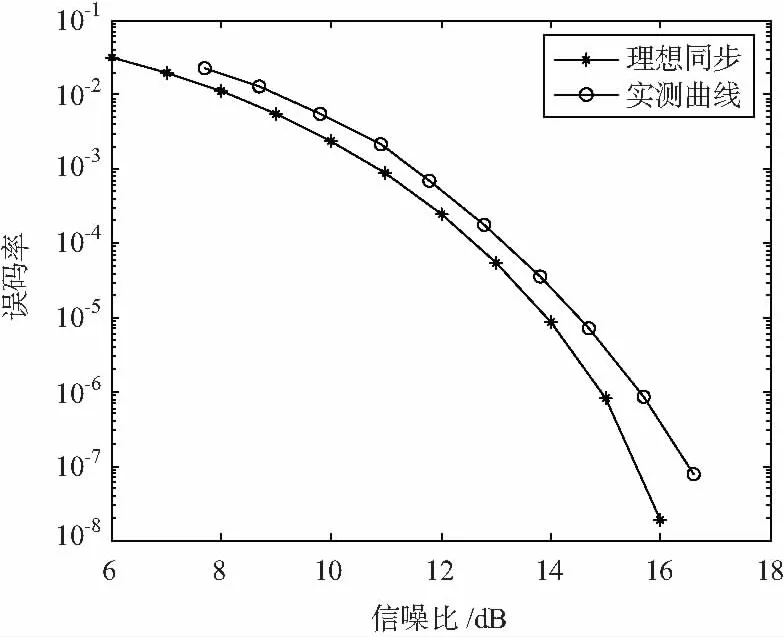

采用VHDL语言[20]对上述设计进行实现,并加载到硬件平台。在L频段,搭建测试环境对高速解调器进行误码率性能测试。设备测试框图如图5所示。任意波形发生器产生测试用的中频信号,中频1.2 GHz,符号速率930 MS/s,调制方式16APSK,通过调节宽带噪声源设置,施加不同强度的噪声,经过高速解调器解调输出后送误码仪测试,获得不同信噪比下的误码率性能。解调性能测试结果如图6所示。从测试性能曲线可以看出,在误码率为1×10-7时解调器的解调损失小于1 dB。

图5 设备测试框图

图6 解调性能测试结果

4 结束语

本文在综合分析信号模型和硬件实现难度的基础上,设计了中频模拟下变频和基带采样的实现方案。此方案降低了对AD芯片采样频率的要求。由于码间串扰造成接收信噪比降低,采用Gardner环实现时钟同步;载波同步利用数据的帧头和导频,采用开环估计和闭环跟踪实现载波同步,使解调器在接收信号恶化的情况下正常工作。采用最小均方误差线性均衡器消除码间串扰,提高误码率性能。经过测试,设计实现的高速解调器可以实现符号速率为930 MS/s的16APSK信号的解调,在误码率为1×10-7时解调损失小于1 dB,满足实际工程需要。