基于MIPS架构的多周期CPU设计

柳 成,荣 静

基于MIPS架构的多周期CPU设计

柳 成,荣 静

(扬州大学广陵学院,江苏 扬州 225000)

为了提高多周期CPU流水线的效率,在指令存储器和数据存储器的数据读取中设计发送地址在上升沿、读取数据在下降沿,从而实现译码和访存在一个周期内完成。在取指级不再单独设置加法器,把PC+4放在ALU中完成。通过大量的多路选择器与数据交互总线来进行数据联通。采用Verilog HDL语言设计出CPU,并在VIVADO平台上实现仿真,最后通过龙芯公司的LS-CPU-EXB-002试验箱来进行验证,结果表明所设计的多周期CPU的有效性。

流水线;Verilog HDL;多周期CPU;LS-CPU-EXB-002试验箱

0 引言

MIPS架构是为流水线而生,每条MIPS指令的执行分为五个部分,每一个部分为一个流水级。MIPS是最简单且内核开源的微处理器之一,相对于其它架构微处理器,相同位数的MIPS架构的时钟频率较低,其运行速度也较慢。高效的CPU要求流水线的每一个阶段都占用固定的时间,再通过缩短流水线各个阶段的执行时间来提高时钟频率,在此我们通过改进取地址和读数据时钟控制来实现。

传统的MIPS架构多周期CPU的设计中,在发送地址的下一拍才能获得相应的数据,从指令和数据存储器中读取数据就需要等待一个周期,这样往往会造成资源浪费。为了消除这个闲置时间,将发送地址设计在时钟的上升沿,读取数据放在下降沿,最终实现32位MIPS架构多周期CPU。

1 多周期流水线技术和MIPS指令系统

1.1 流水线设计

MIPS体系结构主要采用了流水线技术[1],它把一条指令的执行分为几个周期来完成。这样每个周期处理器只做一件事,大大的减轻了处理器的任务,使处理器的频率更快,处理器也更高效。通过改进文献[2]中的五级流水线得到如图1所示的多周期CPU流水线设计。

1.2 MIPS指令系统

32位MIPS架构的汇编指令长度为32位,都是三操作数指令,在此直接采用MIPS32指令系统中的20条指令[2,3]。分为五种类型,具体如表1所示。

图1 多周期CPU流水线示意图

表1 指令格式

其中rs和rt是源操作数的寄存器号;rd是目的寄存器号,有时也可以做源寄存器号;immediate表示立即数,offset是偏移量,address是地址,sa是移位量。

2 MIPS架构的多周期CPU设计

本文将分为取指、译码、执行、访存、写回五个阶段[4]来设计。

2.1 取指令阶段

在此阶段CPU主要完成两个任务,一是PC+4,二是根据PC值从指令存储器[5]中取出指令。当IF级运行时,执行级处于闲置状态,设计 PC+4在ALU中完成,不再单独设置加法器。通常CPU读取地址后,需要等待一个周期,再读取数据。但事实上,这一个周期里只有上升沿有效,下降沿是空闲,而对于多周期CPU来说又不存在数据相关问题,所以使读取地址放在上升沿,获取数据放在下降沿,这样只需一拍时间就能完成取指。

2.2 译码阶段

此阶段主要完成的任务是把操作码op、功能码sa送入控制器中,得出控制信号,由控制信号来决定CPU接下来的任务[6]。主要控制信号有指令操作、存储操作、执行操作、写回操作任务和PC值变化形式。

为了使资源利用最大化,我们将跳转指令的高位加载也放在ALU中进行,立即数的扩展设置专门的扩展电路来完成,由控制信号EXTOP来决定是零扩展还是符号扩展。

2.3 执行阶段

跳转指令在译码阶段已经完成了,其他四种类型指令将进入执行阶段,不同类型指令在执行阶段的情况也不同[7]。我们在执行阶段设置一个新的判决电路模块[8],把在存储器、寄存器堆中取出的数据和控制器发出的相关控制信号送进去经过判决生成两个信号,作为ALU操作数端口前的数据选择器的选择信号。

2.4 访存阶段

在此阶段读取高速缓存中的数据变量。在MIPS架构中只有两条指令用到它,lw(读数据)和sw(写数据),在执行级中已计算出存储器的地址

为了在执行写字节时,依据地址的低两位,移动store的字节到对应的位置,我们在数据存储器前后各设置一个四选一数据选择器。在此阶段设置时钟上升沿从EX_MEM总线中取出数据,向存储器中发出地址,在时钟下降沿中读出数据,然后锁存在MEM_WB总线中。

2.5 写回阶段

此阶段就是为了把ALU计算的数据或者是在存储器中取出的数据写回到寄存器堆中,其中写回的目的寄存器号有rt和rd。

2.6 状态机和多周期的总体电路

设计六个状态,分别是空闲、取指、译码、执行、访存和写回。令IDLE表示为空闲状态、FETCH表示为取指阶段、DECODE表示为译码阶段、EXE表示为执行阶段、MEM表示为访存阶段、WB表示为写回阶段。在译码阶段要判断跳转指令有效值和译码完成有效值的“与”运算是否为1,为1则跳回取值级,否则进入下一阶段。多周期CPU状态机[9]示意图如图2所示,整个多周期CPU的结构设计如图3所示。

图2 多周期CPU状态机示意图

图3 多周期CPU结构图

3 仿真与验证

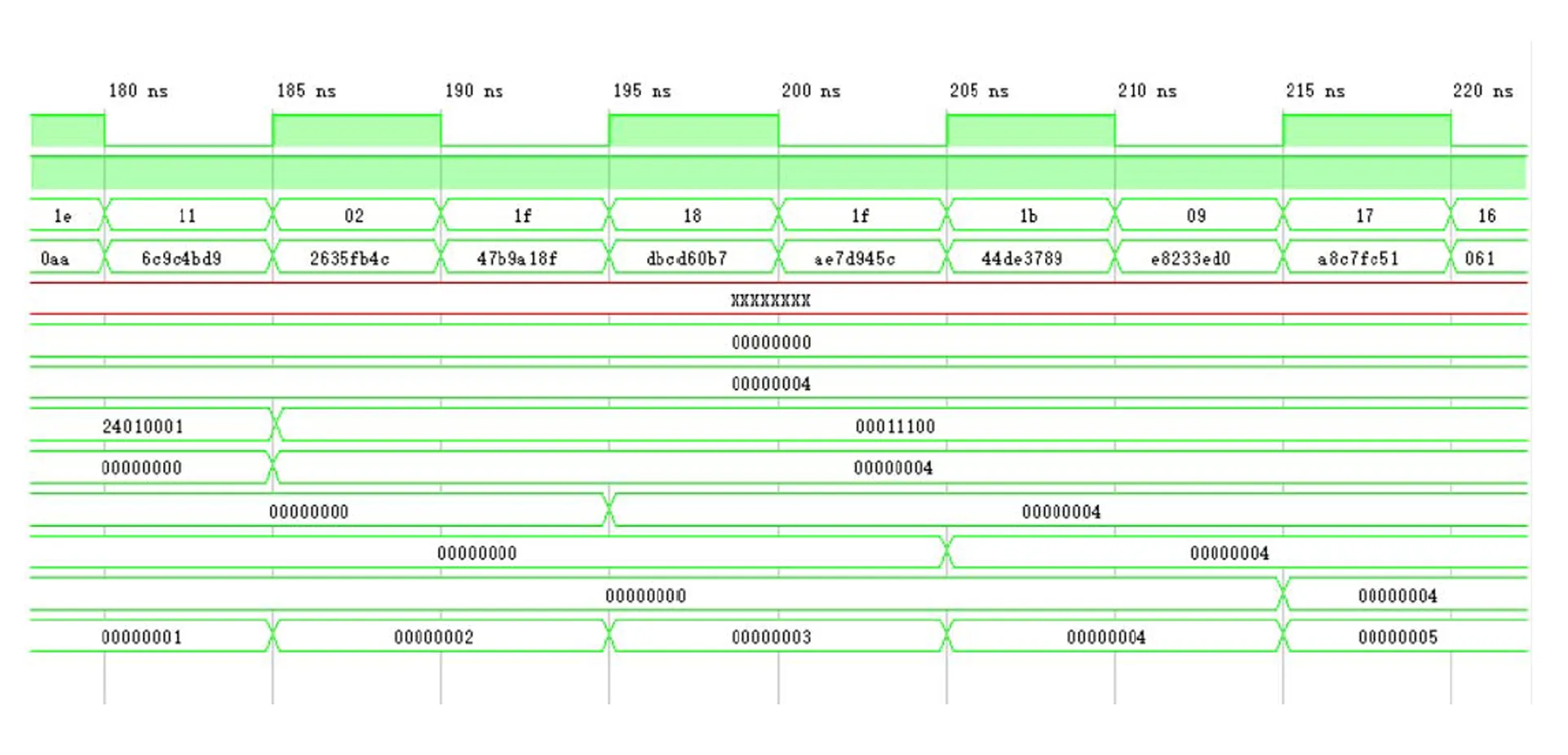

(1)仿真图

我们采用Verilog HDL语言来实现整个CPU功能[10],在VIVADO上编译仿真。图4是多周期CPU对预设指令执行的部分仿真[11]图,其中红色的高阻状态总线表示的是寄存器堆取数据,此时CPU在执行指令的过程中从交互总线锁存器中取数据,所以寄存器堆处于高阻,在写回阶段完成后,数据将会写回到寄存器堆中。

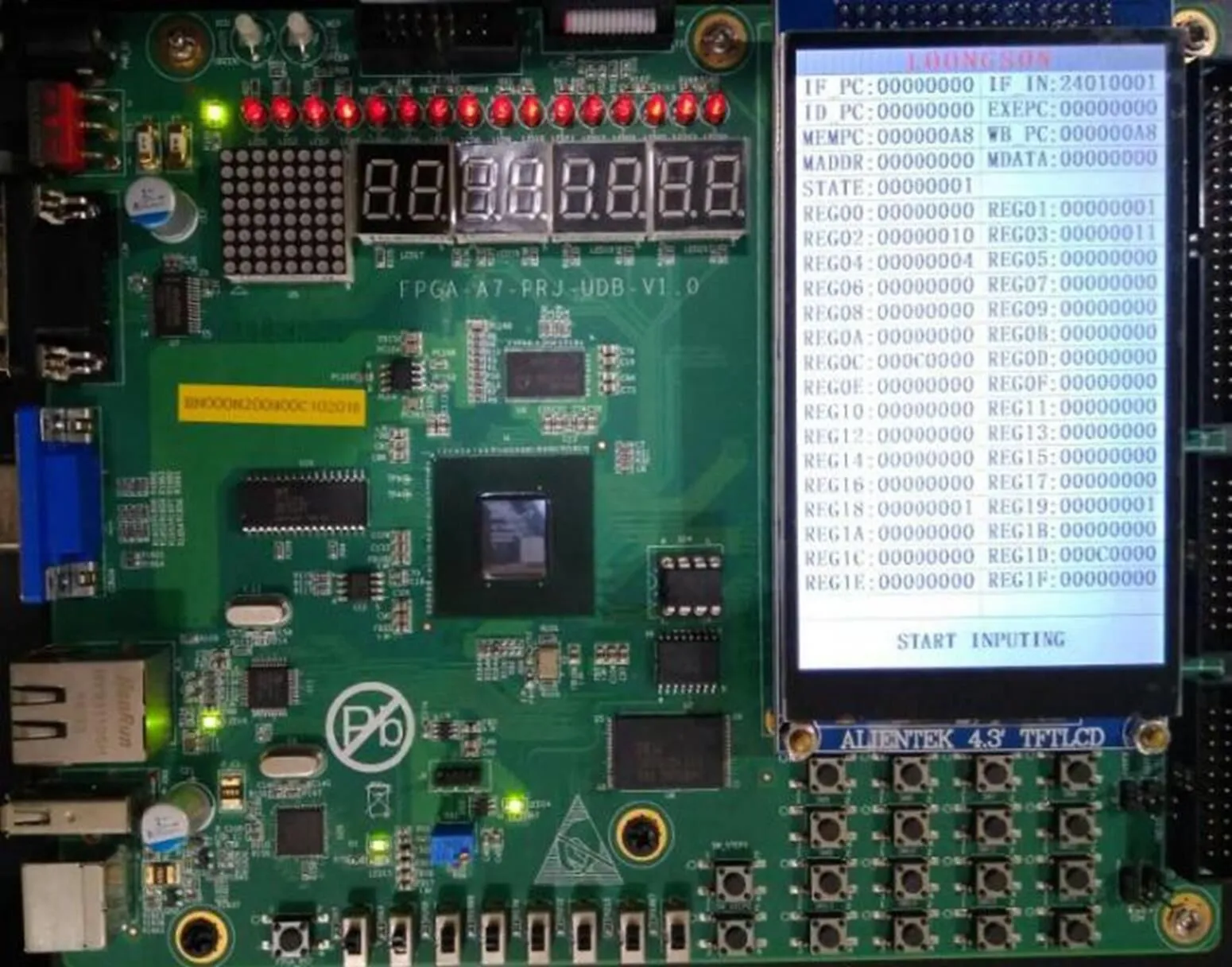

(2)实验箱验证

LS-CPU-EXB-002实验箱[12,13]采用了简单化的输入输出控制接口,它的触摸屏实现的是硬件驱动,可以随时进行输入输出,通过该实验箱来验证所设计的多周期CPU的有效性。如图5所示,其中IF_PC表示IF模块PC值,ID_PC、EXEPC、MEMPC、WB_PC表示当前模块的PC值,IF_IN表示从IF级中取出的指令,MADDR表示存储器地址,MDATA表示从存储器中读出的数据,REG表示32位寄存器测试标识符,随着PC值的变化,不断的有结果写入。在试验箱上通过拨码可以控制PC值的变化,从指令存储器中取出指令并进行数据装载,实验表明,此CPU可以高效地完成测试的指令,并能把计算的结果写入寄存器堆中。

图4 仿真图

图5 CPU验证图

4 结论

经过对取指级的改进,使PC+4在ALU中实现,这样最大化地利用CPU中EXE模块资源。同时通过对时钟上下沿控制,将指令存储器与数据存储器发送地址与读取地址在一个周期内完成,那么译码级与访存级就只需一个周期,这样能大大提高CPU的时钟频率。特别是在执行级中我们设计了一个判决电路,加快数据的交互与传输。最后通过软件仿真和硬件仿真验证,来证实所设计的CPU的正确性,由硬件仿真可以看到所设计的CPU具有实用性。

[1] 刘秋菊, 张光照, 王仲英. 基于MIPS指令集的流水线CPU设计与实现[J]. 实验室研究与探索, 2017, 36(8): 148-152.

[2] D.Sweetman. 看MIPS跑linux——MIPS体系结构剖析(中文版)[M]. 北京: 机械工业出版社, 2008.

[3] M View. MIPS32 Architecture for programmers volume II: the MIPS32 Introduction set[S]. MIPS Technologies Inc, 2005: 10-300.

[4] M View. MIPS32 Architecture for programmers volume I: Introduction to the MIPS32 Architecture[S]. MIPS Technologies Inc, 2005: 7-65.

[5] 阎石. 数字电子技术基础[M]. 北京: 高等教育出版社, 2005.

[6] 秘海晓. 基于FPGA的32位五级流水线CPU的研究与设计[D]. 河北: 河北工业大学, 2012.

[7] 李亚民. 计算机原理与设计[M]. 北京: 清华大学出版社, 2011.

[8] 张震. 基于FPGA的通用型FIR数字滤波器的研究与设计[J]. 软件, 2015, 36(6): 125-128.

[9] 冯建文. 基于有限状态机的多周期CPU实验设计[J]. 实验技术与管理, 2017, 34(7): 127-131.

[10] 焦华. 基础编程的思考方法[J]. 软件, 2018, 39(3): 57-62.

[11] 张玲, 晏伯武. 时序仿真和驱动编写在数字电路实践教学中的应用研究[J]. 软件, 2016, 37(3): 107-109.

[12] 夏宇闻. Verilog数字系统设计教程[M]. 北京: 北京航空航天大学出版社, 2003.

[13] 龙芯中科技术有限公司.LS-CPU-EXB-002CPU设计与体系结构实验指导手册[Z]. 2016.

Design of Multi-cycle CPU Based on MIPS Architecture

LIU Cheng, RONG Jing

(Guangling College of Yangzhou University, Yangzhou 225000)

In order to improve the efficiency of the multi-cycle CPU pipeline, the designation of the sending address is on the rising edge and the reading data is on the falling edge in the data reading of the instruction memory and the data memory, so that the decoding and the access are completed in one cycle. The adder is no longer set separately at the fetch level, and PC+4 is placed in the ALU. Data communication is performed through a large number of multiplexers and data exchange buses. The CPU was designed using Verilog HDL language, and the simulation was implemented on the VIVADO platform. Finally, the verification was performed by the company's LS-CPU-EXB-002 test box. The results showed the effectiveness of the designed multi-cycle CPU.

Pipeline; Verilog HDL; Multi-cycle CPU; LS-CPU-EXB-002 test box

TP332

A

10.3969/j.issn.1003-6970.2018.08.009

扬州大学广陵学院资助项目(JGYB17012)

柳成(1994-),本科生,研究方向为计算机体系结构;荣静(1990-),研究生,扬州大学广陵学院助教,研究方向为信息安全。

本文著录格式:柳成,荣静. 基于MIPS架构的多周期CPU设计[J]. 软件,2018,39(8):40-44