基于FPGA的宽带信号产生和频率测量电路

王丽娜 杨绪森 许冉 徐伟 吴静 石晨鸣

摘 要: 设计基于FPGA的高频信号产生和频率测量电路。系统以FPGA为核心,辅以高速D/A、无源滤波、自动增益控制AGC等模块构成。利用FPGA对标准信号波形进行存储,结合DDS技术,通过高速D/A和无源滤波实现信号的产生。FPGA的计数器、闸门等实体电路实现了等精度测频。利用NIOS实现人机交互功能。实验测试表明,系统输出的三角波、正弦波、方波具有频带宽、频率稳定的特点,测频的相对误差达到10-6。

关键词: FPGA; 模拟电路; 等精度测频; 波形产生; DDS原理; NIOS

中图分类号: TN710.4?34; TP274 文献标识码: A 文章编号: 1004?373X(2018)17?0107?05

Abstract: The high?frequency signal generation and frequency measurement circuits based on FPGA are designed. The system takes FPGA as its core, and is composed of high?speed D/A, passive filter, automatic gain control (AGC) module, etc. FPGA is used to store the standard signal waveform, and combined with DDS technology to realize the signal generation by means of high?speed D/A and passive filter. The counter, strobe and physical circuits of FPGA are used to realize the equal precision frequency measurement. The NIOS is used to realize the human?computer interaction function. The experimental results show that the triangular wave, sine wave and square wave output by the system have the characteristics of wide frequency band and stable frequency, and the relative errors of frequency measurement can reach up to 10-6.

Keywords: FPGA; analog circuit; equal precision frequency measurement; waveform generation; principle of DDS; NIOS

0 引 言

近年来,DDS技术广泛应用于雷达系统、数字通信、电子测量等设备中。传统的方法采用单片机等处理器来控制DDS芯片,使其输出对应的波形信号数据。这种处理器+DDS模块的组合形式使得系统的复杂度高,成本也较高。由于FPGA在处理数字信号方面具有优势[1?5],且能够通过编程的形式在其内部构建软核实现单片机的控制功能。同时,根据DDS原理,在内部构建相位累加器和波形存储器实体电路,结合DAC、滤波电路等实现DDS芯片的功能,单个FPGA可以代替单片机+DDS芯片的组合,实现波形信号产生。

在电子设计过程中,测频是最常用的技术之一[6?7]。目前的数字频率计主要是通过单片机与CPLD的组合形式对信号进行处理分析,这种方法增加了器件的数量,不利于仪器的高集成度。利用FPGA在其内部应用等精度方法测量信号,可以有效提高测量精度[8?9]。被测信号通过前级AGC(自动增益控制)电路、宽带放大电路、高速比较电路处理转换成FPGA可处理的方波信号,经FPGA的同步闸门、计数器、触发器、选择器等实体电路对输入信号和高精度标准信号进行等精度计数,并处理显示。采用FPGA代替单片机和CPLD的组合,可以实现频率测量。

鉴于波形信号产生和频率测量是电子系统中最常用的两项功能,目前几乎没有集成这两项功能的系统。由于大部分电子设计工程的场地不固定,设计人员希望能够在各种场地下进行电子设计实验。因此,本文使用FPGA芯片将信号发生器和频率计功能集成在一起,在提高资源利用率和系统集成度的同时,也使得系统更高效,可以满足大部分情况下的实验需要,应用前景广阔[10?12]。

1 系统原理

1.1 信号产生原理

直接数字式频率合成器(DDS)的基本原理就是事先存储一个周期波形信号的幅度值(如正弦表),再按照预设的每个频率,分别以不同的速率(在正弦表中取值的步进)发送当前周期的波形信号,进而把离散的幅度值合成波形信号。DDS原理图如图1所示。

图1中:[K]是通过软核处理器控制的相位累加器步进值,根据不同的步进值输出不同的频率;[fs]是通过IP核PLL模块输出的100 MHz时钟,作为采样时钟。设累加器的数据位宽为[N]位,那么当相位改变360°时,需要累加[2N]次。

本设计基于FPGA,通过硬件描述语言设计相位累加模块和波形存储模块,可以输出多种波形并任意改变频率。设计的采样频率设定为100 MHz,相位累加器设计为32位,则频率理论分辨率为0.023 Hz。

1.2 频率测量原理

等精度测量法是用系统时钟产生一个标准信号,然后预置一个闸门时间,在预置闸门开启后,不断检测输入信号的上升沿,上升沿到来瞬间,开启实际闸门,待预置闸门下降沿到来后不断检测输入信号的下降沿,下降沿到来瞬间关闭实际闸门。这样整数倍的被测信号周期就是实际闸门,避免了被测信号产生的±1周期误差。被测信号频率可通过实际闸门时间内对标准信号和被测信号计数来计算得出。

2 系统硬件设计

2.1 FPGA设计

FPGA具有并行运算的能力,属于一种半定制专用集成电路,能够灵活地应用在各种需要快速响应和同时处理多路信号的场合。并且FPGA系统配置了NiosⅡ处理器,能够通过硬件描述语言在内部搭建实体电路模拟单片机的功能,实现按键控制、屏幕驱动等功能。

FPGA内部模块设计如图3所示。其中NiosⅡ处理器负责处理按键逻辑控制,实现波形选择及其他功能设置,同时驱动LCD显示屏,显示相关系统参数及测量值。

以正弦波信号产生模块为例,实体电路如图4所示。波形产生主要由相位累加器和波形存储器两个模块完成,而波形存储器中的数据不同可以产生不同的波形。构成实体包括相位累加器inst9和波形存储器inst10:输入端口RESET、频率控制字[K]和时钟输入CLK;输出端口:波形数据sin。

相位累加器根据输入的频率控制字数值不同,进行步进值不等的数据累加并输出。波形存储器根据相位累加器输出的值输出对应的波形幅值,这些连续输出的幅值点便构成了特定的波形。

频率测量实体电路如图5所示。图5中,等精度测频功能由触发器、计数器模块来完成。构成实体包括:计数器inst15和inst18、定时器inst16、D触发器inst17。输入端口包括:基准系统时钟CLK、被测信号Fin、清零信号CLR。输出端口包括:测量数据字节输出CLK_COUNT和FIN_COUNT。

实体计数器inst15对被测信号进行计数,实体计数器inst18对频率为100 MHz的基准时钟计数,但计数的开始时间受闸门en控制。定时器inst16对100 MHz系统时钟信号进行计数,得到周期1 s的预置闸门信号,预置闸门有效时,并不立即开启两计数器,而是通过D触发器产生与被测信号严格同步的实际闸门[q],当实际闸门[q]有效时,两个计数器才开始计数。两计数器的计数值都为4 B,直接将计数值发送给Nios处理器。

2.2 模拟电路设计

本设计主体电路结构如图6所示,主要分为波形产生功能和频率测量功能。波形产生功能包括高速D/A模块和低通滤波器;频率测量功能包括AGC电路模块和高速比较器模块。

模拟电路选用的芯片均为高速芯片,提高了系统整体带宽。

AGC电路的原理如图7所示。信号经过程控放大器后不断进行检测,根据结果产生一个电压值控制程控放大器的增益,使程控放大器输出的信号无限接近限定值。整个电路形成闭环反馈。高速缓冲放大器与后级电路进行阻抗匹配,从而保持系统稳定性。

被测信号经过前级AGC电路调理后幅值已符合要求,而波形有可能是非方波信号,从而使得无法被FPGA正确测量,所以通过高速比较器将前级输出信号整形成方波信号,然后再输入至FPGA进行处理测量。

高速比较电路采用滞回比较电路原理,能够使系统稳定,不会因受干扰而造成波形跳变。

无源滤波由电容、电感和电阻共同组成,通过公式计算及实际调试,使其符合性能要求。其中截止频率设定为40 MHz。

3 仿真与调试

3.1 波形信号产生

以正弦波信号产生为例,对波形信号产生功能进行仿真,采用逻辑分析仪采集FPGA端口输出的数据,得到如图8所示的数据图。

由此数据图能够清楚地判断出端口输出的数据是符合要求的。将图8中输出的并行数据输入至D/A转换模块就可以得到如图9所示的连续正弦波信号。

图9中,测试所用D/A转换模块为8位并行数据接口,并行数据有利于高速数据的快速转换,提高系统整体性能。

3.2 频率测量

频率测量如图10所示,通过高性能信号发生器输入100 kHz、幅值为1 V的正弦波信号,同时用高性能频率计为参考,观察本设计的测频数值。

图10中,输入信号为100 kHz,高性能频率计显示值为99.999 996 647 kHz。LCD屏显示频率测量值如图11所示,显示屏上的数值为99.999 716 kHz。

4 测试与分析

FPGA使用标准的50 MHz晶振,对应不同模块,使用IP核进行倍频至100 MHz作为系统时钟,分功能进行性能指标测试。

测试仪器:RIGOL DP832电压源、RIGOL DG4102信号源和频率计、RIGOL DS2202示波器。

4.1 波形信号产生功能测试

通过按键设置不同波形、频率、幅值的信号,以RIGOL DG4102频率计的测定值为标准值进行误差分析。正弦波和方波产生的频率测试数据如表1所示。

4.2 频率测量功能测试

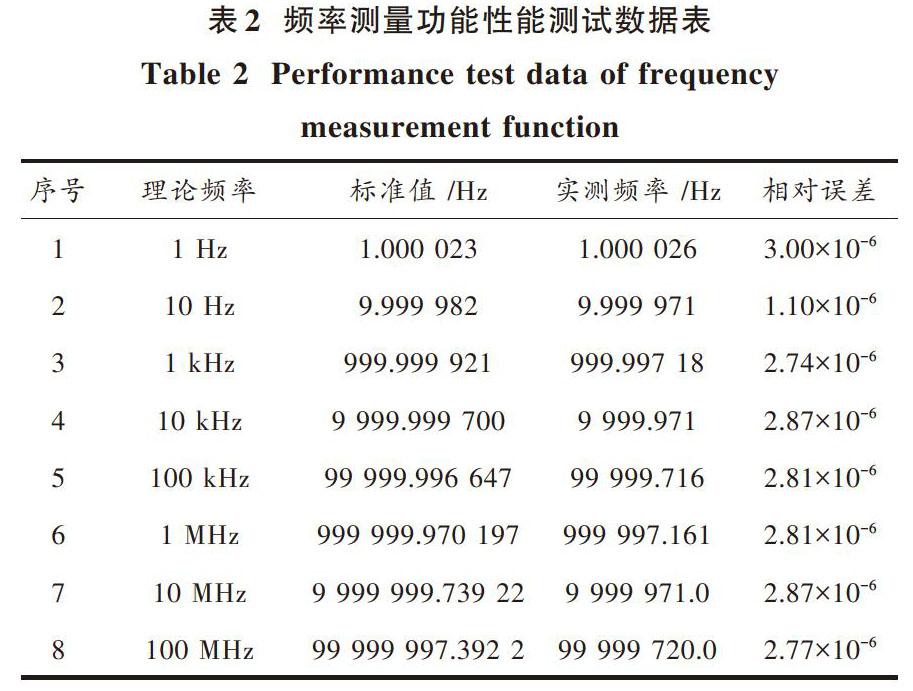

对于频率测量功能采用高性能信号发生器输出不同波形、频率的信号进行测量,以RIGOL DG4102频率计的测定值为标准值进行误差分析。测试结果如表2所示。

5 结 论

本文主要设计了基于FPGA的宽带信号产生和频率测量电路。通过测试数据表明:任意波形信号产生功能能够产生频率1 Hz~20 MHz、幅值为50 mV~10 V的正弦波、方波等多种波形;频率测量功能能够实现对幅值10 mV~1 V、频率1 Hz~100 MHz的不同波形的測量,系统总体性能较高。

参考文献

[1] 韩朝辉,孟令军,邹坤.基于FPGA的多速率信号发送器的设计[J].计算机测量与控制,2016,24(2):317?320.

HAN Zhaohui, MENG Lingjun, ZOU Kun. Design of multi rate signal transmitter based on FPGA [J]. Computer measurement & control, 2016, 24(2): 317?320.

[2] 李嘉楠,谢雪松,张小玲,等.基于DDS技术的多路电气隔离程控信号源[J].电子技术应用,2016,42(2):53?56.

LI Jianan, XIE Xuesong, ZHANG Xiaoling, et al. A programmable multi?routing electrical isolated signal generation system based on DDS technology [J]. Application of electronic technique, 2016, 42(2): 53?56.

[3] 张艳.基于FPGA低频信号发生及分析仪设计[J].自动化与仪器仪表,2016(6):40?41.

ZHANG Yan. Design of frequency signal generation and analysis system based on the FPGA [J]. Automation & instrumentation, 2016(6): 40?41.

[4] 张霞.基于FPGA的正弦信号测量系统[J].电子设计工程,2015,23(24):93?95.

ZHANG Xia. Sine signal measurement system based on FPGA [J]. Electronic design engineering, 2015, 23(24): 93?95.

[5] 田毅,范毓洋,李哲玮,等.基于FPGA的亚稳態参数测量方法[J].微电子学与计算机,2016,33(10):46?49.

TIAN Yi, FAN Yuyang, LI Zhewei, et al. Metastable parameter measurement method based on FPGA [J]. Microelectronics & computer, 2016, 33(10): 46?49.

[6] 吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2010.

WU Houhang. Play FPGA [M]. Beijing: Beijing University of Aeronautics and Astronautics Press, 2010.

[7] 赛尔吉欧·佛朗哥.基于运算放大器和模拟集成电路的电路设计[M].西安:西安交通大学出版社,2009.

FRANCO S. Design with operational amplifiers and analog integra?ted circuits [M]. Xian: Xian Jiaotong University Press, 2009.

[8] 黎山峰,杨雷,孙建军.基于NiosⅡ的FPGA频率计设计与实现[J].仪表技术与传感器,2016(8):105?108.

LI Shanfeng, YANG Lei, SUN Jianjun. Design and implementation of FPGA frequency meter based on Nios II [J]. Instrument technique and sensor, 2016(8): 105?108.

[9] 方易圆,邓琛.等精度频率计的FPGA设计[J].测控技术,2012,31(10):1?4.

FANG Yiyuan, DENG Chen. Design of equal precision frequency meter based on FPGA [J]. Measurement & control technology, 2012, 31(10): 1?4.

[10] ZHANG W H, BASKARAN R, TUMER K L. Effect of cubic nonlinearity on auto?parametrically amplified resonant MEMS mass sensor [J]. Sensors and actuators A, 2002, 102(1/2): 139?150.

[11] 吴瑕杰,宋文胜,冯晓云.一种在线计算多模式空间矢量调制算法及其FPGA实现[J].电工技术学报,2016,31(18):124?133.

WU Xiajie, SONG Wensheng, FENG Xiaoyun. An on?line calculation multi?mode SVPWM algorithm and implementation based on FPGA [J]. Transactions of China electrotechnical society, 2016, 31(18): 124?133.

[12] 杨鸿武,张策,陆晓燕,等.一种改进式TAC的高精度时间间隔测量系统的实现[J].计算机测量与控制,2015,23(12):4008?4012.

YANG Hongwu, ZHANG Ce, LU Xiaoyan, et al. Implementation of high precision time interval measurement system based on an improved time?amplitude converter [J]. Computer measurement & control, 2015, 23(12): 4008?4012.