基于Offload和FPGA的网络传输设计与实现

薛 镭,贺亚龙

(中国船舶重工集团公司第七一五研究所,杭州 310023)

0 引言

目前主流的操作系统网络协议栈基本上都使用TCP/IP协议栈。经典的TCP/IP参考模型从上至下分为4个层次:应用层、传输层、网络互联层和主机到网络层[1]。在以太网通信中,最大传输单元(Maximum Transmission Unit,MTU)规定了经过网络层封装的数据包的最大长度。当 IP层需要传送的数据超过 MTU值时,IP层需要对该数据包进行分片,使每一片的长度小于或等于MTU值;在TCP通信建立连接时,取两端提供的最大报文长度(Maximum Segment Size,MSS)的最小值作为会话的MSS值,由于TCP分段有MSS值的限制,通常情况下TCP数据经过IP层封装后的长度不会大于MTU。因此,在一般情况下,TCP数据包不会进行IP分片。如果出现网络数据包太小的情况,操作系统网络协议栈及应用软件对网络数据的解析计算会消耗大量的CPU时间,导致网络数据传输效率急剧下降,甚至出现丢包。为了解决这些问题,本文着重研究了一种基于offload和FPGA的网络数据采集方法,将网络数据的解析工作放到FPGA中进行,然后通过PCIe总线高速传输到PC机应用程序中处理。

PCIe总线可以提供更大的总线带宽,PCIe V3.0支持的最高总线频率为4 GHz,远高于PCI-X总线支持的最高总线频率。PCIe总线支持虚通路(Virtual Channel,VC)技术,优先级不同的数据报文可以使用不同的虚通路,而每一路虚通路可以独立设置缓冲,从而相对合理地解决了数据传送过程中存在的服务质量问题[2]。

1 设计原理

本文描述的offload主要是指将原本在网络协议栈中进行的IP分片、TCP分段、重组、checksum校验等操作转移到FPGA中进行,以降低系统CPU负荷、提高处理性能。

1.1 发送模式

TSO(TCP Segmentation Offload)就是把TCP分段的过程转移到 FPGA中进行,直接把不超过滑动窗口大小的payload下传给协议栈,而由FPGA进行TCP分段操作,并执行checksum计算和包头、帧头的生成工作。

UFO(UDP Fragmentation Offload)是一种专门针对UDP协议的特性,主要机制就是将IP分片的过程转移到 FPGA中进行,用户层可以发送任意大小的UDP数据包(UDP数据包总长度最大不超过64k),而不需要协议栈进行任何分片操作。

1.2 接收模式

LRO(Large Receive Offload)在FPGA层面上接收到多个TCP数据包,并将其聚合成一个大的数据包,然后上传给应用程序处理。这样就可以减少CPU处理的开销,提高系统接收TCP数据的能力和效率。

RSS(Receive Side Scaling)可以将不同的网络数据流分成不同的队列,再将这些队列分配到多个 CPU核心上进行处理,从而将负荷分散,充分利用多核处理器的能力,提高数据接收的能力和效率。

1.3 总体功能与结构

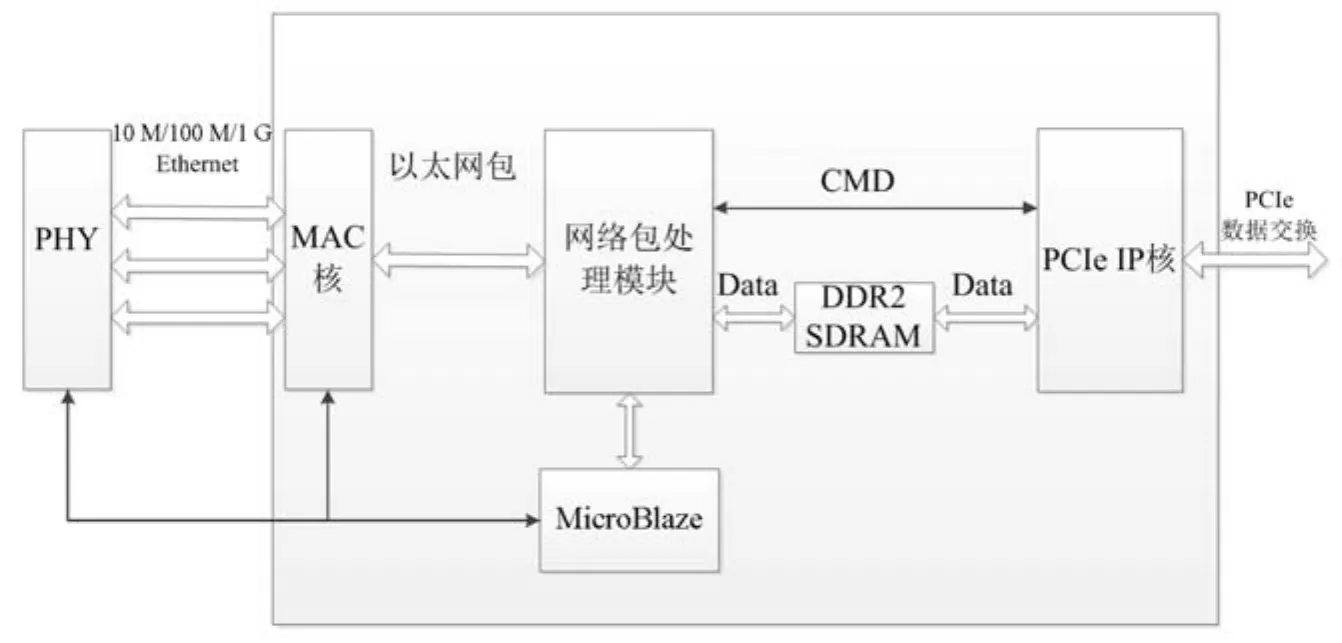

网络数据经过FPGA主控处理后,通过PCIe总线传递给PC主机应用程序处理,FPGA网卡传输功能框架如图1所示。

图1 网卡功能框架图

2 硬件设计

2.1 芯片选型

网络电路由PHY芯片及周围电路组成,PHY芯片选用Marvel公司的88e1111型号,该芯片的特性为:支持GMII、RGMII和MII等接口;具备4个GMII时钟模式;支持自适应功能;可选择2.5 V和1.0 V输入输出电压。

FPGA芯片采用Xilinx公司Virtex-5系列芯片,包含多种硬 IP系统级模块,包括强大的 36 kb Block RAM/FIFO、第二代25×18 DSP Slice、带有内置数控阻抗的SelectIO技术、ChipSync源同步接口模块、系统监视功能、带有集成数字时钟管理器(Digital Clock Manager,DCM)和锁相环(Phase Locked Loop,PLL)时钟发生器的增强型时钟管理模块以及高级配置选项[3]。

2.2 FPGA程序设计

FPGA程序的组成框图如图2所示。FPGA程序主要实现如下功能:1)集成3个MAC核,实现与PHY芯片的通信以及以太网包的收发;2)根据 IP地址和PORT、数据类型进行网络数据分包,并加上时间戳信息;3)使用MircroBlaze配置IP/PORT/MAC地址等参数;4)提供 PCIe接口接入 PC机操作系统,处理与PC机的PCIe数据交换。

图2 FPGA程序的组成框图

2.3 工作流程

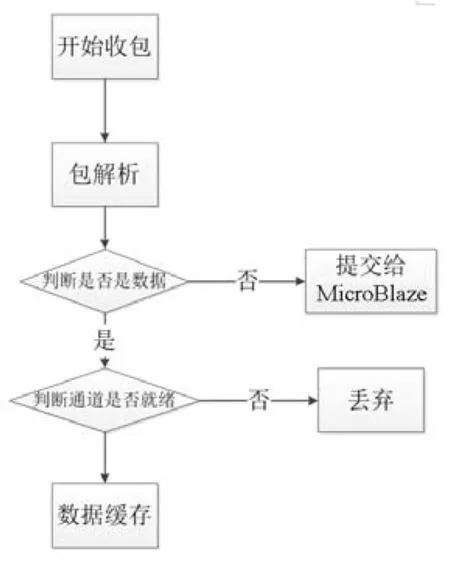

本程序对以太网包的处理采用嵌入式操作系统+逻辑模块的结构,网络包处理模块采用片内逻辑资源设计,实现对以太网包 1~3层的解析和数据分发,收包流程如图3所示。

图3 网络包处理模块收包流程

按照上述流程,大部分以太网包由该模块处理,或提交主机、或直接丢弃,其他少量命令/状态包则提交给 MicroBlaze进一步处理,如命令 UDP包、ARP包、ICMP包、TCP包和其他未识别的以太网包等,这样既确保了对各通道UDP数据包的线速处理,同时利用MicroBlaze内部的TCP/IP协议栈实现复杂网络处理能力。

MicroBlaze除了解析命令UDP包外,还实现对返回给客户端的状态信息的打包,以及FPGA片内外寄存器空间的配置和状态收集。

3 软件设计

3.1 PCIe驱动程序设计

PCIe总线支持3个独立的物理地址空间:存储器空间、IO空间和配置空间[4]。每个PCIe设备都有一个配置空间,配置空间采用ID寻址方法,用总线号、设备号、功能号和寄存器号来唯一标识一个配置空间[5-6]。

FPGA的PCIe IP核在生成时,会生成相应的PCIe总线号、设备号等ID[7-8],驱动程序通过设备ID和厂商ID对设备链进行扫描,进行匹配。驱动与设备匹配之后,驱动程序中申请内存缓冲空间,提供DMA读写接口将数据从PCIe总线传输到PC机应用程序缓冲空间。

3.2 FPGA程序设计

FPGA程序实现了数据包的过滤,需要完成如下功能。

3.2.1 FPGA过滤规则配置

FPGA已从数字电路设计上实现了通道选择,缓存大小设置,ARP协议、ICMP协议、IGMP协议、IP协议、UDP协议、TCP协议等网络数据包过滤配置功能。应用程序需要在初始化阶段完成过滤规则的参数配置。

3.2.2 数据缓冲队列

初始化缓冲队列,网络数据包经过FPGA过滤之后,通过驱动程序传输进入内存不同协议的数据缓冲队列。

3.2.3 数据解析

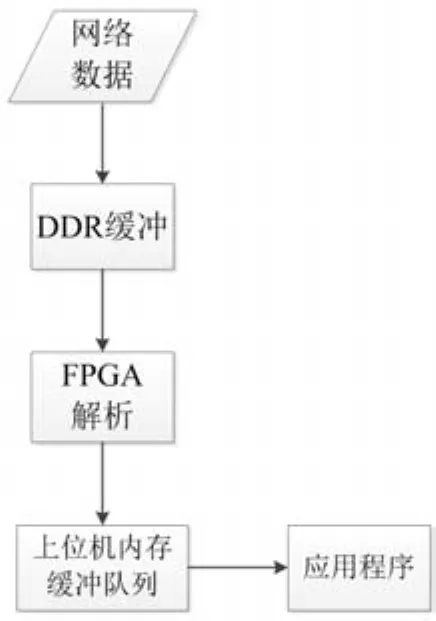

根据网络协议规范,从各种数据缓冲队列中取出需要的数据提交给应用程序处理,应用程序工作流程如图4所示。

图4 应用程序工作流程

4 试验验证

使用本文设计的基于offload的FPGA实现网卡功能,进行网络数据传输,并与普通网卡进行对比,试验数据如表1所示。

表1 网络数据传输比对

测试结果显示:基于offload的FPGA实现网络数据传输的网速提升明显、没有丢包、网速较稳定无波动情形。

5 结束语

本文设计了基于offload的FPGA实现网络数据传输,其充分运用了FPGA可编程的灵活性,具有结构简单、易于控制、小型化、低功耗等特点。相关验证测试结果显示:该设计传输网络数据正确、工作稳定可靠、传输速率提高20%以上、即使PC端应用程序出现卡顿也无丢包、对实时数据的处理与存储效率有所提升,具有实际工程应用价值。

同时,结合 FPGA丰富的资源及并行处理能力,后续可以考虑优化应用程序软件架构,进一步提高网络数据传输与处理能力。