基于数字信道化的侦察干扰一体化技术

王明君

(中国电子科技集团公司第五十一研究所,上海 201802)

0 引 言

随着无线电装备的广泛应用,战场电磁环境日渐复杂;在雷达对抗领域,我方装备将可能同时被不同频段、多部、多体制雷达照射。这就要求雷达对抗设备具备大带宽,能够适应复杂电磁环境,从众多辐射源中分选出高威胁信号,具备同时干扰多部、多体制雷达的能力[1]。这将极大地增加干扰设备的复杂程度及设备量。在弹载、机载等运用场合,对任务载荷的体积重量又有严格控制。因此,雷达对抗设备的全能型、轻小型化将是大势所趋。

微电子领域的发展,使得数字信号处理器(如现场可编程门阵列(FPGA)、数字信号处理器(DSP)、中央处理器(CPU)、图形处理器(GPU))的处理能力得到大幅提升;数字信号处理算法的优化使得运算效率更高效,对处理器要求更易实现。基于数字系统高集成、高可靠及灵活等特点,数字化是雷达对抗设备实现全能型、轻小型化的有效途径。

本文设计了基于高速模/数(A/D)转换、数/模(D/A)转换、四倍数据率(QDR)II、Altera FPGA及TI公司的DSP雷达侦察干扰一体化处理单元。基于高效数字信道化结构,处理单元实现了对宽带信号的实时侦收、存储及高逼真干扰信号产生。

1 设计方案

1.1 硬件架构设计

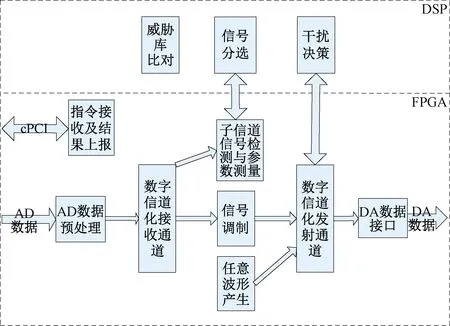

上位机通过紧凑型外设部件互连标准(cPCI)总线下发控制指令并接收处理单元的上报数据;处理单元通过高速模/数转换器(ADC)对宽带雷达信号进行中频采样,完成信号数字化;大规模FPGA实现信号侦收的预处理算法及干扰算法;DSP接收FPGA的预处理结果进行信号分选;数字化干扰信号经过高速数/模转换器(DAC)转换为模拟信号,作为干扰激励输出。为提高系统集成度,本文在一块cPCI标准6U板卡上实现2路瞬时带宽2 GHz的侦察干扰一体化处理通道。处理单元组成框图如图1所示。

1.2 高速ADC、DAC的选择

高速ADC、DAC作为处理单元的对外窗口,完成宽带数字侦收的模数变换及宽带干扰的数模转换。为满足2 GHz瞬时处理带宽要求,需要ADC和DAC采样率超过4 GSPS,为方便系统中变频通道的设计实现,需要留有一定的过渡带。综合目前的器件水平及后续处理的方便,本设计选用

图1 处理单元组成框图

4.8 GSPS采样率。中频输入输出范围选择0.2~2.2 GHz。

目前采样率能达到4.8 GSPS的ADC,主要有E2V公司的EV10AQ190和TI公司的ADC08DJ3200,从器件使用难度及扩展性等方面因素考虑,本设计选择EV10AQ190作为处理单元的模数转换芯片。

EV10AQ190为E2V推出的最高采样率5 GSPS,量化位数10 bit的高速ADC。芯片内部采用4个1.25 GSPS/10 bit的ADC核,通过交叉采样实现5 GSPS的等效采样率。内部结构图如图2所示。

目前采样率能达到4.8 GSPS的DAC主要有EUVIS公司的MD662和TI公司的DAC38RF85,综合考虑芯片的性能及可升级性,选取MD662作为系统的数模转换核心芯片。

MD662是EUVIS公司基于MD652 推出的采样率可达8 GSPS的12 bit高速DAC;芯片内部自带4∶1的MUX电路,在4.8 GSPS采样率下,数据端口输入率只需要4.8 G/4=1.2 G,目前FPGA的LVDS接口可以适应这一速率要求。MD662 内部结构图如图3所示。

图3 MD662内部结构图

1.3 处理器的选择

处理单元采用FPGA和DSP作为处理器。FPGA 作为处理单元的主处理器,要完成侦察预处理、干扰信号产生等算法,且FPGA和高速ADC、DAC都要有高速数据交换,对FPGA的IO口速度也有较高要求。综合考虑后,每个处理通道选择1片Altera公司的StratixⅣ系列高端FPGA——EP4SE530H40I3作为信号处理的主处理器芯片,负责侦察、干扰算法实现。选用TI公司的高端定点DSP芯片TMS320C6455BZTZ作为模块协处理器,负责信号分选及干扰决策。采用1片Altera公司CycloneⅢ系列低端FPGA——EP3C55F484I7作为处理单元的通信及控制处理器,负责和上位机通信并完成对处理单元各部分电路的控制。

1.4 数据存储芯片的选择

信号侦察过程中,FPGA对信号进行预处理及DSP进行信号分选工作时都需要对处理数据进行缓存,本设计采用DDR2芯片——MT47H64M16HR-3IT作为FPGA和DSP的数据缓冲器。

干扰信号产生过程中,处理单元需要对原始中频信号进行缓存并调制输出。每一个处理通道在4.8 GSPS/10 bit采样率情况下,将产生48 Gbit/s的原始波形文件。要将如此大带宽的数据实时存储,对存储器的带宽要求较高。本设计采用2片Cypress公司的QDRⅡ芯片——CY7C1565KV18-500BZI进行位扩展以实现宽带信号的实时存储。每片CY7C1565KV18具有最高36×1 Gbit/s的读写速度,2片采用位扩展可以实现72 Gbit/s的读写速度,满足系统48 Gbit/s读写速度的需求。

2 软件实现

2.1 软件架构设计

一体化处理单元主要完成宽带雷达信号的实时侦收及干扰功能;侦收功能主要完成对0.2~2.2 GHz的雷达信号进行数字信道化接收、上报侦收结果,并引导干扰功能对指定雷达进行高逼真干扰。干扰功能主要在引导下对指定目标进行高逼真欺骗干扰或非相参压制性干扰。

图4 软件功能划分

一体化处理单元各功能主要在FPGA及DSP中实现。功能划分如图4所示。DSP中主要完成基于PDW的雷达信号分选及威胁库比对,并根据指令做出干扰决策。FPGA中主要完成基于数字信道化的侦察干扰一体化算法实现,具体算法实现将重点介绍。

2.2 侦察干扰一体化收发通道设计

运用基于多相滤波的数字信道化技术,采用复信号偶型排列结构[2],将处理单元的频带划分为D个子信道,子信道带宽为2π/D,如图5所示。信道化收发通道算法流程如图6所示。

图5 复信号偶型结构信道划分

图6 数字信道化侦收干扰一体化算法流程

2.3 算法仿真

用Matlab进行算法仿真,首先利用Kaiser窗截取理想低通滤波器[3],获得多相滤波器的原型系数。原型滤波器频响如图7所示。

图7 原型滤波器频响

根据图6的算法流程建立Matlab仿真模型,输入数据率4.8 GSPS(ADC、DAC采样率4.8 GHz);将第一奈奎斯特区划分为32个通道,如图8所示。

图8 信道划分

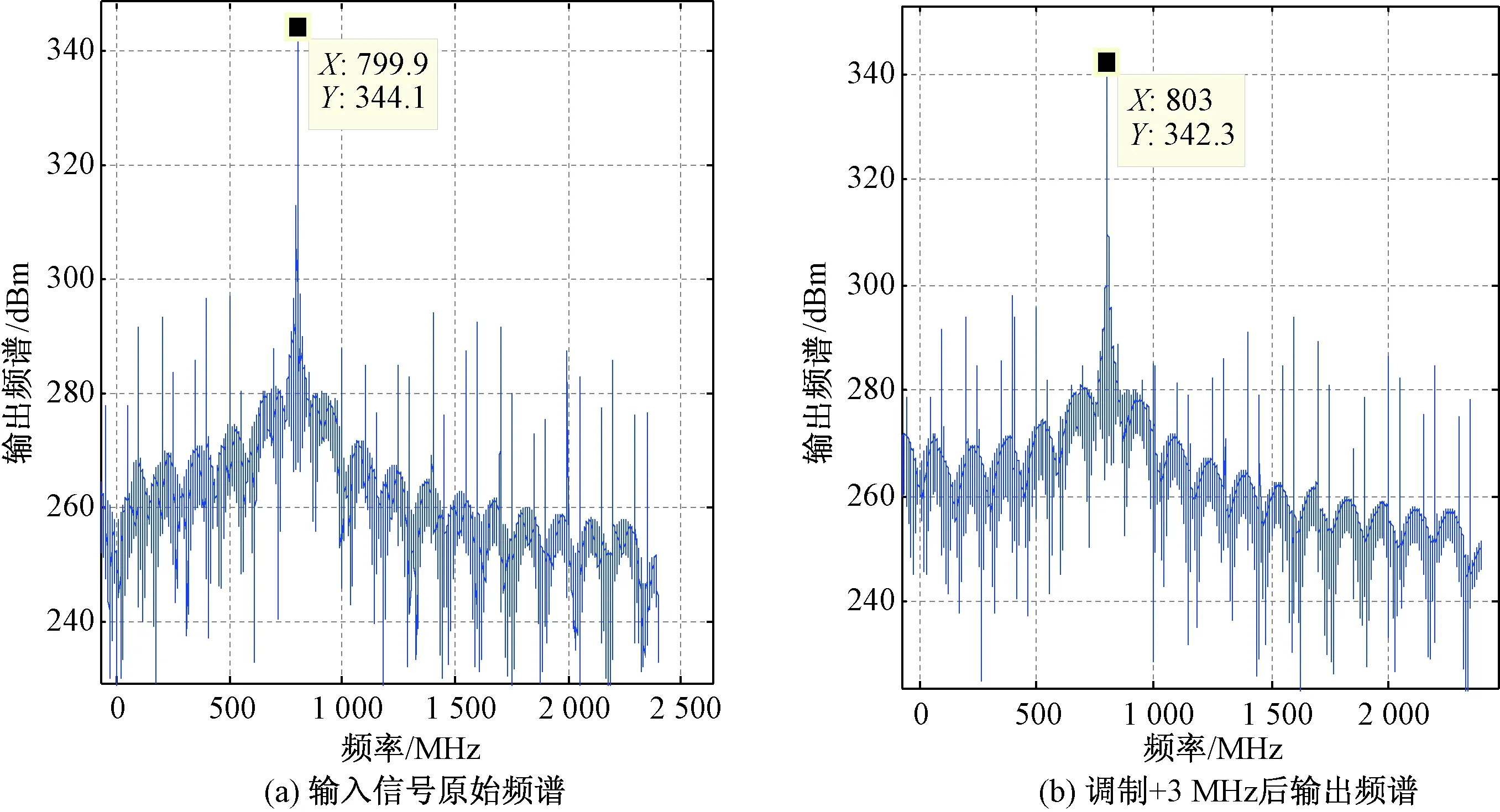

为系统模型输入800 MHz信号,频谱如图9(a)所示;将调制信号频率设置为+3 MHz,输出频谱如图9(b)所示。

图9 调制前后信号频谱

通过仿真结果可以看出,算法达到了侦收干扰共用处理通道的效果,基于数字信道化的侦收发射通道可以应用在侦察干扰一体化处理单元中。

2.4算法FPGA实现

数字信道化收发通道在EP4S530中实现,通道接收采样率4.8 GSPS的10 bit ADC数据,通过降速处理后变为150 MSPS×32路的低速数据。将低速数据送入数字信道化接收模块,通过下变频处理后变为32路带宽75 MHz的基带信号。信号检测模块对基带信号进行时频检测并将结果形成脉冲描述字(PDW)上报DSP进行分选。引导干扰时,还需要将检测出有信号的信道的波形数据进行相应的调制[4],最后送入信道化发射通道,进行干扰合成输出。

3 系统验证及性能测试

处理单元实物图如图10所示。

图10 处理单元实物图

信号源输入0.2~2.2 GHz信号作为处理单元的输入信号,通过侦收上报后系统下发干扰指令,处理单元进行引导并干扰。输入载频频率800 MHz,脉宽100 μs,重复周期1 ms的脉冲调制信号作为输入信号,图11为未进行频率调制的输出频谱。

图11 无调制输出频谱

图12为调制3 MHz后的输出信号频谱。

图12 调制3 MHz后输出频谱

4 结束语

本文介绍了一种基于数字信道化的侦察干扰一体化技术,通过硬件上侦察干扰共用采集通道,软件上共用信道化下变频模块,改变了以往侦察和干扰分置带来的设备量较大等弊端,提高了设备的小型化水平,更加适应小型平台的应用场合。