基于DSP28335+IR2110芯片的移相全桥驱动电路设计1

贺根华,祁承超,柳 鑫

(空军预警学院 信息对抗系,湖北 武汉 430019)

目前,随着电力电子技术的进步,高频开关电源在市场的占有比重越来越大.传统的模拟电路在高频时容易受到干扰,为了确保开关电源能够稳定可持续的工作,一般采用数字化进行实现.本文通过TI公司TMS320F28335芯片来产生可控制的移相角.同时,功率开关器件一般采用直接驱动和间隔隔离驱动两种驱动方式[1-3].IR2110是一种理想驱动装置.该芯片具有光耦隔离(体积小)和电磁隔离(速度快)的等优点,是中小功率驱动装置的首选.

本文以TMS320F28335和IR2110芯片为基础,设计了基于DSP28335+IR2110芯片的移相全桥电路驱动.该电路简化了模拟驱动控制电路的复杂性,实现了移相全桥电路数字化控制.

1 IR2110内部结构及管脚功能介绍

1.1 IR2110内部结构

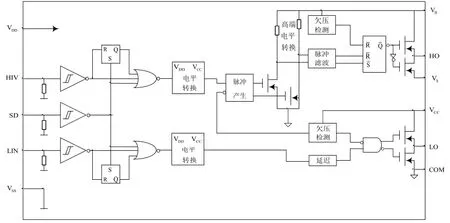

IR2110内部结构如图1所示,主要由三部分组成:逻辑输入、电平平移和输出保护.IR2110的逻辑电源电压工作范围为5~20 V,具有两路独立的高端和低端输出通道.悬浮电源采用自举电路,其高端可承受500V的工作电压,在15V工作下,功耗仅116mW.一个IR2110芯片通过高端和低端输出通道可同时驱动同一桥臂的上、下两个开关器件,从而减小了控制器件的体积和电源数目,降低了成本,提高了系统的可靠性[4].

图1 IR2110内部结构

1.2 管脚功能介绍

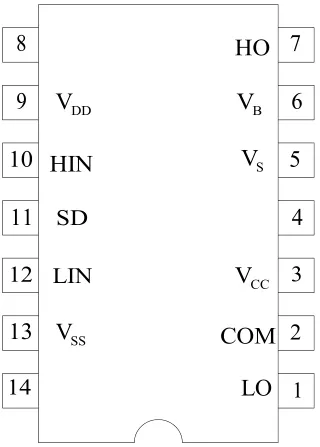

IR2110引脚图如图2所示.

1脚为低端逻辑输出(LO);

2脚为低端电源公共端(COM);

7脚为高端逻辑输出(HO);

3脚是低端电源电压(Vcc);

5脚是高端浮置电源公共端(VS);

6脚是高端浮置电源电压(VB);

9脚是逻辑电路电源电压(VDD);

10脚是高端逻辑输入(HIN);

11脚是输入关闭端(SD);

13脚是逻辑电路接地端(Vss);

14脚是低端逻辑输入(LIN);

4、8、脚置空.

图2 IR2110引脚图

2 IR2110驱动电路设计

2.1 IR2110驱动电路的工作原理

IR2110驱动电路如图3所示,其中VDD为逻辑电路电源,电压范围为5V~20V,Vcc为功率管门极驱动电源,电压范围为10V~20V.图3中,当开关管S2导通,则VS的电位被拉低,Vcc通过自举二极管D2、自举电容C2、开关管S2组成闭合回路给C2充电,使得自举电容C2形成一个悬浮电源,以确保在S2关断及S1导通时,自举电容C2储存的能量来驱动S1管的栅极,从而实现自举式驱动[5].

在IR2110驱动电路中,自举电容的选择非常重要,其取值大小跟开关频率有关.通常情况下开关频率越高,自举电容的取值越小,自举电容选择的是钽电容.同时自举二极管的选择也非常重要,它的主要作用是阻断直流干线上的电压,一般选择漏电流较小的快回复二极管[6].

2.2 驱动电路的参数设计

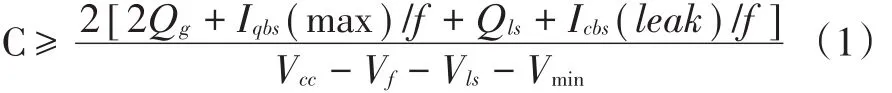

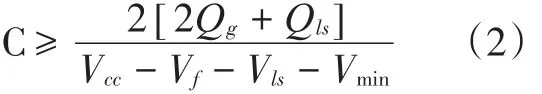

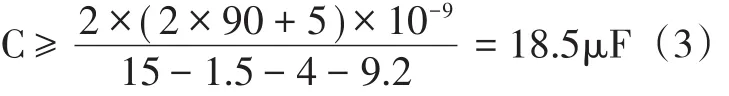

自举电容[7-8]的计算公式如下:

其中参数Vcc为提供的电源电压,本文选择直流15 V电压;Vls为下半桥MOSFET导通时的栅源阈值电压,一般为3~5V,本文取Vls为3V;Vmin是VB和VS之间的最小电压(可由IR2110手册中查到,Vbsuvmin=9.3V);Vf为自举二极管的正向导通压降,一般为0.7V;Qg为门极电荷通常为70nC(可由MOSFET手册中查到);Iqbs(max)为最大VBS静态电流230μA(可由2110手册中查到);Icbs(leak)为自举电容漏电流;Qls为转移电荷 =5 n C(5 0 0 V)=2 0 n C(1200V);f为开关频率,本文开关频率为50kHz.由于开关频率过大,公式(1)可简化为公式(2)

将上述参数代入公式(2)中得:

本实验C1和C3选取2.2μF的滤波电容,自举电容C2选取22μF,36V的胆电容,二极管D1和D3选用快恢复二极管FR157,为防止栅极电流di dt过大损坏开关管,通常选取十几欧的限流电阻,取R1和R2为10Ω.

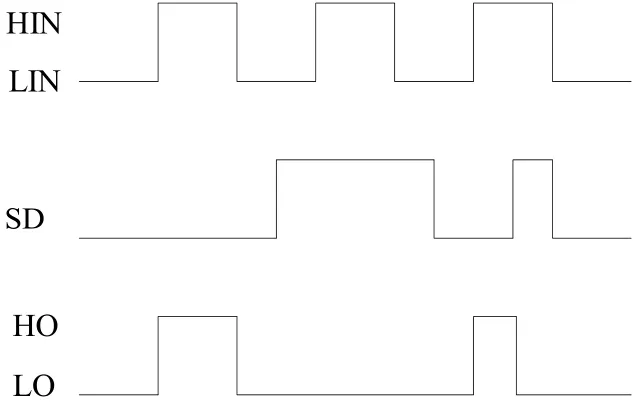

2.3 保护电路设计

IR2110芯片SD管脚具有过流保护功能,当LO和HO脚输出一对互补的信号驱动上下两个功率管时,如发生异常情况,上下两只管子同时导通,发生直通现象,其管电流瞬间增大,与设定的值进行比较,若大于设定值时,比较器LM139输出高电平送给IR2110芯片SD管脚.如图4所示,高电平的SD信号使得LO和HO管脚输出信号立即变为低电平,立即关断上下两个功率开关管.

图4 HO、LO、SD的输入时序

3 TMS320F28335移相波形的产生[9-16]

3.1 各寄存器的配置

1)输出PWM端口配置:

DSP的端口具有多功能引脚,为将端口配置成PWM功能引脚,首先需要对DSP的端口进行配置,.本论文采用两路EPWM1和EPWM2来产生四路驱动信号,EPWM1A、EPWM1B、EPWM2A、EPWM2B分别对应EPWM1、EPWM2、EPWM3、EPWM4.EPWM1、EPWM2、EPWM3、EPWM4对应的端口分别为 GPIO0、GPIO1、GPIO2、3.

InitEPwmGpio()部分代码:

EDIS;

GpioCtrlRegs.GPAPUD.bit.GPIO0=0;

GpioCtrlRegs.GPAPUD.bit.GPIO1=0;

GpioCtrlRegs.GPAPUD.bit.GPIO2=0;

GpioCtrlRegs.GPAPUD.bit.GPIO3=0;

EDIS;

2)PWM波的频率配置:

PWM波的频率设置是通过设置时基周期寄存器(TBPRD)来完成的,由下面公式计算:

其中,f是PWM波的频率;k为系数(当工作在减计数或增计数时,a为1,当工作在增减计数模式时,a为2.)TBCLK为时钟基准频率,它的大小由HSCLKDIV与CLKDIV决定,本论文中把时钟基准频率设置为150MHz.

本文配置EPWM工作于增加计数模式,由公式(4)可得,要产生50KHz的PWM波,则TBPRD的值设为3000,设置代码如下:

volatile Uint16 EPWM1_TIMER_TBPRD=3000;

volatile Uint16 EPWM2_TIMER_TBPRD=3000;

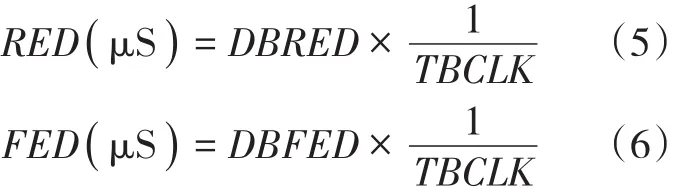

3)死区时间设置:

为满足开关管的软开关,需要设置死区时间,可以通过设置死区上升沿寄存器(DBRED)和下降沿延迟寄存器(DBFED)来设置死区时间,根据下面公式:

本文死区时间为5us,由式(5)、式(6)可得DBRED的值和DBFED的值为750,设置代码如下:

EPwm1Regs.DBFED=750;

EPwm1Regs.DBRED=750;

EPwm2Regs.DBFED=750;

EPwm2Regs.DBRED=750;

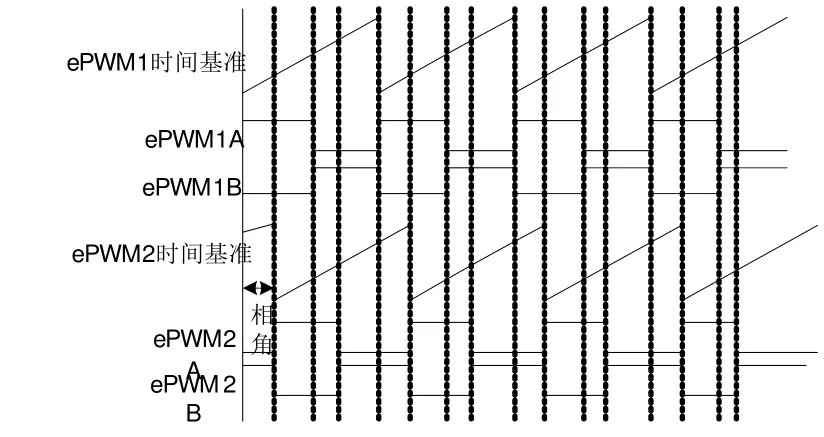

3.2 移相角控制

如图5所示,以EPWM1产生的PWM波为基准,EPWM2在此基础上进行移相.

图5 移相波形图

通过设置相移寄存器(TBPHS)可以达到移相目的,EPWM1相角为00,代码设置如下:

EPwm1Regs.TBPHS.half.TBPHS=0;

其中phshift为所需改变的相角.TBPHS的值对应相角的转换,根据下面公式实现:

当TBPHS=0时,相角phshift为00,当TBPHS=4096时,相角phshift为1800.

4 电路结果分析

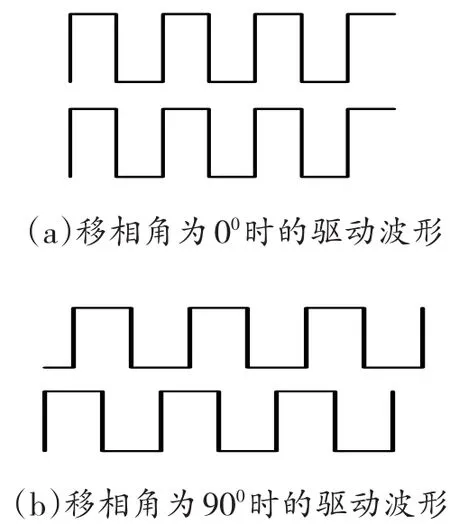

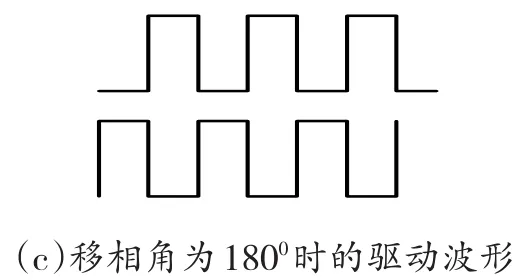

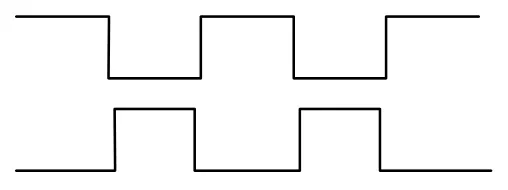

本实验为移相全桥电路电路提供两组互相对称带死区的驱动信号,为降低功率开关管驱动信号的开通、关断延时,通常在栅极输入端加一个5Ω的小电阻,在栅极和源级之间加一个10kΩ的电阻.EPWM1与EPWM2之间不同移相角的驱动波形如图6所示,移相角为00时的驱动波形如图6(a)所示,移相角为900时的驱动波形如图6(b)所示,移相角为1800时的驱动波形如图6(c)所示.同一桥臂上下两管之间带死区的驱动波形如图7所示.

图6 EPWM1与EPWM2之间不同移相角的驱动波形

图7 同一桥臂上下两管之间带死区的驱动波形

5 结语

数字化的IR2110驱动电路结构简单,单个芯片可以驱动两个功率开关管,在桥式电路中有广泛的应用.本文对外围电路的设计,各个器件的参数选择,DSP28335各寄存器的配置及移相原理进行设计,实现了移相全桥数字化驱动.实验结果表明,通过对DSP的控制可以对移相角进行控制,完成不同负载条件下,输出电压的稳定.