基于FPGA的图像处理系统设计与实现

吴 松,张利华

(华东交通大学,江西 南昌330013)

0 引言

数字图像处理目的是把图像中没用的信息去除掉,保留或者恢复提供给用户参考的数据信息。随着用户对图像的细节信息越来越关注,图像处理要求越来越高[1]。尽管软件算法的不断优化能够在一定程度达到要求,但是软件算法优化已经趋近瓶颈[2]。目前,基于嵌入式的图像采集平台包括ARM、FPGA和DSP,基于FPGA的SOPC比ARM系统处理速度快,比DSP系统控制能力强[3]。以往的图像采集与处理多是由图像采集卡完成图像采集后再由计算机对其进行处理,这种方法虽然具有处理速度快的优点,但存在着价格昂贵、功耗高、体积大等不足[4-5]。

通过硬件FPGA实现图像采集处理具有以下优势:① 更多复杂的算法需要嵌入到到硬件平台上实现,能够节约图像处理的时间,增加实时性[6];② 基于嵌入式的硬件图像处理系统可以进行多次开发,而且每次开发周期较短,节约开发成本;③ 将图像处理功能集成在专用芯片或者FPGA片上系统中,占用空间小,便于携带和户外监控[7]。基于FPGA的诸多优势,文中提出采用可编程逻辑器件FPGA实现图像采集处理的方案,在FPGA上实现摄像头OV7725、SDRAM以及VGA的控制。通过完成各个模块设计,将图像采集系统联调,预期采集系统工作正常,性能良好。

1 系统设计

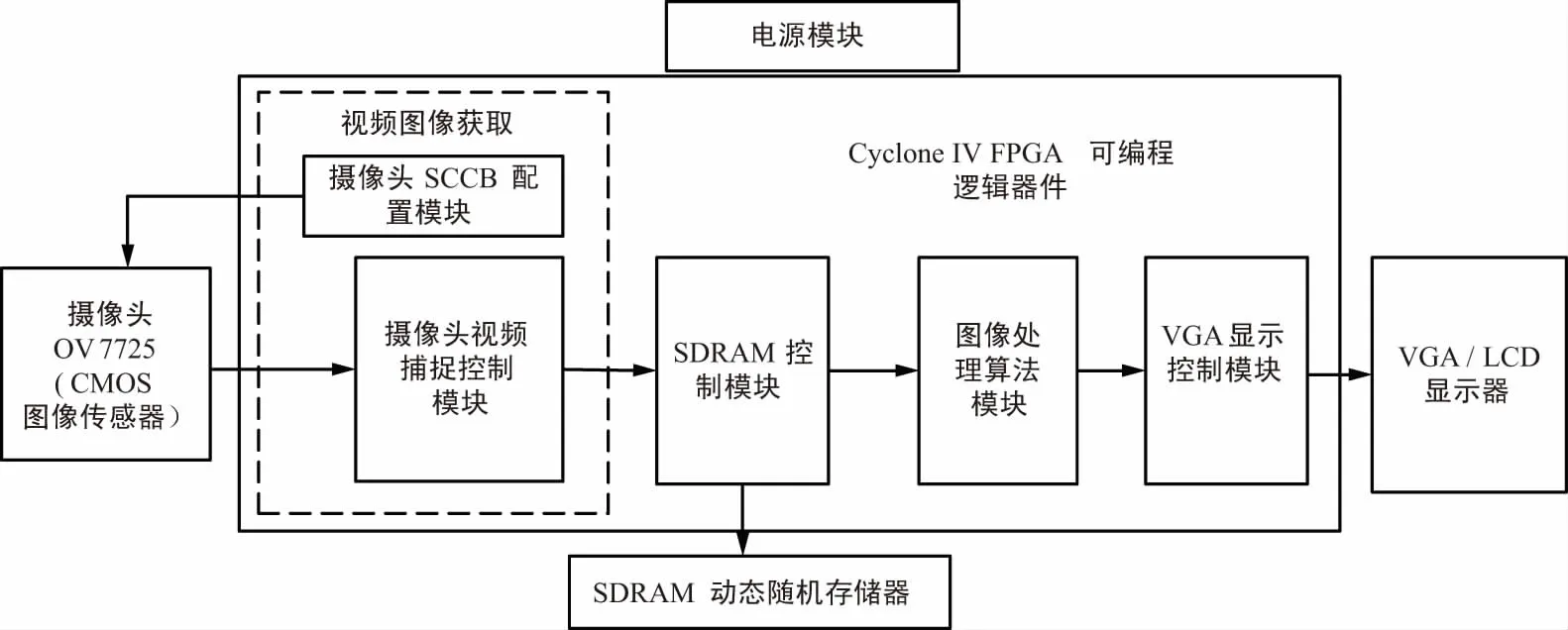

整个系统由视频图像采集、SDRAM存储、图像处理算法、VGA显示控制以及电源模块组成,其中SDRAM控制模块、VGA显示控制模块、图像算法模块全部模块集成在FPGA芯片中。实现平台使用Altera公司Cyclone IV系列EP4CE10E22C8为核心实验板,该芯片包含专用外部存储器以及flash接口,可以支持DDR存储器和动态随机存储器,最高提供150 000个逻辑单元。

系统的功能框图如图1所示。FPGA控制摄像头OV7725采集视频图像,将数据写入SDRAM存储器缓存。FPGA调用图像处理算法对SDRAM中的数据进行处理,处理后的图像数据送至VGA显示控制模块,经过VGA外围接口电路呈现在VGA显示屏上。

图1 系统的功能框图

2 图像处理系统主要模块设计

2.1 OV7725摄像头配置模块

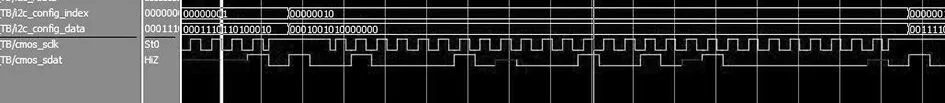

摄像头OV7725芯片内部集成了图像采集模块、数模转换模块、DSP处理器,具有标准的SCCB配置接口,能够配置输出RGB565、YCbCr422、RAW等视频流格式,支持VGA的分辨率图像尺寸。摄像头OV7725总共有172个内部寄存器,但不是每个寄存器都需要配置,很多采用默认的配置,通过SCCB总线进行配置[8]。摄像机串行控制总线(SCCB)由时钟信号SIO_C、数据信号SIO_D以及使能信号SCCB_E组成,为了节省芯片引脚,只采用了SIO_D和SIO_C。SCCB时序与I2C时序类似,SCCB总线仿真时序如图2所示。

图2 I2C总线仿真时序图

SCLK为高电平,SDA由高电平变低电平,总线开始传输;SCLK为高电平,SDA由低电平变高电平,总线传输结束。SCCB为串行传输,每次传送一个字节。通过SCCB设置OV7725的工作模式后,就能够捕获图像数据。行同步信号有效时,摄像头连续输出1 280个像素的一行数据。而且数据输出只有高8位有效,低2位被去除。RGB565格式分布是{R[4:0],G[5:0],B[4:0]},先输出RGB的高8位,然后接着输出RGB的低8位,通过将两个数据进行拼接得到需要RGB数据。RGB565格式数据拼接的关键代码如下:

if(byte_flag == 1'b1) ∥当采集到两个有效数据时,开始拼接这两个数据

cmos_frame_data_r <= {cmos_din_r,cmos_din};∥MSB -> LSB

else

cmos_frame_data_r <= cmos_frame_data_r;∥采集完之前,输出的数据保持不变

end

2.2 SDRAM存储模块

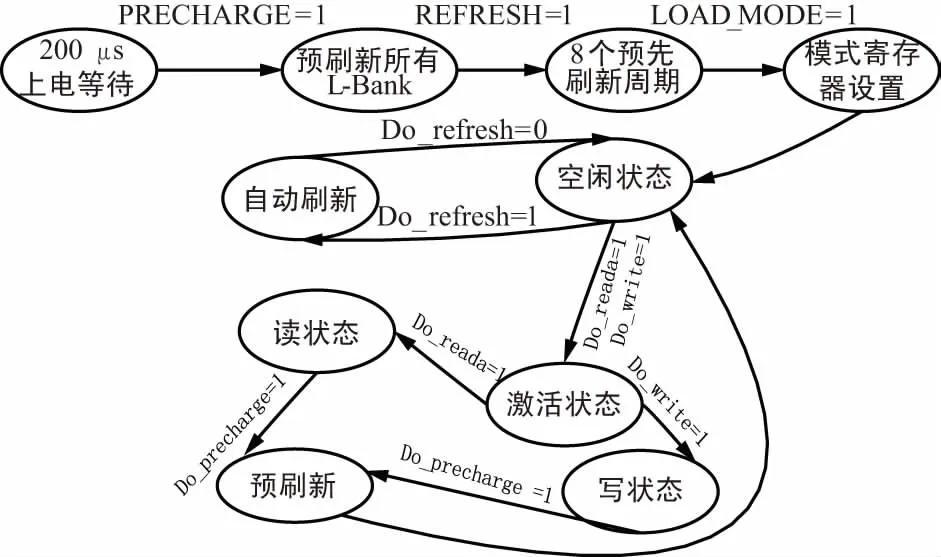

由于摄像头采集的数据与SDRAM控制器接收数据的速度存在速度匹配问题,需要解决跨时钟域的问题,通过调用FIFO模块来实现。为了能够实时快速显示图像,运用乒乓操作来完成。首先调用两个FIFO模块,一个用于读取,一个用于写入。摄像头采集数据首先写入FIFO,当FIFO写满之后,控制器直接一次性读取FIFO中所有数据存储到SDRAM的第一块当中;然后第一块等待读取,第二块进行写入,这样达到一边读取一边写入的效果,不仅加快显示速度,而且充分利用了SDRAM的存储空间。SDRAM控制器主要包括控制模块、命令模块、数据传输模块三部分[9]。命令模块主要为了实现控制器中的状态机以及实现在SDRAM的读操作和写操作,并且实现SDRAM的动态刷新,保证SDRAM控制器的正常操作。数据传输模块主要完成SDRAM的数据传输。SDRAM控制模块移植厂家开源的代码,控制模块状态如图3所示。

图3 控制模块状态图

2.3 Sobel边缘检测

步骤一:计算Gy和Gx与模板每行的乘积

if(!rst_n) begin

Gx_temp1 <= 0;

Gx_temp2 <= 0;

Gx_data <= 0;

end else begin

Gx_temp1 <= matrix_p13 + (matrix_p23 << 1) + matrix_p33;∥postive result

Gx_temp2 <= matrix_p11 + (matrix_p21 << 1) + matrix_p31;∥negetive result

Gx_data <= (Gx_temp1 >= Gx_temp2) ? Gx_temp1 - Gx_temp2 :Gx_temp2 - Gx_temp1;

end

步骤二:计算平方和

if(!rst_n)

Gxy_square <= 0;

else

Gxy_square <= Gx_data * Gx_data + Gy_data * Gy_data;

步骤三:计算平方根

SQRT u_SQRT

(.radical(Gxy_square),

.q(Dim),

.remainder ());

2.4 VGA显示模块

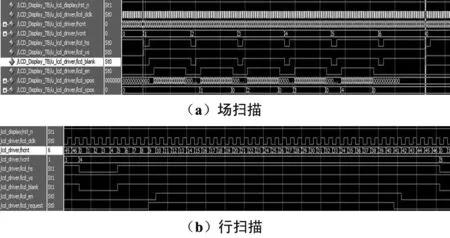

在VGA显示过程中,需要同步信号来决定扫描的开始以及结束。每一行有效的时间和整体扫描的时间不同,而且要小一点,因此在程序的设计过程中需要考虑。扫描的时序主要根据显示器的基本原理进行展开[13-14]。用户只需要满足显示的时序要求,就能够设计完成这部分的代码。通过modelsim完成仿真测试的VGA仿真时序图,如图4所示。

图4 VGA仿真时序图

在测试过程中,为了能够形象看到VGA的扫描过程,笔者将行和列的像素数按照一定的比例进行减少,观察图4,当行计数值hcnt达到用户设定的数(46),行计数清0,场计数vcnt增1,直到行、场都扫描完成,一帧图像显示完成。根据笔者自定义输入信号,仿真出现预期效果波形。由图4可知,lcd_en(数据显示有效期)只有在行同步信号和场同步信号同时为高电平时才有效。场计数在行计数信号计数达到终点时进行计数,整个VGA时序电路由hcnt和vcnt的值决定。

3 系统测试结果

系统各个模块设计完成后,将设计好的系统下载到FPGA开发板中,系统能够实现图像的采集、处理和显示。基于FPGA的视频图像处理系统,不仅具有体积小、成本低、灵活性高和实时性强等特点,而且系统设计与实现易于小型化、集成化,很容易在一片硅片上实现逻辑功能强大的电路。凭借这样的优点,系统方便携带以及容易安装,对移动式监控有利。另外,系统的算法全部由硬件电路实现,各个模块并行运行,能够满足对图像实时处理的效果。系统采集到的图像以及边缘检测算法效果如图5所示。

图5 系统采集到的图像以及边缘检测算法效果

4 结束语

文中设计的基于FPGA的视频采集系统能够实时获取现场图像,同时经过Sobel边缘检测能够对现场图像获取清晰的边缘。该视频采集系统具有低成本、低功耗、小体积以及高图像质量的优点,可以方便地应用于到图像采集与处理以及视频监控项目中;同时通过硬件FPGA实现图像的边缘检测,能够集成于摄像头内,采集的图像不需要上位机软件处理,节约后续图像处理的时间。

[1] 李慧敏,樊记明,杨笑.基于STM32和OV7670的图像采集与显示系统设计[J].传感器与微系统,2016,35(9):114-117.

[2] 刘紫燕,冯亮,祁佳.一种基于FPGA的实时视频跟踪系统硬件平台设计[J].传感器与微系统,2014,33(7):98-102.

[3] 梁皓东,张国平.基于ARM9+FPGA的便携式视频展示台的设计[J].电视技术,2014(3):60-63.

[4] 董心雨,黄俊.基于FPGA的红外图像采集与传输系统设计[J].半导体光电,2012,33(4):579-581,587.

[5] 陈序,卿粼波,何小海.基于FPGA的高速图像处理平台设计[J].成都信息工程学院学报,2013(2):114-118.

[6] 李善寿,方潜生.基于FPGA和CIS的人民币图像采集系统设计[J].传感器与微系统,2010,29(10):97-99.

[7] 孙春凤,袁峰,丁振良.基于FPGA的多通道高速CMOS图像采集系统[J].计算机工程与应用,2008(21):46-48,105.

[8] 杨帆,张皓,马新文,等.基于FPGA的图像处理系统[J].华中科技大学学报(自然科学版),2015,43(2):119-123.

[9] 李明,赵勋杰,毛伟民.Sobel边缘检测的FPGA实现[J].现代电子技术,2009,32(16):44-46.

[10] 艾扬利,杨兵.基于FPGA的Sobel算子并行计算研究[J].现代电子技术,2005(9):42-43.

[11] 李勇,许军,张新喜,等.基于FPGA的高速图像处理系统设计[J].装甲兵工程学院学报,2008(3):54-58.

[12] 崔跃.FPGA在图像处理中的应用[J].中国新通信,2008(9):68-71.

[13] 王啸林,李玉惠.基于FPGA的图像处理系统研究[J].仪器仪表用户,2006(6):10-11.

[14] 邹庆华,邵瑞.基于FPGA的视频图像处理系统研究[J].信息通信,2016(11):78-79.