低成本地下电缆故障测距高速采样电路设计

梅鸣阳,周凤星,沈春鹏

(武汉科技大学 冶金自动化与检测技术教育部工程研究中心,武汉 430081)

行波法可利用脉冲波形与故障返回波形时间差及行波波速,实现地下电缆故障点到测量点距离的测量,对行波信号的采集是行波法故障测距的重要组成部分。行波波形中涵盖许多故障信息,对宽带宽波形进行高速采样十分必要[1]。由于采样频率的增高,普通采样电路无法满足需求,需要设计一款高速采样模块实现对电缆故障信号瞬态变化的记录与存储。高速采样电路的设计不仅受成本及现代模拟器件制造工艺的限制,而且因为工作频率升高,电路中数字信号反射、串扰、延迟等信号完整性问题愈发突出[2-4]。

本文结合2017年武汉国鼎科技有限公司地下电缆故障检测项目需要,设计了基于FPGA控制的高速采样模块,并对该高速电路关键信号进行信号完整性分析,保证该电路能够正常工作。

1 采样参数及方案

在电缆故障测距设备中,脉冲信号上升时间约为13ns,下降时间约为10ns,信号带宽约为35MHz,采样电路需要实现200 MHz的采样频率。考虑成本高低和采样波形重复性使用采样频率较低的ADC,通过并行时间交替采样的方式实现更高频率的等效实时采样[5],通过两采样通道进行交替采样,采样结果进行处理后可等效为两倍时钟频率采样效果。

2 系统结构

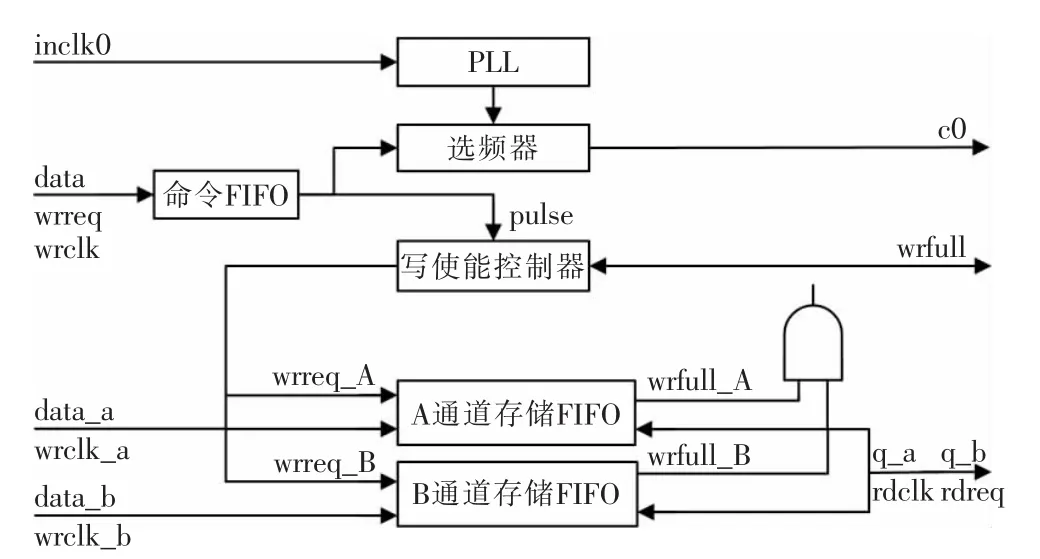

高速采样模块整体结构如图1所示。

图1 采样模块整体框图Fig.1 Sampling module overall block diagram

采样模块采用一片8位、双通道采样芯片AD9288对行波发射信号及故障返回信号进行采样。采集的数据根据时钟缓冲单元分配时钟,交替存储至FPGA中所编写的FIFO储存单元,DSP可利用该储存单元以较低频率获得采样结果并将该结果在液晶屏上显示出来。采样电路是以FPGA作为控制核心实现对信号的处理、采集、存储工作。

3 系统设计与实现

3.1 信号调理电路

模块采用AD8138构成低失真差分ADC驱动电路抑制共模噪声,其共模抑制比可达-77 dB,工作原理如图2所示。

图2 输入信号调理电路Fig.2 Input signal conditioning circuit

行波在电缆传输过程中,高频成分更容易损耗,使用AD8138代替传统巴伦变压器驱动ADC,可以保留低频信息。通过调整VCOM引脚上的电压可1∶1的改变差分输出的共模电压,当该共模电压与ADC的差分参考电压一致时,ADC可获得交流采样最大动态范围。AD8138增益带宽积可达320 MHz,压摆率为1150 V/μs,对于脉冲信号,可快速建立起电压,失调电压一般为1 mV。为保护采样电路不被高电压脉冲信号损坏,可在输入端正反并联2个导通压降较低的肖特基二极管,构成输入保护电路。

3.2 高速ADC芯片

ADC9288是一款由Analog Devices公司生产的低成本高速模数转换器,该芯片具有2个可独立工作的模数转换通道,每个通道能够以100 MS/s转换速率工作。ADC的控制管脚及数字输出管脚兼容TTL(3.3 V)和 CMOS(3.3 V)电平,对控制管脚 S1、S2分别分配为高电平和低电平,设置芯片工作在普通工作模式,此时2个模数转换通道可独立工作。将控制管脚DFS电平设置为高电平,ADC数字信号输出为带偏置的二进制输出。

3.3 FPGA控制电路

FPGA采用ALTER公司生产的EP4CE6E6E22C8N,主要实现编码时钟输出、采样数据的存储及与DSP通信功能,FPGA功能框图如图3所示。

图3 FPGA功能框图Fig.3 FPGA functional block diagram

由FPGA实现的PLL锁相环功能,可实现将外部50 MHz时钟倍频至100 MHz,并将该信号作为ADC采样编码时钟的参考时钟。采样数据的高速缓存是以异步FIFO缓冲器实现的。通过FIFO缓冲器,数据可以较快速度写入,而以较慢速度读出。如图4所示为FPGA时序图。

DSP通过 data、wrreq、wrclk管脚向 FPGA 发送指令,FPGA根据指令输出参考时钟频率C0,同时通过pulse信号使能双通道存储FIFO写入使能信号;采样频率wrclk_a、wrclk_b由C0通过时钟分配模块处理获得,当A,B通道FIFO存储满后wr-full_A和wrfull_B均为高电平,FPGA停止采样并通过wrfull信号通知DSP采样状态,DSP通过输入rdclk时钟信号和rdreq使能信号读取数据。

图4 FPGA时序图Fig.4 FPGA timing diagram

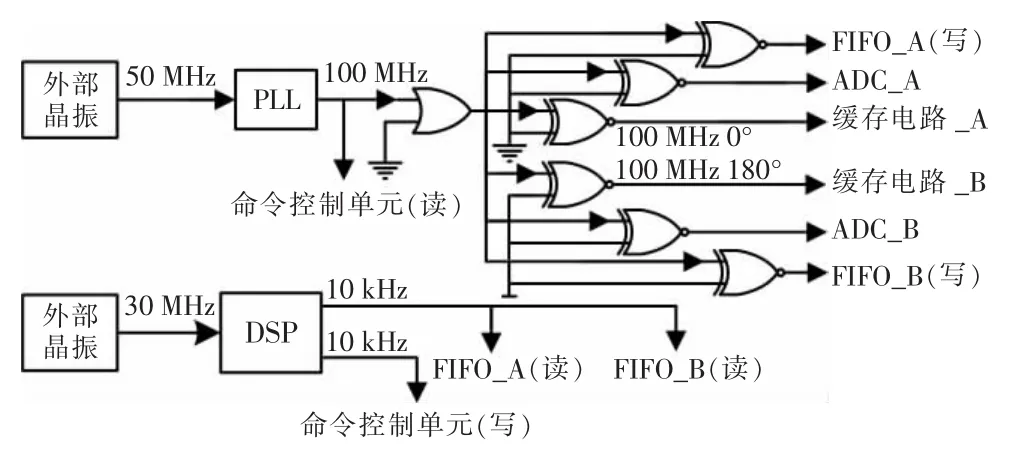

3.4 时钟分配模块

采用时间交叉采样方式对模拟信号进行高速采样,各个数字处理单元都是以时钟信号驱动的,从而保证时序上的一致性,整体时钟分配如图5所示。

图5 系统时钟分配图Fig.5 System clock distribution diagram

外部有源晶振产生的50 MHz时钟信号通过FPGA内PLL倍频至100 MHz,该信号作为FPGA内部控制信号的时钟驱动,同时该时钟信号通过74LXC86异或门电路与不同电平逻辑运算获得相位相差180°的两路100 MHz时钟信号。存在相位差的时钟信号分别作为2个采样通道时钟驱动。

3.5 信号完整性问题的提出

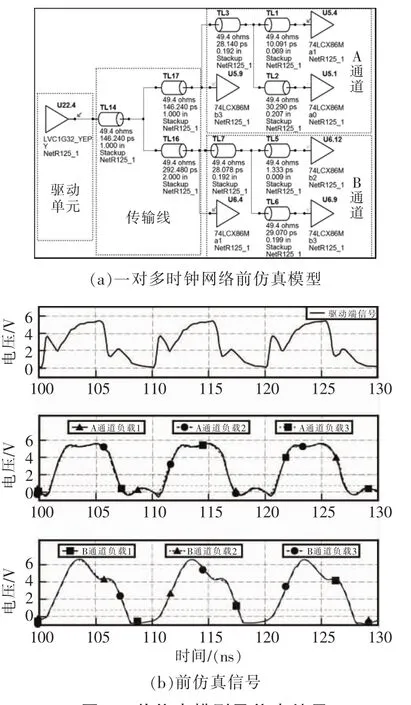

该采样设备由于工作频率较高,可能存在信号问题,图6为时钟分配网络中直接使用一个与逻辑门电路驱动6个异或逻辑门电路信号仿真图。

可见驱动信号在高低电平变化时并非单调,而AB两路接收到的信号也存在畸变现象。负载门电路将高于2.0 V电平识别为高电平,低于0.8 V电平识别为低电平。此时给定驱动时钟占空比为50%,经门电路输出时钟占空比约为61%,这将导致双通道的采样相对相位不能保证为180°,其最终合成波形无法等效为200 MHz的采样频率。为保证系统能按设计逻辑工作,在PCB布线过程中,需对部分传输网络进行仿真,保证负载端对电路信号时序、持续时间和电压幅值等问题的要求[6-7]。

图6 前仿真模型及仿真结果Fig.6 Simulation model and simulation results

3.6 一对多信号质量控制

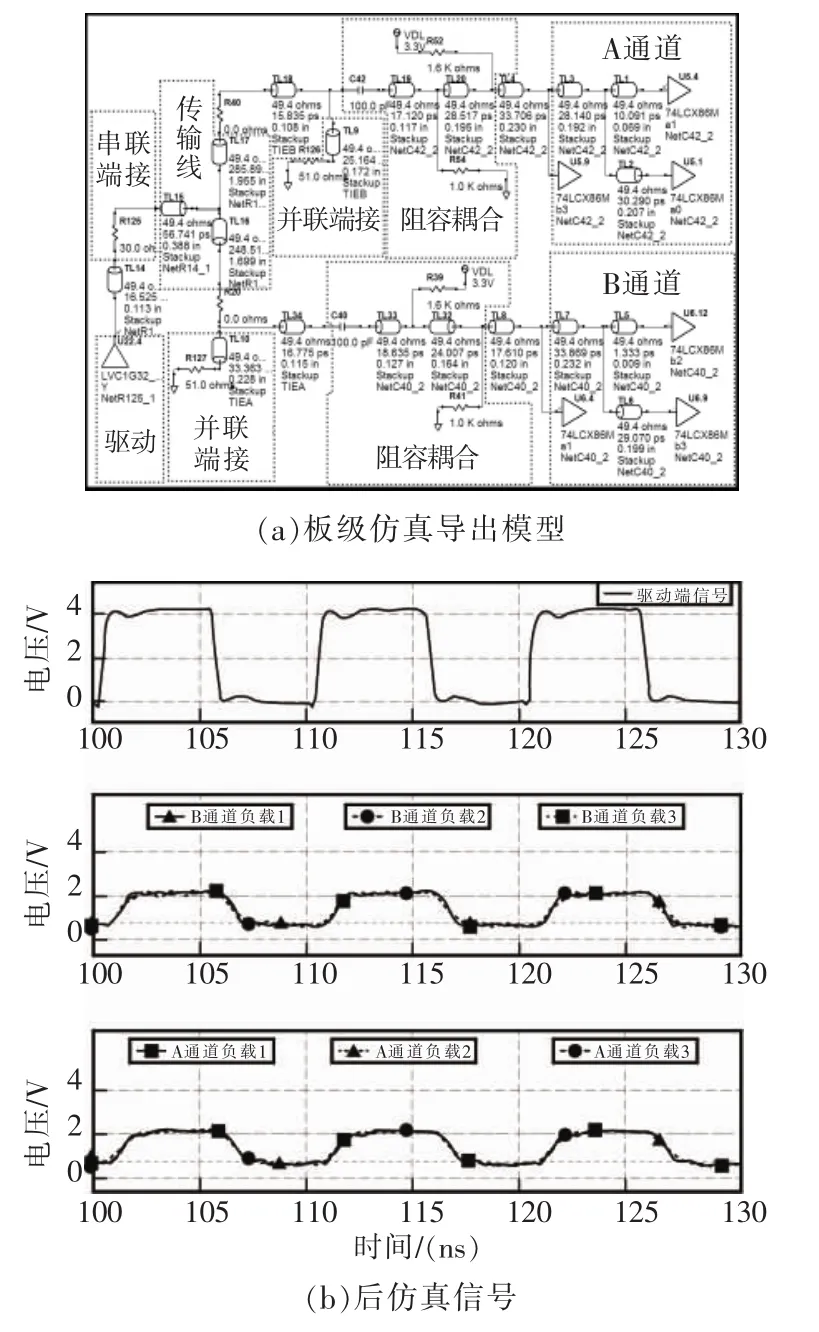

时钟分配网络中,为保证两路信号同时到达,需各分支布线长度等长。树形拓扑结构在分支处会导致阻抗发生改变,反射信号噪声不仅会在分支内造成干扰,而且分支与分支之间也会互相干扰,因此需在驱动端及负载端都添加端接电阻[8-9]。

在驱动端使用串联端接的方式抑制噪声,要求串联端接电阻与驱动器输出阻抗之和等于传输线特征阻抗,该设计中串联电阻为30 Ω。在负载端,由于同一通道3个负载位置较为接近,该处分支较短,非均匀传输线距离短,阻抗突变造成的反射可忽略不计,可在靠近负载处并联端接电阻,抑制一级分叉造成的噪声,并联电阻阻值与传输线阻抗一致。由于添加了端接电阻,会导致驱动端驱动能力不足,使用阻容耦合方式保证负载正确识别电平。

对驱动电路重新进行设计并布线,经过反复实验,获得最终板级仿真导出模型及相关信号图如图7所示。驱动端的波形能够维持方波形状,AB通道的负载端信号几乎一致,时钟信号在电平敏感区域单调。

图7 后仿真模型及仿真结果Fig.7 Postsimulation model and simulation results

3.7 PCB设计相关规则

设备工作于高频状态,按照以下方案设计PCB以预防常见的信号完整性问题:

(1)设计四层PCB层叠,保证信号有完整参考平面,防止跨平面阻抗变化导致的信号反射;

(2)ADC及FPGA信号传输总线为点对点连接,需添加端接电阻抑制反射噪声;

(3)数据总线PCB布线需遵循3W原则,防止串扰;

(4)高速芯片附近需添加去耦电容,防止地弹噪声。

4 实验结果

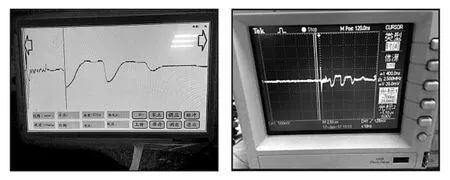

为验证采样模块行波信号采样效果,取一段长约200 m的双绞线电缆作为测试对象,模拟现场电缆故障测距。以电缆一头作为测试点的起始端,另一头作为测试点的末端,终点短路,模拟低阻故障进行电缆故障检测实验。该采样模块采样数据在液晶屏上显示结果与示波器检测结果对比如图8所示。

图8 采样模块样机采样效果Fig.8 Sampling module prototype sampling effect

由实验结果可知,采样模块可按设计正常工作,样机能够准确获得50 ns驱动信号及故障返回信号,并且可以通过该信号判断出电缆故障点的位置。

5 结语

通过对低压脉冲法对信号采样的需求分析,设计了一套由FPGA控制的高速采样电路,该电路成本低且结构简单,适用于便携式设备中使用。为保证该电路能够正常工作,对电路中时钟分配网络进行了信号完整性的仿真分析及电路改进。通过实际板卡现场试验,验证了电路设计及仿真的准确性,实现了对低压脉冲故障信号的采集,为电缆故障检测设备研制后续工作出了铺垫。

[1] 李金平,颜铤.便携式电缆故障定位仪的设计研究[J].北京联合大学学报,2006,20(2):49-52.

[2] 谢锐,裴东兴,姚琴琴.高频信号动态测试中的信号完整性分析[J].仪器仪表学报,2017,38(3):773-779.

[3] 吴健,孔德升.高速数据采集卡的信号完整性分析[J].仪表技术与传感器,2013(12):93-96.

[4] 杨华,陈少昌,朱凤波.高速数字电路PCB中串扰问题的研究与仿真[J].电光与控制,2012,19(3):90-94.

[5] 李南,陈以方,原可义.基于CPLD的8位400MSPS高速信号采集卡设计[J].无损检测,2009(4):294-296.

[6] 陈丽.传输线信号完整性的反射分析[J].工矿自动化,2014,40(3):49-52.

[7] 罗必露,杨昭荣.基于Cadence的接收机信号完整性设计[J].微波学报,2016(s2):498-500.

[8] 吴长瑞,岑凡,蔡惠智.FPGA与DDR2 SDRAM互联的信号完整性分析[J].计算机工程与应用,2011,47(29):158-160.

[9] 楼津甫,张褔洪,曾榕.基于SI分析的高速数字接口拓扑结构设计[J].Hans Journal of Wireles-s Communications,2014,4(6):99-106. ■