短沟MOS器件GIDL漏电的改善

顾 祥,陈 天,洪根深,赵文彬

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214035;2.华润微电子有限公司,江苏无锡 214061)

1 引言

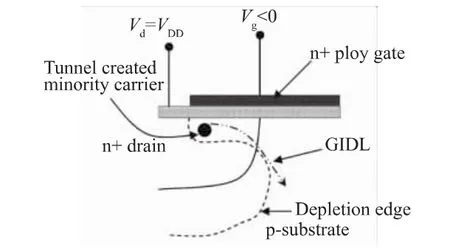

当工艺制程进入深亚微米阶段,短沟道效应(SCE)引起的亚阈漏电使CMOS器件的关态特性变差、静态功耗增大;在数字电路和存储单元中,它还可能导致逻辑状态絮乱。当栅介质层按等比例缩小,栅漏电压VDG(VG=0,VD<击穿电压)使NMOSFET栅覆盖的漏区表面为深耗尽时,能带发生弯曲使Si价带电子通过带-带(B-B)遂穿进入导带,流向漏极,而产生的空穴绝大部分流向衬底,形成二次击穿电流,即GIDL电流,如图1所示,从而导致击穿电压降低,截止状态特性进一步蜕变[1-3]。GIDL效应是引起极小尺寸MOSFET亚阈漏电的关键因素[4,5]。

图1 GIDL漏电流产生机制

超深亚微米器件为了抑制SCE效应,改善器件的关态特性,基本采用带有角度的Halo注入工艺,提高器件源漏结附近的沟道掺杂浓度,有效减弱了源漏向沟道区的耗尽[6-8],但该工艺的引入使得源漏掺杂对GIDL的影响机制变得更加复杂。本文利用工艺实验和器件的二维模拟仿真,给出了Halo注入、LDD注入对NMOS器件GIDL效应的影响,实验数据显示了Halo注入工艺比其他工艺对GIDL效应的影响更大,通过降低Halo注入可以有效改善GIDL效应。

2 实验

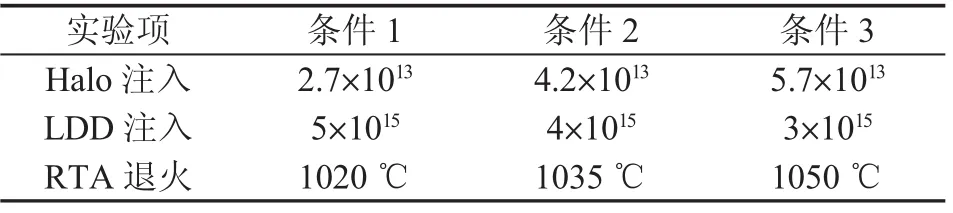

本文基于0.13 μm 1.2 V/3.3 V逻辑工艺平台,研究对象是1.2 V NMOS器件,多晶栅长0.13 μm,栅宽10 μm,栅氧厚度1.6 nm,主要工艺流程见图2;对工艺过程中的Halo注入、LDD注入、源漏RTA退火进行分片试验,分片条件见表1;试验后通过Vg-Id曲线、饱和电流以及漏电流的测试来评估不同工艺对GIDL效应的影响。GIDL主要由栅覆盖漏区表面发生耗尽时的能带弯曲程度决定,短沟器件中沟道横向电场和栅漏电势差导致沟道区上方界面态的两级隧穿,B-B隧穿机制决定的GIDL电流表示见式(1)和(2):

其中A为比例系数,Ea为栅覆盖的漏区表面电场,B的理论值为21.3 MV/cm,Ea=(Vdg-1.2)中常量1.2为保证B-B隧穿所需的表面势,即能带弯曲量。

图2 1.2 V NMOS器件主要工艺流程

表1 工艺试验条件

当Vdg较小时,由于漏区表面电场降低,能带弯曲减小,电子准费米能级已处于禁带中,B-B隧穿很难发生;只有在Vdg较大的情况下,B-B隧穿导致的GIDL漏电才会加剧,因此我们在测Vg-Id曲线时,必须将Vg扫到-0.5V,将不同工艺条件的GIDL情况明显地反映出来。

3 结果与讨论

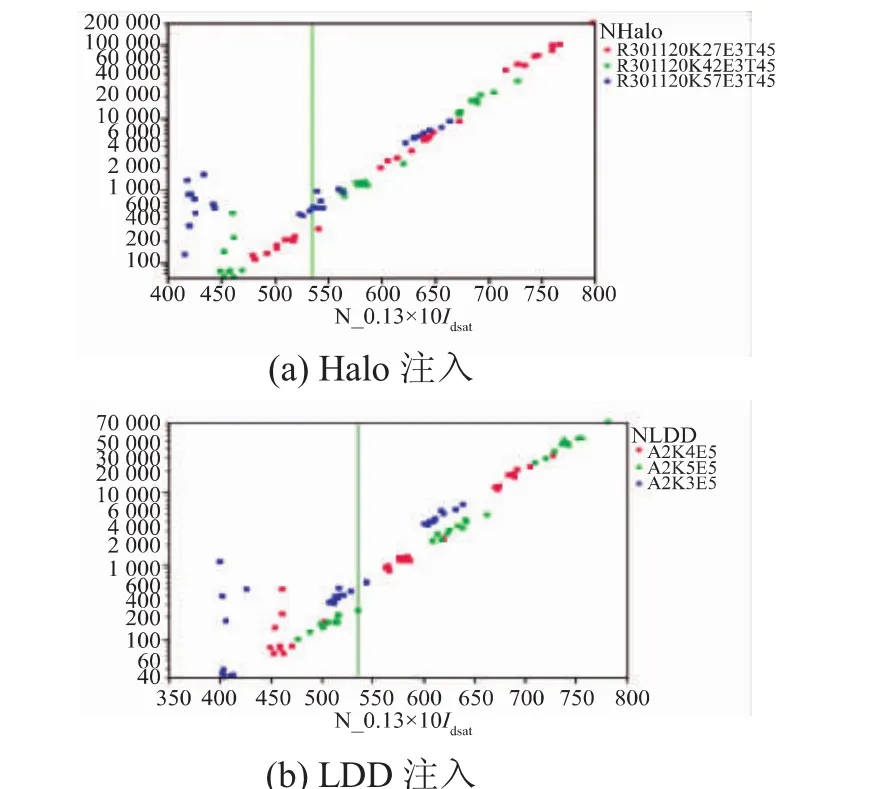

3.1 Halo和LDD注入剂量对GIDL的影响

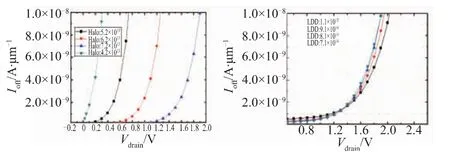

图3显示了不同Halo和LDD注入剂量下器件的Vg-Id曲线和Ioff相关性曲线。从实际测试结果可以看出,当Halo注入剂量增加或LDD注入剂量减小时,器件的GIDL漏电增大,Ioff漏电也明显增大。图4则反映了不同饱和电流的器件漏电流随着Halo注入剂量和LDD注入剂量变化的趋势,饱和电流较小的器件,由于阱浓度相对较大,在Halo注入剂量较大或LDD注入剂量较小时,很多测试点的漏电流出现了明显增大,另外,我们可以从图3和图4中发现,Halo注入对GIDL漏电的影响程度明显比LDD注入大。

图3 Halo/LDD注入对Vg-Id曲线的影响

图4 Halo/LDD注入对Idsat&Ioff曲线的影响

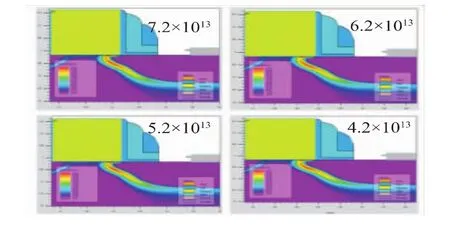

我们采用Silvaco TCAD软件对器件的电流密度及电场分布进行了仿真,不同工艺条件的电流密度分布情况如图5所示,电场分布情况如图6所示。

图5 不同Halo注入剂量下的电流密度分布图

图6 不同Halo注入剂量下的电场分布图

从仿真结果可以看出,当Halo注入剂量增加或LDD注入剂量减小时,器件漏区到衬底的漏电流明显增加,漏衬PN结的峰值电场也明显增大;器件Ioff的仿真值与实验结果基本一致,具体如图7所示,相对较小的Halo注入或较大的LDD注入剂量,不容易发生表面反型,结的耐压偏大。此外,LDD浓度越高,耗尽层越窄,使得能发生带间隧穿的面积减小,因此GIDL漏电小。在漏极电压为1.3 V的强电场下,不同LDD注入剂量下GIDL漏电流曲线有一个交点,这里进一步说明了只有当VDG大于某个电压值时,LDD注入对器件的GIDL漏电才起到主导作用。

图7 不同Halo/LDD注入剂量对应的Ioff仿真值

3.2 RTA对GIDL的影响

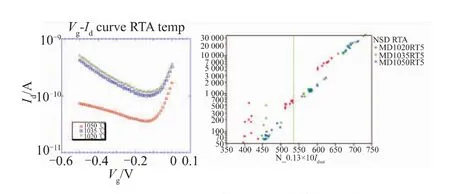

图8(左)显示了不同RTA退火,器件的Vg-Id曲线和Ioff相关性曲线。从实际测试结果可以看出,当RTA温度降低时,器件的GIDL漏电增大,Ioff漏电也明显增大。图8(右)反映了不同饱和电流的器件漏电流随着RTA退火温度变化的趋势,饱和电流较小的器件,由于阱浓度相对较大,在RTA退火温度较低时,很多测试点的漏电流出现了明显增大。

图8 不同RTA温度下的器件特性曲线

对工艺的RTA温度进行了模拟仿真,器件的Ioff仿真曲线如图9所示,与实际的实验结果一致,器件的漏电随着RTA的温度升高而降低。当RTA温度升高时,虽然源漏PN结的位置会向沟道侧延伸,使得栅下耗尽区的面积增大,更容易发生B-B隧穿,但是此时的PN结沟道侧的浓度降低,使得表面垂直电场降低,使GIDL漏电降低,因此,基于当前工艺条件,掺杂浓度降低对GIDL起了主导作用。

图9 不同RTA温度下的Ioff仿真值

3.3 小结

总结以上Halo注入工艺、LDD注入工艺、RTA退火温度工艺对GIDL的影响,本质上都是漏衬PN结的掺杂分布的变化,源漏掺杂浓度较低时,漏区耗尽区展宽,表面垂直电场降低,B-B隧穿强度降低;掺杂浓度提高,使表面能带弯曲增大,表面电场增强,但表面耗尽区宽度变窄,发生B-B隧穿的有效区域较小,GIDL开始减小;另外,我们可以很明显地看出Halo注入工艺对GIDL的影响程度明显比其他工艺大,而RTA工艺对整个工艺平台的影响较大,一般情况下不会轻易改变它,因此,降低Halo注入剂量是改善GIDL的最佳且可行的方案。

4 结论

本文详细介绍了超深亚微米器件GIDL漏电的原理和产生机制,并对0.13 μm逻辑工艺中影响GIDL的关键工艺步骤进行了工艺试验流片。试验结果显示,通过降低Halo注入剂量、增大LDD注入剂量、提高RTA退火温度都可以改善GIDL所产生的漏电,但最佳优化方案是降低Halo注入剂量。

同时,对工艺器件进行了模拟仿真,仿真结果与试验结果一致,并通过器件剖面的电流分布图和电场分布图,说明GIDL效应的强弱,最后结合B-B隧穿的产生机制,解释了不同工艺条件对GIDL的影响趋势,并为GIDL的改善提出了建设性意见。

[1]J Chen,TY Chan.Subbreak-down drain leakage current in MOSFET’s[J].IEEE Electron Device Lett,1987,38:515.

[2]TY Chan,J Chen.The impact of gate-induced-drain-leakage on MOSFET scaling[J].IEDM Tech,1987,48:718.

[3]GQ Lo,DL Kwong.Hot-carrier-stress effects on gate induced drain leakage current in n-channel MOSFET’s[J].IEEE Electron Device Lett,1991,12(1):5.

[4]C Chang,J Lien.Corne-field induced drain leakage in thin oxide MOSFETs[J].IEDM Tech,1987,45:714.

[5]K Rais,F Balestra.Temperature dependence of gate induced drain leakage current in silicon CMOS devices[J].Electron,1994,30(1):324.

[6]Ws Feng,T Y chan.MOSFET drain breakdown voltage[J].IEEE Electron Device Lett,1986,36:449.

[7]T Y Chan,J Chen.The impact of gate-induced drain leakage current on MOSFET scaling[J].IEDM Tech,1987,49:718.

[8]T E Chang,CH Huang.Mechanism of interface trap-induced drain leakage current in OFF-state n-MOSFET’s[J].IEEE Trans.Electron Devices,1995,42:738.