10 bit 100 MS/s混合型模数转换器

张 章, 余文成, 解光军

(合肥工业大学 电子科学与应用物理学院,安徽 合肥 230009)

由于逐次逼近型模数转换器(Successive Approximation Register Analog-to-Digital Converter, SAR ADC)具有结构简单、功耗低、面积小等特点,且不需要运算放大器,使得SAR ADC比其他奈奎斯特模数转换器更适合现代互补金属氧化物半导体(Complementary Metal Oxide Semiconductors, CMOS)工艺的演进路线[1].然而,基于传统结构的N比特SAR ADC每完成一次转换都需要进行N次比较,而每次的比较速度又受限于电容型数模转换器(Digital to Analog Converter,DAC)的建立时间和逻辑控制电路的传递延迟.因此,传统结构的这种缺陷阻碍了SAR ADC 向高速高精度领域的发展.为了改善这个缺陷,研究者们利用SAR ADC的特点,开始在其传统结构的基础上尝试研究混合型结构的高性能ADC,例如流水线-逐次逼近(Pipeline-SAR)混合型ADC[2]、时域交织(Time-Interleaved,TI)ADC[3]和全并行-逐次逼近(Flash-SAR)混合型ADC[4].其中,Pipeline-SAR混合型ADC能提高传统SAR ADC的速度,但是引入了运算放大器,增加了系统的复杂度和整体功耗.时域交织型SAR ADC虽然提升了传统SAR的速度,但ADC的性能却受到通道间失配的影响,需要额外的校准电路来解决.Flash-SAR混合型ADC利用高转换速率和结构简单的Flash ADC来提高SAR ADC的整体性能,让其在面积、速度、功耗以及精度方面具有较好的折中.

文中所设计的混合型ADC采用“3+8”的两极流水线结构,利用Flash ADC并行转换的特点先对信号进行粗量化,得到 3 bit 数字码输出,再利用SAR ADC对余量信号进行细量化处理,得到 8 bit 数字输出;最后,通过冗余位数字校准电路得到 10 bit 的量化精度.

1 ADC的系统结构

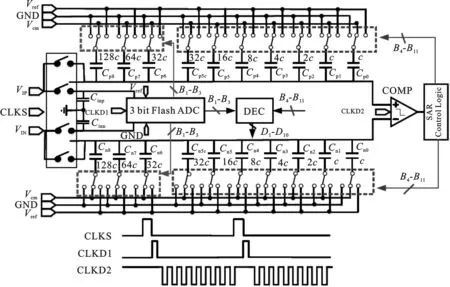

所设计的Flash-SAR ADC其结构框图和时序图如图1所示.结构包括第1级Flash ADC结构和第2级SAR ADC结构、数字校准电路.所述第1级全并行模拟数字转换器包括 3 bit Flash和数字编码电路.所述第2级逐次逼近模拟数字转换器包括高位电容底极板电平切换控制器和低位电容底极板电平切换控制器、比较器、高位数模转换器(Digital to Analog Converter,DAC)电容阵列和低位DAC电容阵列.相较于现有的SAR ADC结构,所设计的混合型ADC利用Flash ADC并行转换的特点先对信号进行粗量化,得到 3 bit 数字码输出;再利用SAR ADC对余量信号进行细量化处理,得到 8 bit 数字输出.这样可以减少SAR在一个周期内的转换次数,从而提高了SAR ADC的转换速率.加入的 1 bit 冗余位可以容忍32最低有效位(Least Significant Bit,LSB)的失调电压[5],因此只要第1级Flash ADC中比较器的调电压小于这个误差容限,后面的数字校正电路都可以将错误结果纠正过来,从而不影响整个系统的性能.

图1 Flash-SAR ADC的结构框图和时序图

2 电容阵列DAC的非线性与噪声分析

二进制权重电容阵列DAC中单位电容的选取要根据电容阵列DAC的非线性和热噪声来确定,下面将分别根据非线性和热噪声的要求来计算所需的电容值.

2.1 DAC的非线性分析

电容失配是主要影响DAC线性度的主要因素,同时也会增大静态参数微分非线性(Differential NonLinearity,DNL)和积分非线性(Integral NonLinearity,INL)的误差.因此,可根据给定的INL指标,计算出DAC电容阵列中单位电容的最小值.但需要满足的条件是: 静态参数INL因电容失配而带来的误差要小于量化噪声.

假设C1=Cu+ε1,Ci=2i-2Cu+εi(i=2~N-1),其中εi是第i位理想电容值与实际电容值之间的差,如果每个电容之间都满足正态分布,则第i位电容的方差可以表示为

(3)

其中,bi=1,1/2,0,分别代表DAC电容阵列的底极板连接到Vref,VCM,VGND.SAR ADC中INL的表达式为

FINL(y)=VDAC, real(y)-VDAC, ideal(y)VLSB,(4)

其中,VLSB为ADC的最小量化电压.将式(3)代入式(4),得到

(5)

(6)

FINL(y)最大值发生在满量程的一半处,即y=2N-1,将其代入式(6),可得

(7)

在工程中,为了保证一定的良率,通常需要满足:

3σINL<0.5VLSB.(10)

从工艺说明文档中可以查到单位电容失配的标准差与电容值的相关失配系数AC两者之间的关系为

由式(9)~式(11)可计算出在线性度要求下所需要单位电容的最小值为

2.2 DAC的热噪声分析

对于一个N位的ADC,该ADC的量化噪声可以表示为

Δ212=(2VFS)2(12(2N)2) ,(13)

其中,Δ为ADC的理想步长,其值为1个LSB(ADC的最小量化电压),VFS为ADC输入信号摆幅值.通常在设计ADC时,为了减小采样电路热噪声对其精度的影响,总的热噪声必须远小于ADC的量化噪声.其表达式为

对于文中设计的10 bit 100 MS/s混合型ADC,将KT=1.38×10-23×300 J代入上式,并且VFS= 1.6 V,可以计算出电容阵列DAC总电容值为 20 fF.在分辨率为 10 bit 的SAR ADC中,单位采样电容为 (20/2N-1) fF,即 0.156 fF,这个电容值非常小.因此,在中精度SAR ADC中,真正制约单位电容的取值不是噪声的影响,而主要是电容的匹配.

3 HCSR开关切换策略

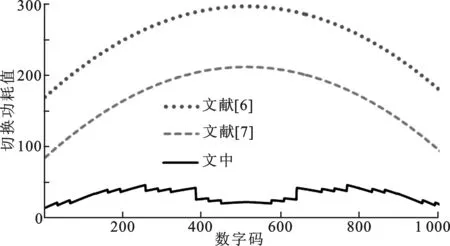

图2 开关切换功耗

文中提出的高位电容跳过与复用的开关策略(Higher Capacitor Skipped or Reused algorithm,HCSR)是用在混合型ADC中,利用Flash ADC得到的量化结果来控制SAR ADC中电容阵列的连接方式.另外,在MCS开关切换策略的基础上,将模数转换过程中始终连接在固定电平VCM端的终端电容加上开关切换的工作,用来判断最低有效位.从而相对MCS开关切换策略,文中提出的开关策略所需要的电容数目减少了一半,在很大程度上优化了面积和功耗.

图2为利用传统的二进制搜索算法时电容充电消耗的能量示意图,图中Csw为开关切换充电至Vref的电容,Cnsw为开关不切换并保持原来状态的电容,CT为DAC电容阵列的总电容.当电容Csw的底极板由VGND充电至Vref时,所消耗的能量为

由式(15)可以看出,当Csw=0.5CT时,消耗的能量E最大.当电容阵列DAC利用传统连续的开关切换策略时,在转换周期中每个电容要经历充电或者放电的过程,这样就导致电容阵列DAC消耗很多能量.但是,在Flash-SAR的混合型结构中,Flash可以对采样到的信号先进行粗量化,根据量化的结果判断采样的差分信号之差的大小.如果这个差值比较大,则电容阵列对电荷重新分配时需要对高位电容进行充放电; 如果这个差值比较小,则高位电容保持原有的状态.

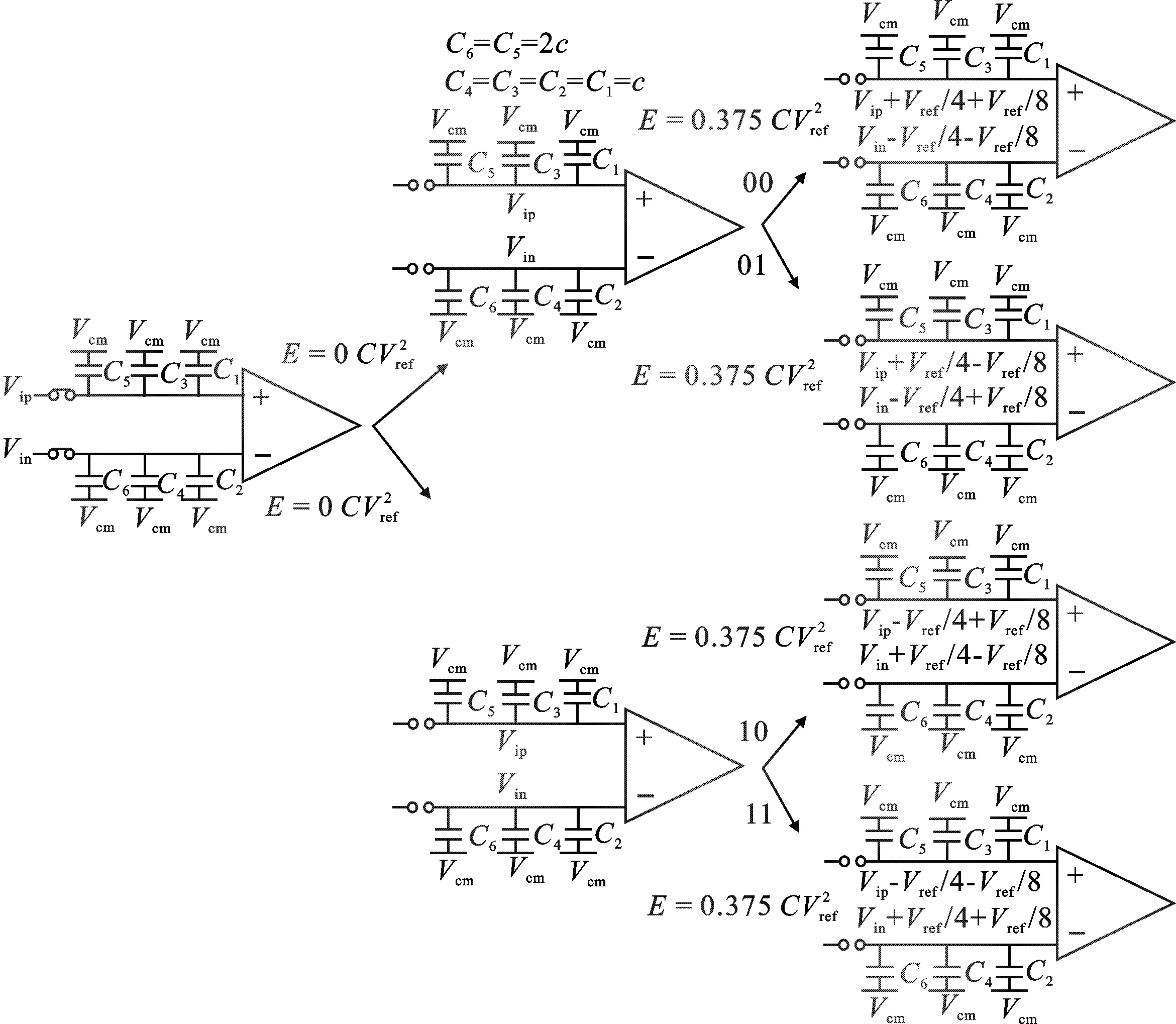

图3给出了采用高位电容跳过与复用算法的3 bit Flash-SAR 混合型ADC的工作原理.其中Flash ADC量化数字码的高位和次高位,SARADC量化数字码的低位.原理图中也标出了电容阵列对电荷重新分配时的开关功耗.如果Flash ADC的量化结果B1B2为00或01时,说明差分信号的差值比较大,为了使电容阵列顶极板的电压最终实现逼近的效果,在DAC电压重新分配时需要对高位电容进行充放电操作.如果Flash ADC的量化结果B1B2为01或10时,说明差分信号的差值比较小,此时电容阵列顶极板的电压已经处在逼近的状态,所以在DAC电压重新分配时就不用对高位电容进行操作,保持原来的状态.

图3 高位电容跳过与复用算法的原理图

图4 3种开关切换算法的功耗对比

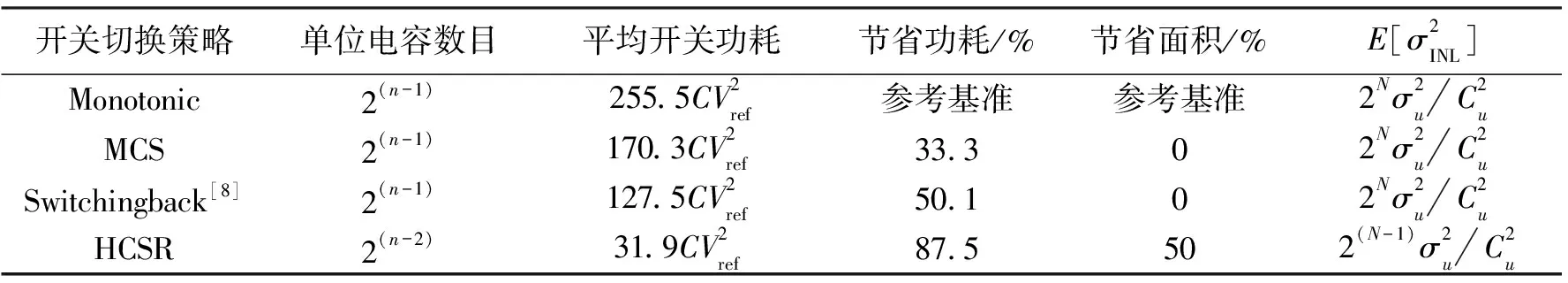

表1为不同开关策略在单位电容数目、平均开关功耗和线性度上的对比总结,其中节省功耗和节省面积的指标是其他开关切换策略相对于Monotonic开关切换策略为参考基准而得出的.从表1的数据可以看出,文中提出的开关策略的平均开关功耗和所使用的单位电容数目是最少的,从而节省了功耗和面积.另外,提出的开关策略的INL特性优于其他3种开关策略,因此具有更好的线性度特征.

表1 不同开关策略的对比

4 电路仿真与结果分析

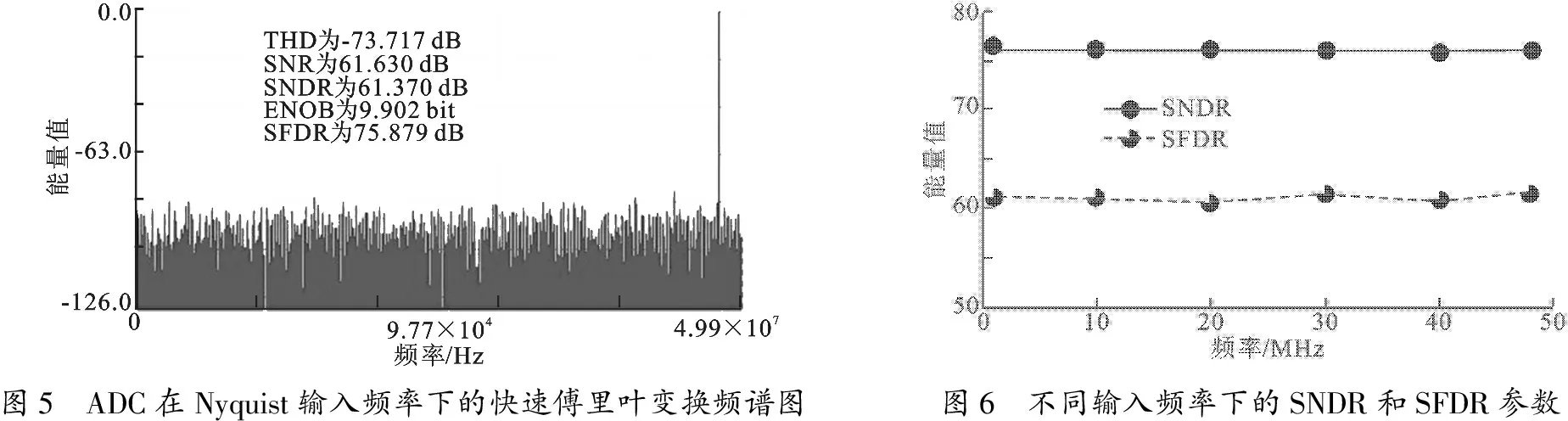

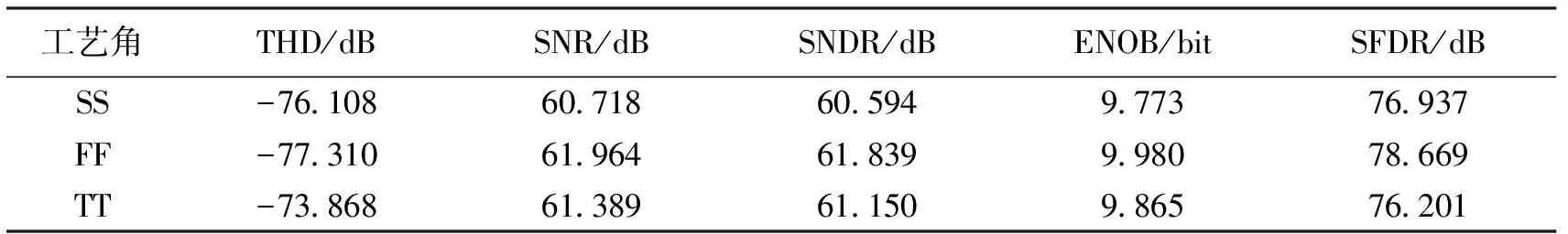

文中所设计的10 bit Flash-SAR混合型ADC采用中芯国际集成电路制造(上海)公司(Semiconductor Manufacturing International Corporation,SMIC) 0.18 μm 工艺实现.当采样频率为 100 MS/s 时,输入信号接近奈奎斯特(Nyquist)频率,即频率为 48.144 531 25 MHz 时,在同样的仿真环境下进行仿真后,得到的频谱图如图5所示.其中,无杂散动态范围(Spur-Free Dynamic Range,SFDR)为 75.879 dB,信号噪声失真比(Signal to Noise and Distortion Ratio,SNDR)为 61.37 dB ,有效位数(Effective Number Of Bit,ENOB)为 9.902 bit.为了验证ADC在Nyquist频带内的性能,文中在采样频率为 100 MS/s 、温度为27℃、工艺角为典型值(TT)的环境下,分别对频率从1 MHz到50 MHz的正弦波输入信号进行仿真.图6给出了ADC的SFDR和SNDR参数随输入信号频率的变化曲线.在低频输入时,SFDR较高; 而在高频输入时,SFDR较低.这是由于在低频时,动态因素所产生的谐波失真功率较小,而随着输入信号频率的升高,总谐波失真(Total Harmonic Distortion,THD)成为限制SFDR的主要因素.另外,在整个Nyquist频带内SNDR的变化比较小,基本保持不变.这是因为无论输入信号的频率有多大,量化噪声以及热噪声都是限制ADC的关键因素.表2列出了ADC在3种不同工艺角下,当采样频率为 100 MS/s,输入信号频率为 1.074 218 75 MHz,环境温度为27℃,工作电压为 1.8 V 时的动态性能,其中SNR(Signal to Noise Ratio)为信噪比.在工艺角为SS(高温、低压)的情况下,P沟道金属氧化物半导体(P-channel Metal Oxide Semiconductor,PMOS)晶体管和N沟道金属氧化物半导体(N-channel Metal Oxide Semiconductor,NMOS)晶体管的工作速度最慢,在一定程度上影响了ADC的性能参数,因此仿真得到的结果相对于FF(低温、高压)、TT工艺角会差一点.

图5 ADC在Nyquist输入频率下的快速傅里叶变换频谱图 图6 不同输入频率下的SNDR和SFDR参数

表2 不同工艺角下ADC的动态性能比较

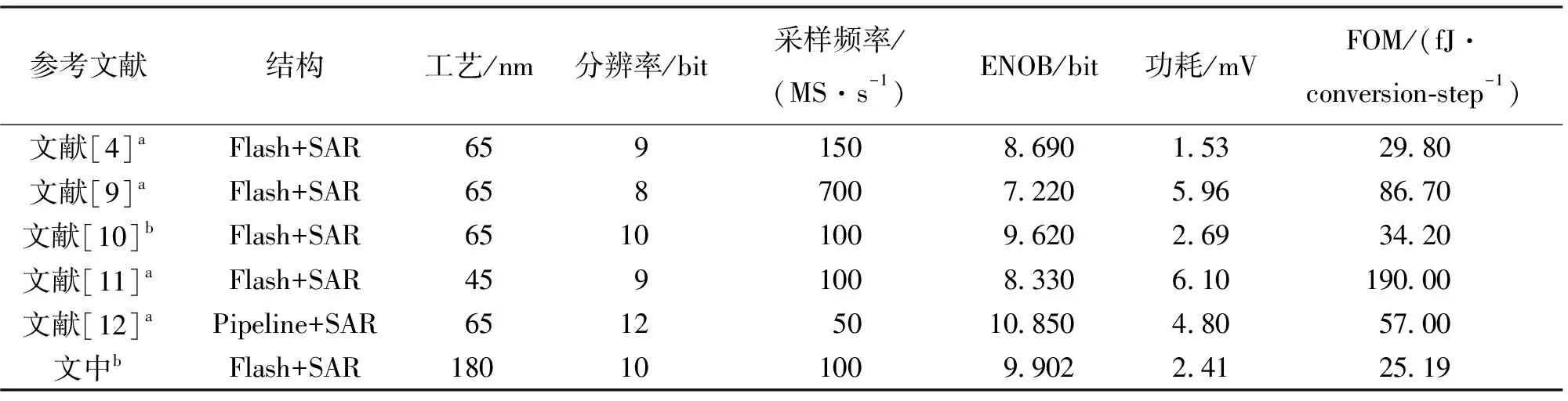

表3给出了文中设计的10 bit Flash-SAR混合型ADC与已发表的混合型ADC之间的性能比较.从表3的对比中可以看出,尽管文中所设计的混合型ADC采用的是相对落后的SMIC 0.18 μm 工艺,但相比于其他论文中采用更先进工艺所设计的ADC具有更好的性能,并且在功耗上也占有很大的优势.

表3 ADC的性能比较

注: 上标a表示测试结果;上标b表示仿真结果.

5 结 束 语

文中在SMIC 0.18 μm 1P6M CMOS混合信号工艺下,设计并实现了一个 10 bit 100 MS/s Flash-SAR混合型ADC.提出了一种新型的开关切换策略,从理论上分析了该策略相对于现存的开关切换策略具有更好的线性度,节省更多的功耗以及总电容数.同时,最后的仿真结果也证实了该策略的可行性.

[1] 曹超, 马瑞, 朱樟明, 等. 高精度SAR ADC非理想因素分析及校准方法[J]. 西安电子科技大学学报, 2015, 42(6): 61-65.

CAO Chao, MA Rui, ZHU Zhangming, et al. Analysis of Non-ideal Factors and Digital Calibration for High Resolution SAR ADCs[J]. Journal of Xidian University, 2015, 42(6): 61-65.

[2] LIM Y, FLYNN M P. A 1 mW 71.5 dB SNDR 50 MS/s 13 b Fully Differential Ring-amplifier-based SAR-assisted Pipeline ADC[C]//Proceedings of the 2015 IEEE International Solid-State Circuits Conference. Piscataway: IEEE. 2015: 458-459.

[3] HONG H K, KANG H W, JO D S, et al. A 2.6 b/Cycle-architecture-based 10 b 1 JGS/s 15.4 mW 4×-time-interleaved SAR ADC with a Multistep Hardware-retirement Technique[C]//Proceedings of the 2015 IEEE International Solid-State Circuits Conference. Piscataway: IEEE, 2015: 470-471.

[4] LIN Y Z, LIU C C, HUANG G Y, et al. A 9-bit 150-MS/s Subrange ADC Based on SAR Architecture in 90-nm CMOS[J]. IEEE Transactions on Circuits and Systems Ⅰ: Regular Papers, 2013, 60(3): 570-581.

[5] LIU C C, CHANG S J, HUANG G Y, et al. A 10 b 100 MS/s 1.13 mW SAR ADC with Binary-scaled Error Compensation[C]//Proceedings of the 2010 IEEE International Solid-State Circuits Conference. Piscataway: IEEE, 2010: 386-387.

[6] LIU C C, CHANG S J, HUANG G Y, et al. A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure[J]. IEEE Journal of Solid-State Circuits, 2010, 45(4): 731-740.

[7] HARIPRASATH V, GUERBER J, LEE S H, et al. Merged Capacitor Switching Based SAR ADC with Highest Switching Energy-efficiency[J]. Electronics Letters, 2010, 46(9): 620-621.

[8] HUANG G Y, CHANG S J, LIU C C, et al. 10-bit 30-MS/s SAR ADC Using a Switchback Switching Method[J]. IEEE Transactions on Very Large Scale Integration Systems, 2013, 21(3): 584-588.

[9] MURATORE D G, AKDIKMEN A, BONIZZONI E, et al. An 8-bit 0.7-GS/s Single Channel Flash-SAR ADC in 65-nm CMOS Technology[C]//Proceedings of the 2016 European Solid-State Circuits Conference. Washington: IEEE Computer Society, 2016: 421-424.

[10] WU S Y, DU L, JIANG M, et al. A 10-bit 100 MS/s Time Domain Flash-SAR ADC[C]//Proceedings of the 2014 IEEE International Conference on Electron Devices and Solid-State Circuits. Piscataway: IEEE, 2014: 7061088.

[11] CHO Y K, JUNG J H, LEE K C. A 9-bit 100-MS/s Flash-SAR ADC without Track-and-hold Circuits[C]//Proceedings of the 2012 International Symposium on Wireless Communication Systems. Washington: IEEE Computer Society, 2012: 880-884.

[12] KUPPAMBATTI J, KINGET P R. A Low Power Zero-crossing Pipeline-SAR Adc with On-chip Dynamically Loaded Pre-charged Reference[C]//Proceedings of the 2013 39th European Solid-State Circuits Conference. Washington: IEEE Computer Society, 2013: 113-116.