集成电路ESD防护浅析

郭昌宏,周金成,李习周,张易勒

(天水华天科技股份有限公司,甘肃 天水 741000)

静电是一种客观存在的自然现象,产生的方式多种,如接触、摩擦、电器间感应等。人体自身的动作或与其他物体的接触、分离、摩擦或感应等因素,能够产生几千伏甚至上万伏的静电。

两个电势不同的物体相接触会造成电荷在两个物体间的转移,直到二者电势相等,电荷分配完毕。当带有电荷的半导体器件上电的一刹那,电荷泄放通路形成瞬间高脉冲形成导电通路,器件引脚所吸收的高能脉冲损伤芯片。

1 电子行业的困扰

随着我国电子产业的迅速发展和技术水平不断提高,高分子材料、大规模IC、微电子器件广泛应用于各领域及电子产品中,静电放电(Electrostatic Discharge,ESD)造成的损伤给企业造成了重大的危害。因此,静电防护技术受到企业的普遍重视。ESD是造成所有电子元器件或IC系统过度电应力破坏的主要元凶。因为静电通常瞬间释放的电压非常高(超过几千伏),这种损伤是毁灭性和永久性的,会造成电路直接烧毁。所以预防静电损伤是所有IC设计和制造的头号难题。ESD现象存在集成电路芯片的制造、运输、使用过程中,芯片的外部环境或者内部结构积累一定量的电荷,这些积累的电荷会瞬间通过芯片的管脚进入集成电路内部,在集成电路内部的电流峰值可达到数安培,这个瞬态大电流足以将芯片烧毁,如图1所示。

图1 集成电路内部ESD失效SEM图像

1.1 ESD对IC的放电方式

根据ESD产生的机理及其对IC放电的不同方式,通常将静电放电分为三类模型。

1.1.1 人体模型

人体模型(Human Body Model,HBM)是目前最常见的模型,也是在产品的可靠性检验中一定要通过的检测项目。人体模型是指因人体上已积累了静电后接触芯片,静电会瞬间从芯片的某个端口进入芯片内部,再经由芯片的另一端口泄放至地,此放电会在几百纳秒的时间内产生数安培的瞬间电流,把芯片内的器件烧毁。一般人体模型ESD的防护级为2~4 kV。

1.1.2 机器模型(Machine Model,MM)

机器模型(Machine Model,MM)是当积累在机器金属臂上的静电接触芯片时有可能通过芯片的管脚瞬间泄放静电电流。机器放电模式的等效放电电阻(Resd)为 0 Ω,但其等效电容(Cesd)为200 pF。由于机器放电模式的等效电阻小,故其放电的过程更短,能在几纳秒到几十纳秒间产生数安培的瞬态电流。目前,机器模型及其测试标准由日本制定。

1.1.3 器件充电模型

器件充电模型(Charged Device Model,CDM)是芯片本身积累静电荷,当芯片管脚与地表接触的瞬间,芯片内部的静电会经管脚向外泄放电流。该模式放电的时间仅在几纳秒之内。芯片内部的静电会因芯片器件本身对地的等效电容而变,芯片摆放的角度以及芯片所用的封装形式都会造成不同的等效电容。

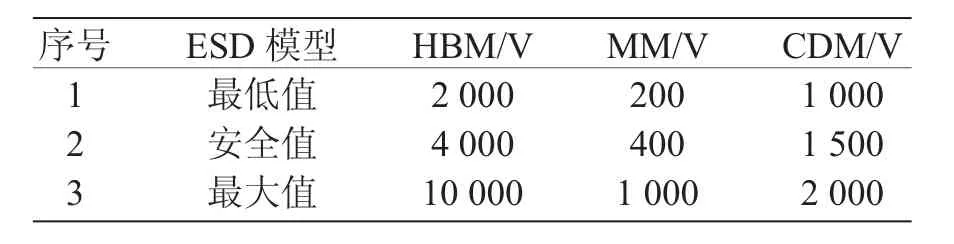

一般集成电路中ESD的规格如表1所示(“OK”为最低的要求)。

表1 ESD规格表

1.2 +ESD对集成电路损伤的表现

静电对IC的损伤主要表现为:芯片内热二次击穿、金属喷镀熔融、介质击穿、表面击穿、体积击穿、功能故障等。表面击穿损伤如图2所示。

图2 表面击穿示意图

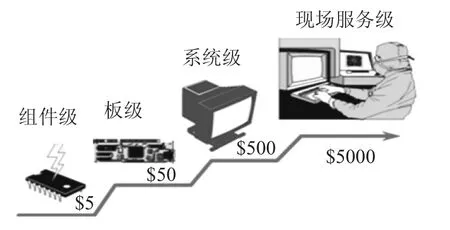

静电放电是电子产品质量最大的潜在杀手,静电防护也成为电子产品质量控制的重要内容。ESD损伤的成本在每个进程级,增加10倍,如图3所示。

图3 静电损伤成本示意图

集成电路制造技术已进入纳米时代,随着集成电路尺寸的减小,ESD问题越来越成为集成电路中最主要的可靠性问题。而国内外品牌手机使用时稳定性的差异也基本上反映了他们在静电防护及产品的防静电设计上的差异。

2 集成电路中ESD问题的解决途径

ESD保护一般通过两种途径来实现,第一种方法是避免ESD的发生;第二种方法则是通过芯片内或芯片外集成内部保护电路或专用ESD保护器件,从而避免ESD发生后将被保护器件损坏。

2.1 避免ESD的措施

静电放电防护电路是IC上专门用来做静电放电防护用的特殊电路,提供ESD电流泄放路径,以免ESD放电时电流流入IC内部电路而造成损伤。

2.1.1 接地

接地是避免ESD最基本也是最有效的方法。接地可为静电冲击提供良好的泄放通道,使带电体上积聚的静电荷得以顺利泄出,迅速导入地面,避免对敏感元件的放电,接地电阻应<10 Ω。将工作环境中的人员、设备通过不同的地线接地,该区域中的操作台面应该接地良好。静电接地适用于导静电材料和静电耗散材料,如胶皮接地。

2.1.2 湿度控制

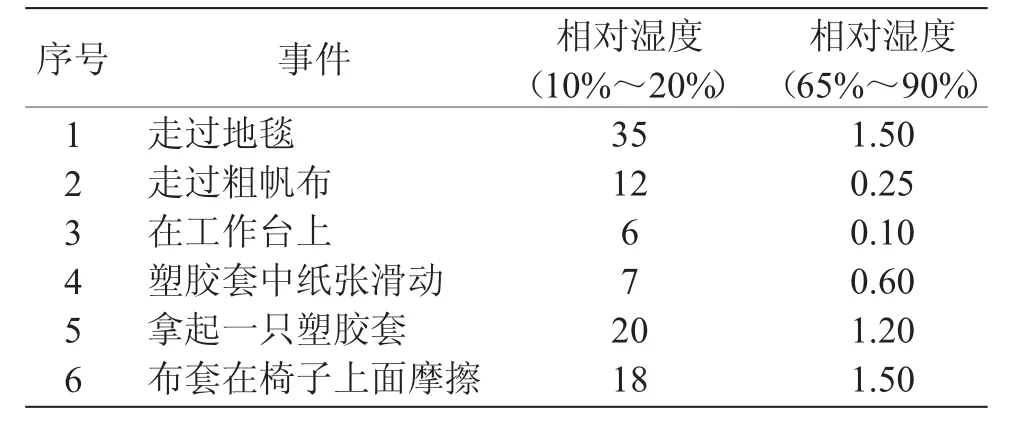

湿度是影响静电电荷积累的重要因素。增加环境湿度可提高非导体材料的表面电导率,使物体表面不易聚积静电。在静电危险场所,在工艺条件许可时,可以安装空调设备、喷雾器以提高空气的相对湿度消除静电。为使静电达到最佳的控制效果,必须使湿度保持在60%~70%以上。在允许的情况下湿度以不低于50%为宜。适当增加湿度可降低ESD电压,具体湿度如2表所示。

表2 操作人员工作时产生静电的典型数据kV

2.1.3 防静电腕带直接接触集成元器件的人员均应配戴防静电腕带,防静电腕带应与人体皮肤有良好接触,防静电腕带可以将人体上的静电释放掉。

2.1.4 包围隔离、静电屏蔽

为了防止静电电荷进入敏感电子器件造成损伤,需要用抗静电材料包装,并用静电屏蔽袋作为保护。一切贮存、周转集成元器件的容器(元器件袋、转运箱、印制板架、元器件存放盒等)应具备静电防护性能。仓库的存放架也应接地,以免聚集大量静电损坏集成元器件。而在静电敏感区域工作的人员,则还需要穿着静电服。静电屏蔽适用于高压电源的静电屏蔽、某些对静电极敏感电路的屏蔽,从而避免静电场对ESDS器件和ESDS组件的感应和静电放电产生的宽频带干扰。

2.1.5 静电中和

静电中和是利用外界因素将空气电离,利用异性电荷相吸的原理,异号电荷与静电源上的电荷中和,同号电荷导向大地,从而消除静电源上积累的静电。离子中和绝缘体往往是易产生静电的,对绝缘体静电的消除,用接地方法是无效的,通常采用的方法是离子中和,即在工作环境中使用离子风机,离子气枪。

2.2 设计ESD保护器件

避免ESD的措施一般应用于产品交付客户之前,对于终端用户显然不合适。因此,需要在电子产品的设计时加上ESD防护单元,这个防护单元可以在芯片外加上专用ESD防护器件,也可以在芯片内部加上ESD防护单元。

2.2.1 芯片内部ESD防护

ESD防护设计的关键在于在芯片内部电路的I/O端口集成片上(on-Chip)ESD防护单元。芯片内部ESD防护就是在芯片里集成ESD防护单元,当静电信号到来的时候保护内部电路免遭破坏,相比于芯片外ESD防护电路,其可直接显著增强ESD防护能力,节省板级空间,减少系统成本并降低设计与布线的复杂度。最经济有效的方法是合理设计芯片上ESD防护单元,这个单元必须能够有效地保护内部电路抵御ESD冲击。

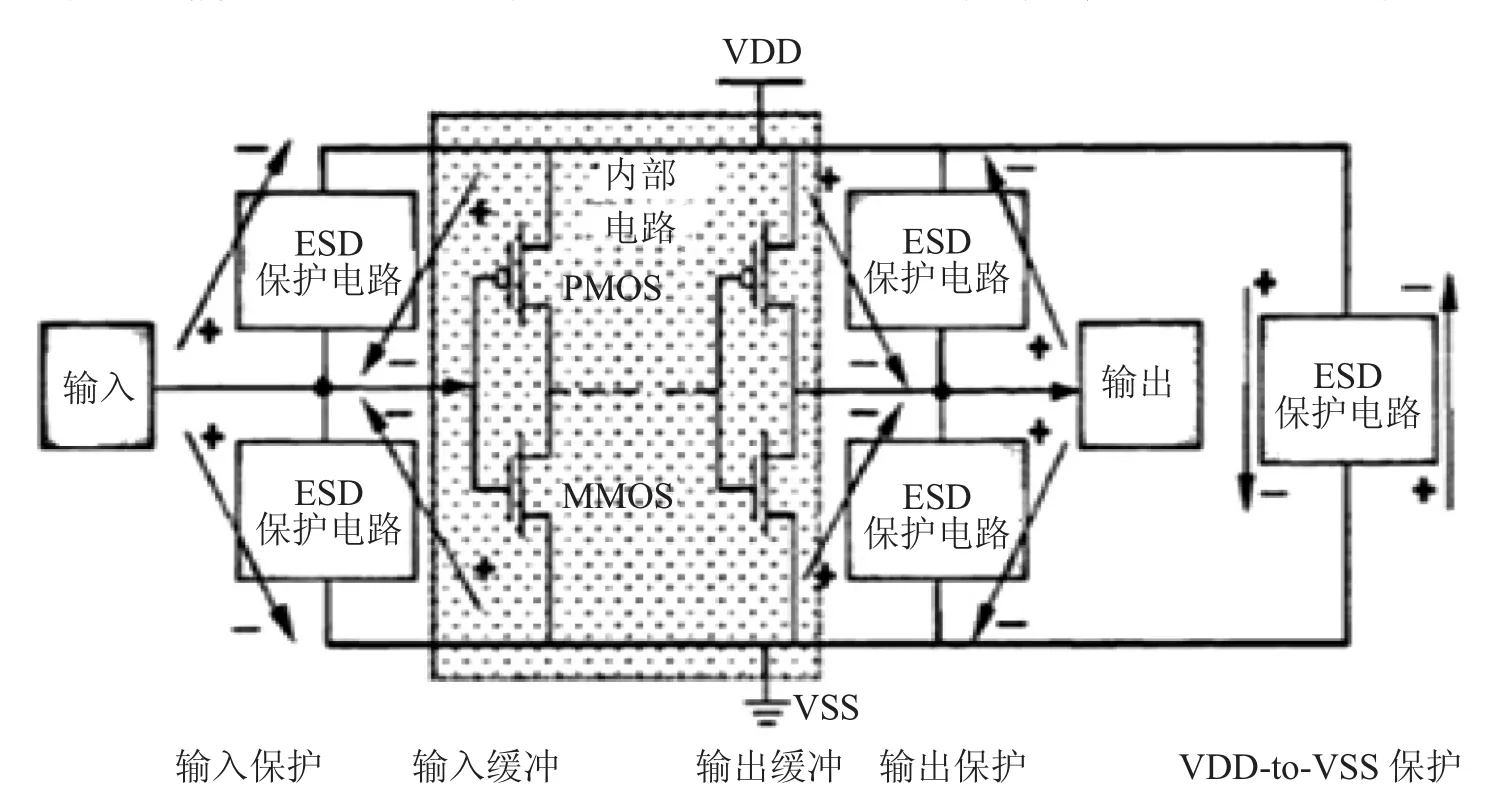

人体放电模型的ESD来自外界,所以ESD防护电路都是做在引线PAD的旁边。在输出PAD,其输出极大尺寸的PMOS及NMOS元件本身可当作ESD防护元件来用。输入PAD,因CMOS电路的输入PAD一般都是连接到MOS元件的栅极(gate),栅极氧化层容易被ESD所击穿,因此在输入极的旁边会做一组ESD防护电路来保护输入级的元件。在VDD pad与VSS pad的旁边也要做ESD防护电路,因为VDD与VSS脚之间也可能遭受ESD的放电。ESD防护电路的安排必须全方位地考虑到ESD测试的各种组合。ESD防护网络如图4所示。

图4 全芯片ESD防护网络

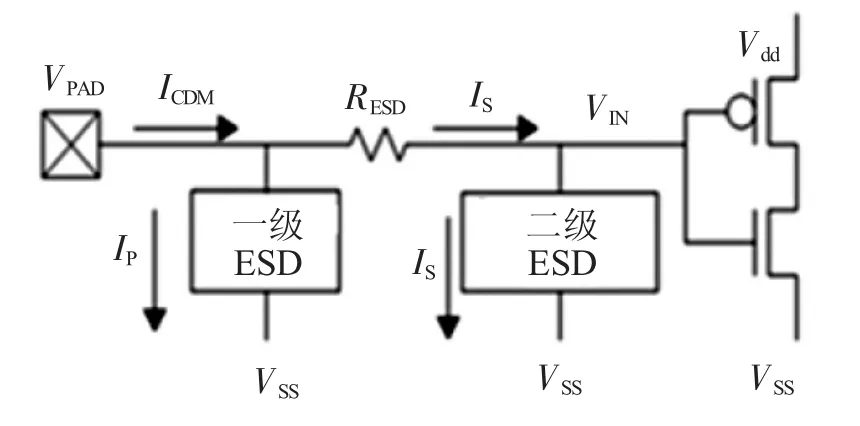

2.2.2 ESD防护电路

ESD防护电路是为了防护ESD而加入,在IC正常工作情形下,该ESD防护电路不起作用。因此加入ESD防护电路时,要提供有效快速的ESD放电回路,抗静电结构自身也不能被损坏。当电路在正常工作时,抗静电结构是不工作的,其负作用(例如输入延迟)必须在可以接受的范围内尽可能地小,应防止ESD结构部分发生闩锁。芯片内部ESD防护电路如图5所示。

图5 芯片内部ESD防护电路图

2.2 芯片外ESD防护

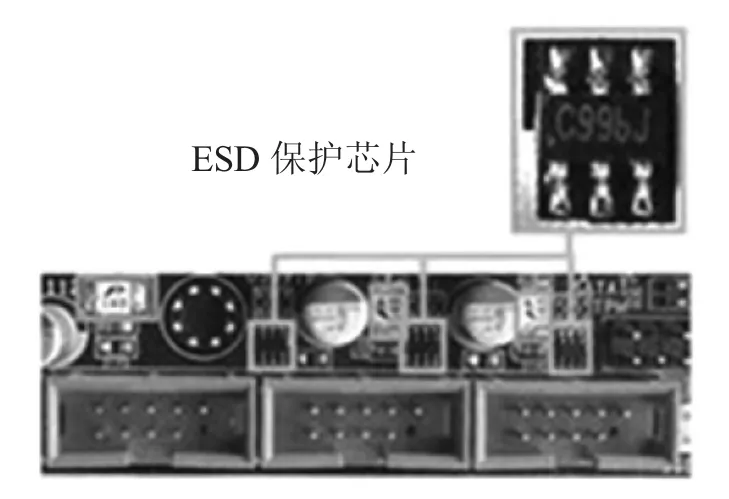

由于芯片上ESD保护电路能力有限,为了保证整个系统有较好的ESD防护能力,外部ESD保护器件是必不可少的。芯片外ESD保护器件常见的有陶瓷电容、齐纳二极管、肖特基二极管、MLV(Multi-Layer Varistor,多层变阻器)和 TVS(Transient Voltage Suppresser瞬态电压抑制器)。无ESD保护的芯片如图6所示,有ESD保护的芯片如图7所示。

图6 无ESD保护芯片图

图7 有ESD保护芯片图

2.2.1 陶瓷电容

在大功率、高压领域使用的高压陶瓷电容器,具有小型、高耐压和频率特性好等特点。随着材料、电极和制造技术的进步,高压陶瓷电容器的发展有了长足的进展,并取得广泛应用。高压陶瓷电容器已成为大功率高压电子产品不可缺少的元件之一。

目前,最先进的陶瓷电容的ESD保护能力是传统产品的3倍,CeraPad陶瓷基板的ESD保护能力可达25 kV。

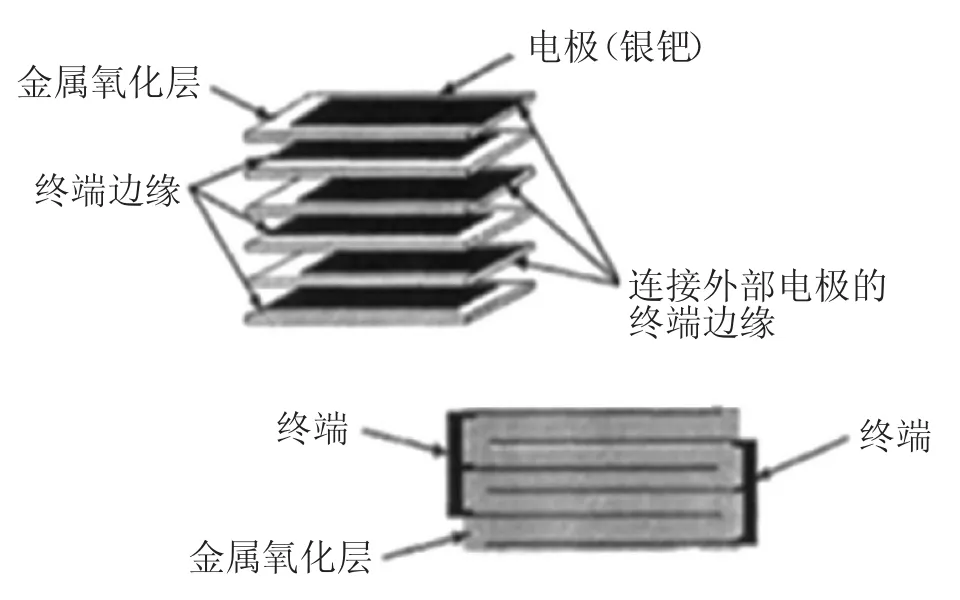

2.2.2 肖特基二极管

MLV(多层变阻器)是一种基于ZnO压敏陶瓷材料,其工作原理是利用压敏电阻的非线性特性,当过电压出现在压敏电阻的两端时,压敏电阻可以将电压钳位到一个相对固定的电压值,从而实现对后级电路的保护。MLV的内部结构如图8所示。

图8 MLV的内部结构示意图

2.2.3 TVS

TVS(Transient Voltage Suppresser瞬态电压抑制器)通常并联于被保护电路,当瞬态电压超过电路正常工作电压时,二极管发生雪崩,为瞬态电流提供通路,使内部电路免遭超额电压的击穿或超额电流的过热烧毁。TVS的内部结构如图9所示。

图9 TVS的内部结构示意图

2.2.4 PCB布线

PCB布线是ESD防护的一个关键要素,PCB设计中,采用瞬态电压抑制器(TVS)二极管来抑制因ESD放电产生的直接电荷注入,PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。需注意电路环路、电路连线长度、低电荷注入,避免在PCB边缘安排重要的信号线,如时钟和复位信号等,将PCB上未使用部分设置为接地。

3 结束语

ESD是一个“看似很小的大问题”,一个产品ESD防护的好坏直接影响到该产品的良品率和寿命。从目前情况看,芯片上集成电路ESD防护电路的难度相当大;工艺的进步使集成电路栅极氧化层越来越薄,集成电路自身的ESD防护能力降低,先进工艺使传统的芯片上ESD防护措施效果减弱。芯片上ESD防护单元的设计,对电子产品抗击ESD伤害有着至关重要的作用,是提高集成电路自身抗静电的有效方法。

[1] 朱旭强.集成电路片上ESD防护器件的设计与分析[D].成都:电子科技大学,2011.

[2] 苗萌.ESD防护设计的若干问题研究[D].杭州:浙江大学,2012.

[3] 李明亮.集成电路典型工艺下I/O电路及片上ESD防护设计研究[D].杭州:浙江大学,2011.