一种基于片同步技术的高速ADC与FPGA互连方法

韩 琦 葛 飞 梁圣杰 张之卓

北京航天自动控制研究所,北京100854

在数字中频接收机中,为适应电子设备小型化、低功耗设计且具有较宽的频带覆盖和较高灵敏度的需求,系统经常使用单片多通道的高速ADC组建多通道采样处理平台。如AD公司的AD9653采样器为4通道16位125Msps高速同步采样器,可适用于多通道同步采集系统的设计,其中芯片接口使用8对高速串行差分线传输采样数据,每对差分线最高传输速率高达1Gbps。在如此高的数据传输速率情况下,即使保证ADC各通道串行数据与随路采样时钟的走线严格等长,采用传统的ADC与FPGA数据接口互连方式也将无法实现稳定可靠的数据接收。基于上述原因,Xilinx公司在Vertex4系列FPGA之后引入了片同步技术(ChipSync),通过采用此技术在FPGA内部设计同步调整模块,可实现调节采样时钟处在数据的最佳采样位置,以保证数据采样的同步性和稳定性,从而解决高速ADC和FPGA之间高速数据传输的问题。

文献[1-2]提出对ADC输入的串行数据进行延迟调整以达到最佳采样位置的方法,但在ADC进入输出采样数据模式之前,需要事先发送一连串的训练序列用于对比判决,以此控制串行数据位延迟调整至采样时钟的最佳采样位置,而控制输出发送训练序列的格式和输出采样数据之间的模式切换,需要FPGA增加SPI接口的控制逻辑对ADC进行发送命令来完成,由此增加了FPGA的逻辑复杂性。

提出了一种在FPGA设计中对ADC输入的采样位时钟进行自适应延迟调整来补偿采样位时钟的内部走线延时,将采样时钟调节至数据的最佳采样位置的方式,不需要对ADC输出发送训练序列模式和输出采样数据模式的切换控制,去除了FPGA与ADC之间的SPI接口数据交互,大大降低了FPGA的设计复杂度,提高了系统可靠性。

1 高速ADC和FPGA互连设计整体方案

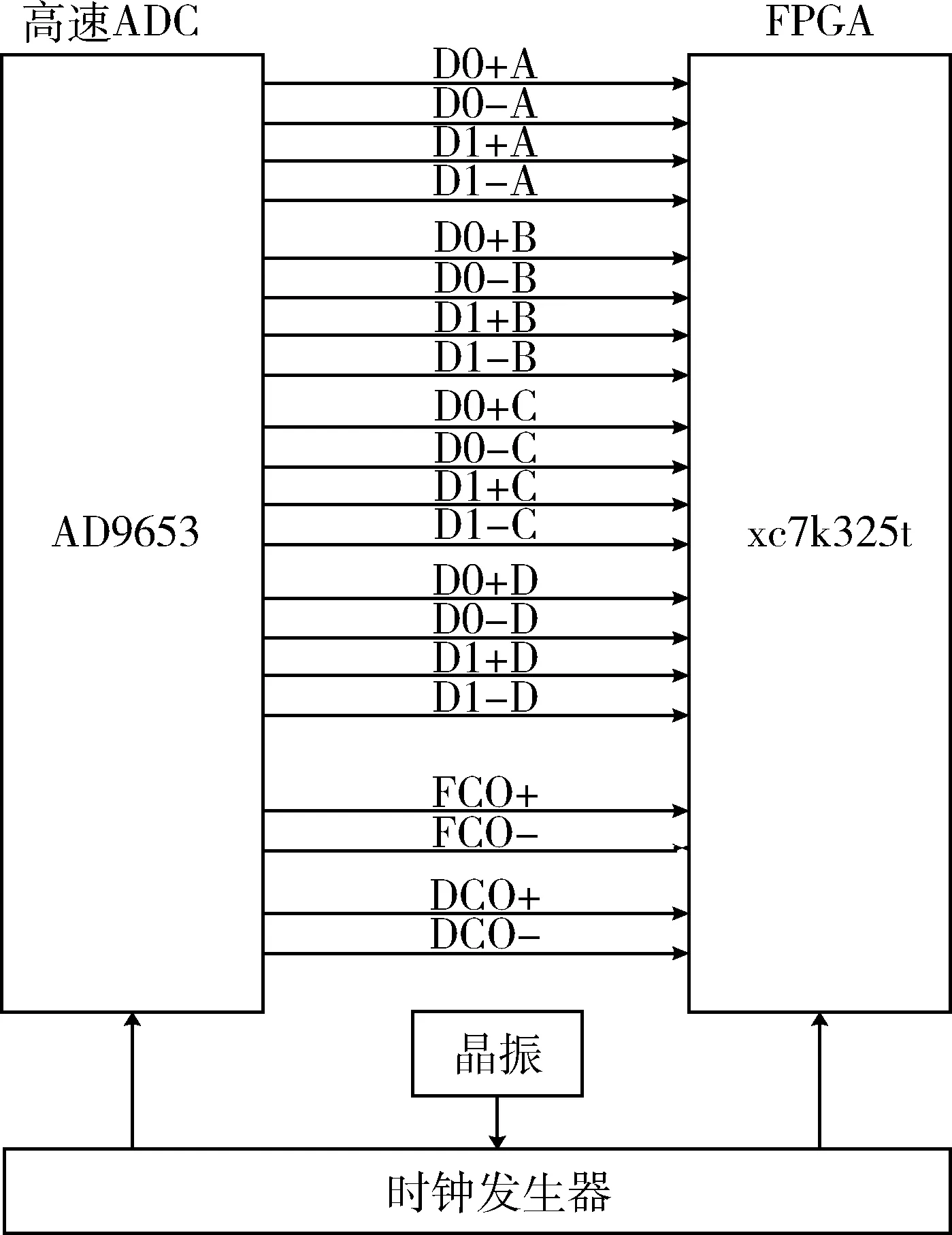

本文的四通道高速ADC和FPGA互连结构框图如图1所示。其中FPGA采用Xilinx公司的xc7k325t,使用内置的SERDES收发器对其进行高速解串处理。高速ADC采用AD9653,采样数据接口格式为二进制补码格式,采用16Bit DDR,双通道,1x帧格式逐字节模式。具体处理过程为:AD9653对四路模拟信号进行模数转换,再分别将对应通道采样得到的16bit数据转换为2对串行差分信号(例:A通道2对差分信号为D0+A/D0-A,D1+A/D1-A),采用源同步的方式连同位时钟(DCO+/-)、帧时钟(FCO+/-)一起传输给FPGA,ADC接口输出的时序关系如图2所示[3];在FPGA内部按照要求使用内置的SERDES收发器完成高速解串、数据帧对齐后得到采样后的16bit并行数据进行后续的数据处理。

图1 四通道高速ADC和FPGA互连结构框图

图2 AD9653的输出时序图

通过图2可知AD9653输出的位时钟DCO+/-与串行数据D0+/-、D1+/-,帧时钟FCO+/-之间存在固定的相位关系,只要在硬件设计上保证各路信号的走线等长,该相位关系即可保证位时钟所处相位为最佳采样点。但是由于位时钟DCO作为串行数据、帧时钟之SERDES收发器的采样时钟,FPGA内部的走线延时将导致到达各SERDES收发器的相位与串行数据、帧时钟之间的相位关系发生变化,此时通过位时钟DCO对串行数据直接采样,将会产生误码。本文采用基于片同步技术对采样位时钟进行自适应调整至数据的最佳采样点来可靠准确地采样数据。

2 基于片同步的互连设计方法

2.1 片同步设计整体方案

图3为基于片同步设计的FPGA实现方案,首先通过位时钟自适应调整模块调节位时钟延迟,使得连接至各ISERDES采样时钟的相位与输入的DCO+/-一致,此刻采样点处于串行数据位和帧时钟的采样中心,为最佳采样位置。然后再采用数据帧对齐调整模块对帧时钟采样获得的并行数据进行判断,产生BITSLIP信号控制各ISERDES进行移位操作,直至帧时钟采样输出期望的并行数据后,完成数据帧对齐操作,此时即完成了各数据通道的并行数据提取工作。

图3 片同步设计整体方案图

2.2 片同步技术[4]

片同步(ChipSync)是Xilinx公司命名的一种同步技术,其目的是为FPGA提供一个高速的源同步数据总线接口。主要由IODELAY延时调整模块、ISERDES解串模块、OSDRDES并串转换模块及时钟网络组成。本文采用的方法主要通过IDELAY延时调整模块控制精确延时,实现采样位时钟的动态调整,确定串行数据的最佳采样位置,然后通过ISERDES解串模块对高速串行数据进行稳定可靠的采样。

IDELAY为内嵌32级每级78ps的可调延时器(IDELAYCTRL的参考时钟为200MHz),可通过CE和INC信号来控制数据延时的增加和减小。

ISERDES为高速解串模块,支持SDR、DDR两种采样模式。在SDR模式下,支持2、3、4、5、6、7、8位宽的串并转换,在DDR模式下,支持4、6、8位宽的串并转换。通过级联可以将串并转换器扩展到10位和14位宽。本方法中串行数据和帧时钟对应的ISERDES选择1:8的串并转换(DDR模式)。同时ISERDES的BITSLIP信号负责对ISERDES的接收数据进行移位操作,用于数据位顺序的调整。

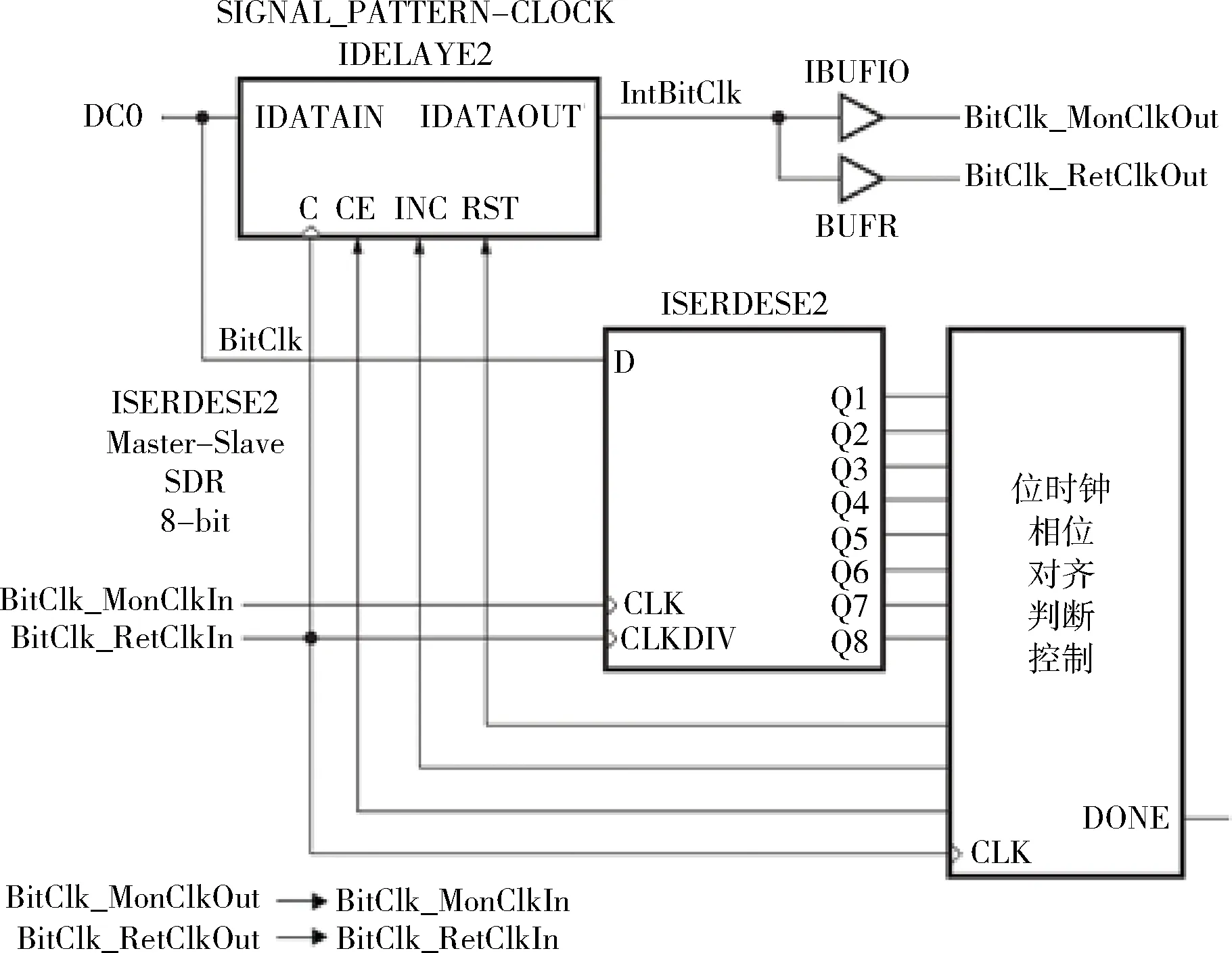

2.3 位时钟延迟自适应调整

由于数据位采样为DDR上下沿采样模式,故位时钟自适应调整的过程只需要将连接至串行数据位和帧时钟的采样时钟,通过IDELAY延时模块实时调整至位时钟DCO的跳变沿即可保证ISERDES的采样时钟与数据的相位关系与输入一致,如图4所示。位时钟延迟自适应调整的处理方法是:

图4 位时钟延迟自适应调整原理框图

将差分转单端后的位时钟DCO连接IDELAY延时调整模块进行相应级数的延迟,调节级数由位时钟相位对齐判断控制输出CE和INC信号进行控制。

将IDELAY输出的延时时钟IntBitClk分别经过BUFIO和BUFR(分频参数为4)驱动作为ISERDES的采样时钟CLK和四分频时钟CLKDIV。其中BUFIO为IO时钟驱动,BUFR为区域时钟驱动,四分频时钟CLKDIV为并行化数据的速度。

将差分转单端后的位时钟DCO作为串行数据提供给ISERDES进行采样,采样时钟为经过延时处理和BUFIO驱动后的同频时钟,位时钟对应的ISERDES选择1:8的串并转换(SDR模式)。

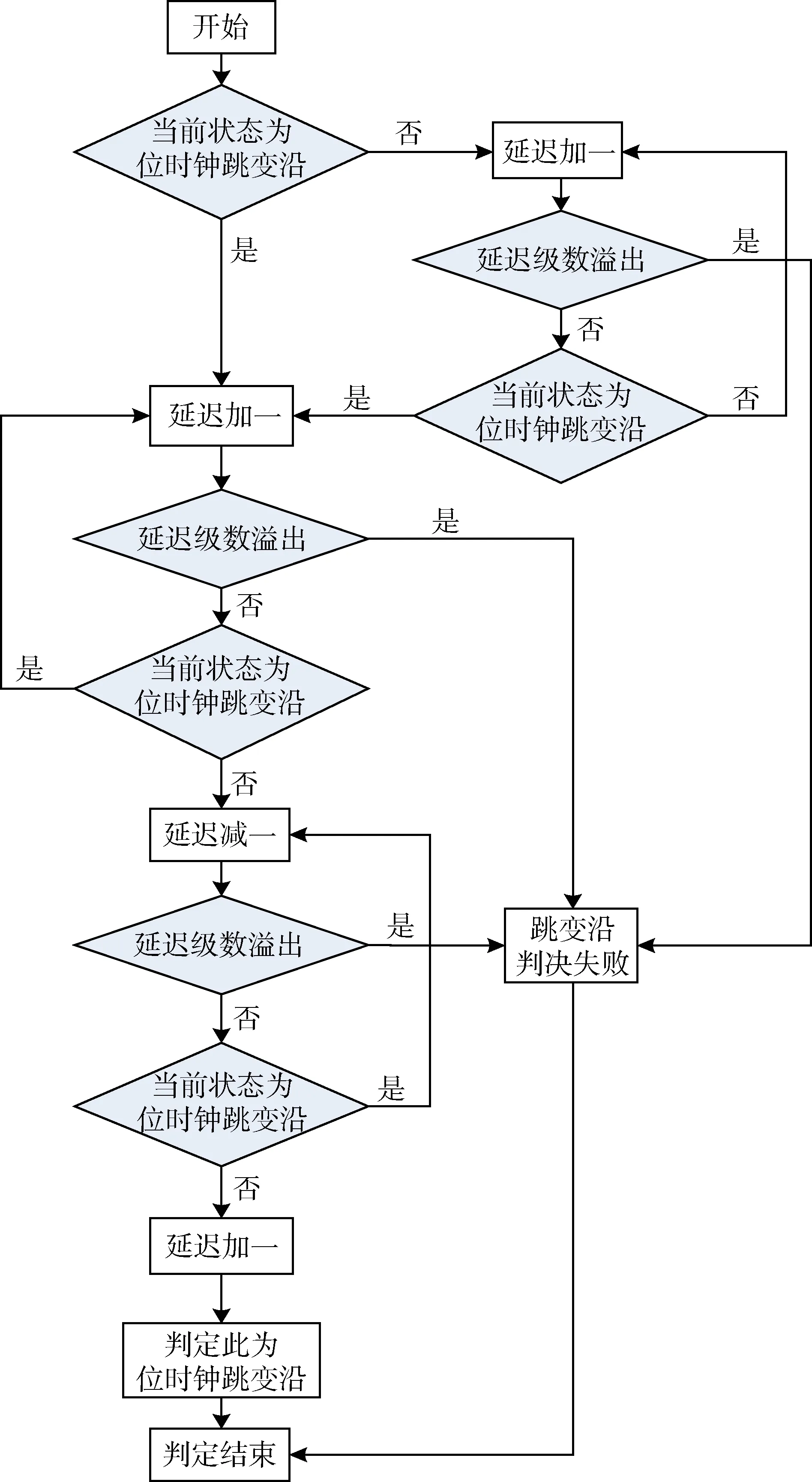

位时钟相位对齐判断控制负责对ISERDES的并行数据(Q1~Q8)进行判断,寻找位时钟的跳变沿。处理流程如图5所示。

图5 位时钟相位对齐判断控制处理流程图

位时钟跳变沿的判断依据为ISERDES上一次采样的并行数据和当前并行数据结果不一致,则当前设置的IDELAY延迟采样时钟与输入的位时钟跳变沿对齐。通过IDELAY延时调整补偿了FPGA内部位时钟的走线延时,使之与AD9653输出数据相位关系保持一致,保证了采样时钟处于数据采样窗口的最佳位置。另外IDELAY的延迟级数为32,需要对延迟级数是否溢出进行判断,当延时级数超过32时表明由于位时钟跳变沿速率不高,IDELAY在整个延迟周期都无法找到位时钟的跳变沿,此时跳变沿判定失败。

2.4 数据帧对齐调整

位时钟延时自适应调整负责完成串行数据和帧时钟的ISERDES采样位时钟与输入位时钟相位对齐,但只能保证串行数据被位时钟正确采样,而串并转换后的并行数据顺序不确定,将有8个组合。为了得到正确顺序下的并行数据流,需要进行数据帧对齐调整。数据帧对齐调整采用对帧时钟ISERDES采样并行数据进行判断,通过调整串行数据和帧时钟ISERDES的BITSLIP,当帧时钟ISERDES采样得到的并行数据与期望的数字序列“00001111”相同时,表明此时数据帧输出顺序正确,即完成了数据帧对齐工作,否则产生一个并行化数据时钟宽度的BITSLIP控制ISERDES的移位操作,进行下一次的判断操作。

3 仿真与板级验证

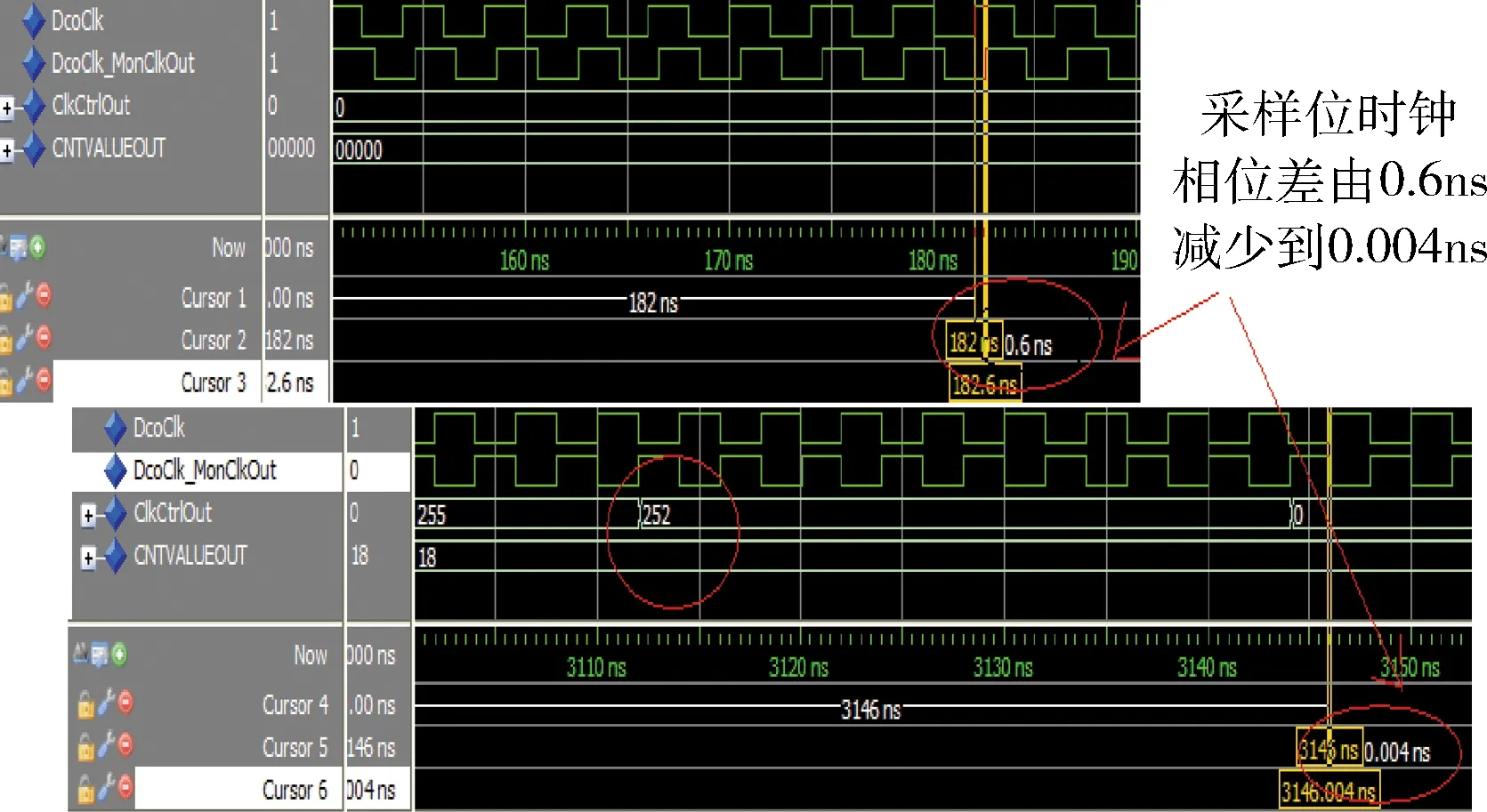

高速接口的FPGA程序是在Xilinx ISE14.7编译环境下实现的,通过编写测试激励文件在Questa Sim 10.0a软件下进行了仿真。如图6所示。经过3146ns,通过IDELAY延时模块18级延时调整后,ISERDES输出的并行数据发生变化,采样位时钟DcoClk_MonClkOut与端口输入位时钟DcoClk的相位差由0.6ns减小到0.004ns,实现了位时钟的自适应对准。其中,CNTVALUEOUT为IDELAY延时模块的延时阶数;ClkCtrlOut为ISERDES采样得到的并行数据。

图6 采样位时钟相位调整验证仿真图

使用信号发生器产生正弦信号进行板级测试,采样频率为125MHz,双线传输,单通道数据率为2Gb/s(125M*16bit)。使用ChipScope工具抓取位时钟的自适应对准过程和采样后的并行数据结果。

位时钟的自适应对准过程板级测试图如图7所示,在IDELAY延时模块完成4级延时调整后(CNTVALUEOUT为x“04”),位时钟DCO采样ISERDES输出的并行数据值ClkCtrlOut发生跳变(由x“FF”变为x“C0”,最后为x“00”),此时位时钟完成自适应对准,IDELAY延时模块固定在4级延时值上,开始进行后面的数据帧对齐调整和中频采样数据工作。

图7 位时钟的自适应对准过程板级测试图

图8为完成数据帧对齐调整对准后对正弦信号的实时采样数据波形图,横坐标为采样点数,纵坐标为数值。输入波形与输出波形一致,完成了对本文采用方法的正确性验证。

图8 采样数据波形图

4 结论

针对多通道的高速ADC与FPGA互连传输的要求,本文提出通过FPGA的片同步技术对位时钟延时进行自适应调整来解决FPGA内部走线延时带来的数据高速采样不稳定问题,与通过对数据位进行延迟调整的方式,降低了FPGA的逻辑复杂度。测试结果表明该方法可满足高速数据传输的要求,已在实际工程中得以应用。该方法也可作为其他点对点高速数据传输系统设计的参考。

参 考 文 献

[1] 顾峰, 吕余清. 应用源同步技术实现高速ADC与FPGA互连[J].电子技术, 2016,10:30-33.(Gu Feng, Lv Yuqing. Implementing High-speed ADC and FPGA Communication Based on Source Synchronization Technology [J]. Electronic Technology, 2016,10:30-33.)

[2] 屈超. 多通道ADC的高速接口设计[J].无线电通信技术, 2013,39(3):76-78.(Qu Chao. Design on Multichannel ADC High-speed Interface[J]. Radio Communications Technology, 2013,39(3):76-78.)

[3] Analog Devices. AD9653[EB/OL]. http://www.analog.com/media/en/technical-documentation/data-sheets/AD9653.pdf.

[4] Xilinx,7 Series FPGAs SelectIO Resources User Guide[EB/OL]. http://www.xilinx.com/support/documentation/user_guides/ug471.pdf.