基于FPGA的多通道实时地震勘探采集系统设计

李科 陈紫强 谢跃雷

摘 要: 针对目前地震勘探采集系统通道数少、实时性差,造成地质勘探工作效率低和勘探成本增加的问题,设计一款基于FPGA的多通道实时地震勘探采集系统,可实现地震勘探中地震波信号的48通道实时采集。该系统以FPGA为主控核心,6块8通道24位高动态范围的Δ?Σ型ADC芯片对地震波信号进行多通道采集,在采集过程中,利用IP核控制2 Gb的高速DDRⅡ SDRAM存储器对采集数据实时存储,采集完成通过RS 485串口通信实现远距离数据传输。实验测试结果表明,该地震勘探系统具备48通道实时采集能力,具有存储容量大、实时性好、系统稳定的特点。

关键词: FPGA; DDRⅡ SDRAM; 地震勘探; 远距离数据传输; 多通道采集; 实时存储

中图分类号: TN919?34; TP274.2 文献标识码: A 文章编号: 1004?373X(2018)09?0024?07

Abstract: Since the defects (few channels and poor real?time performance) of the current seismic exploration acquisition system result in low?efficiency geological exploration and increase of the exploration cost, a multi?channel real?time seismic exploration acquisition system based on FPGA is designed, which can realize 48?channel real?time acquisition of seismic wave signals in seismic exploration. In the system, the FPGA is taken as its main control core, and six 8?channel 24?bit Δ?Σ type ADC chips with high dynamic range is used for multi?channel acquisition of seismic wave signals. During the acquisition process, the IP core is used to control the 2 Gb high?speed DDRⅡ SDRAM memory for the acquired data real?time storage. The long?distance data transmission is realized through RS 485 serial port communication after data acquisition. The experimental test results show that the seismic exploration system has the 48?channel real?time acquisition capability, and the characteristics of large storage capacity, high real?time performance and perfect stability.

Keywords: FPGA; DDRⅡ SDRAM; seismic exploration; remote data transmission; multi?channel acquisition; real?time storage

0 引 言

地质勘探目前最常用的方法之一是地震勘探[1]。它的基本原理是采用人工地震在勘探地质中产生的振动[2],根据勘探设计要求在离激发点不同距离处布置传感器(地震检波器)接收振动产生的地震波信号,将接收到的信号进行解释、处理,根据信号的振幅、频率、速度等信息反演出勘探地质的形态、构造和属性等,從而达到地质勘探的目的,在煤田勘探、矿物勘探、石油勘探中有着广泛应用。地震勘探采集系统的作用就是在地震勘探中对地震检波器接收到的地震波信号进行采集存储和传输。

由于地震勘探的工作面广,放置的地震检波器数量多,勘探信号的数据量大,因此,对地震勘探采集系统的采集通道数、实时处理速度和存储深度要求高。传统的地震勘探采集系统主要采用单片机或数字信号处理器(DSP)为主控核心[3],TF卡或者FLASH和SDRAM芯片为存储器。由于单片机本身处理速度和执行指令周期的影响,其工作频率较低,DSP虽然处理数据速度快,但成本较高,对外部高速存储器控制复杂不易实现,而TF卡或FLASH和SDRAM芯片作为存储器,其存储速度或存储深度有限。因此,传统的地震勘探采集系统仅做到4通道或8通道的信号采集,在进行更多通道的信号采集时,需要多个采集系统同时工作,增加了勘探复杂度,降低了工作效率,造成勘探成本的增加。随着电子技术的发展,高速、大容量的存储芯片和控制灵活、工作频率高的现场可编程门阵列(Field?Programmable Gate Array,FPGA)器件的出现,为多通道实时地震勘探采集系统的实现提供了新途径[4]。

本系统采用Altera公司的Cyclone IV FPGA EP4CE30F23I7[5]为主控核心,128M[×]16 bit的第二代双倍数据率同步动态随机存取存储器(Double?Data?Rate Two Synchronous Dynamic Random Access Memory,DDRⅡ SDRAM)作为高速存储器,结合6块24位的8通道模数转换(Analog?to?Digital Converter,ADC)采集芯片和RS 485串口通信,实现48通道实时地震勘探采集系统设计,提高勘探工作效率,降低勘探成本。

1 系统硬件设计

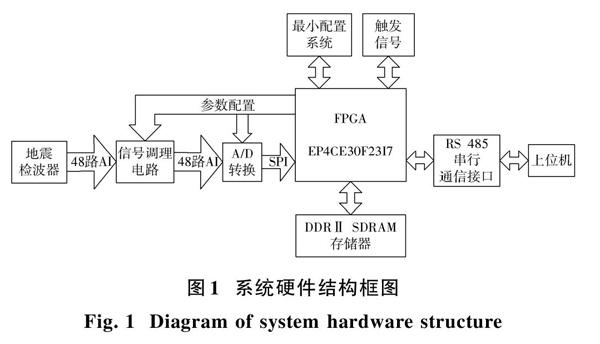

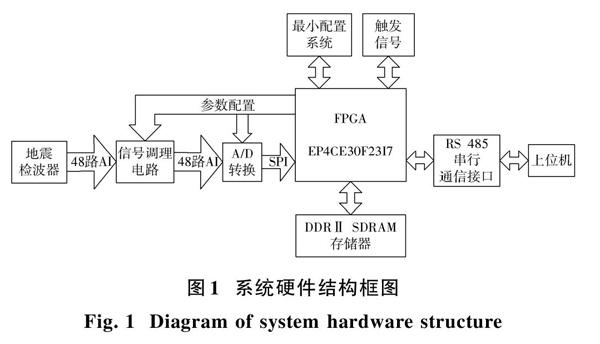

本系统采用“FPGA+DDRⅡ SDRAM+ADC+RS 485串口”的硬件系统结构,具体结构框图如图1所示。系统的硬件结构采用模块化设计,主要功能模块包括:FPGA控制模块、信号调理电路模块、ADC采集模块、DDRⅡ SDRAM存储模块、RS 485串行通信模块等。其中FPGA控制模块是实现信号采集和数据传输的控制通道。

FPGA首先通过RS 485接口采用串行通信协议从上位机获得信号调理电路的放大倍数及ADC采集通道数、ADC采样率、ADC采样时间等配置数据,对信号调理电路模块和ADC采集模块进行配置,同时对DDRⅡ SDRAM控制器进行初始化,进入采集准备状态。触发信号到达后,48个地震检波器接收到的地震波信号进入48路的信号调理电路,调理电路的输出接到6块8通道的ADC差分信号输入端,FPGA控制ADC采集模块进行数据采集,在每个采样点转换完成后,在采样间隔时间里,通过SPI接口协议读出ADC采集数据,存储到DDRⅡ SDRAM中,实现实时采集存储。采集完成后,从DDRⅡ SDRAM中读出所有采集数据,通过RS 485总线上传到上位机。FPGA为整个系统数据采集、存储、传输的控制核心。

1.1 信号调理与ADC采集

1.1.1 信号调理电路

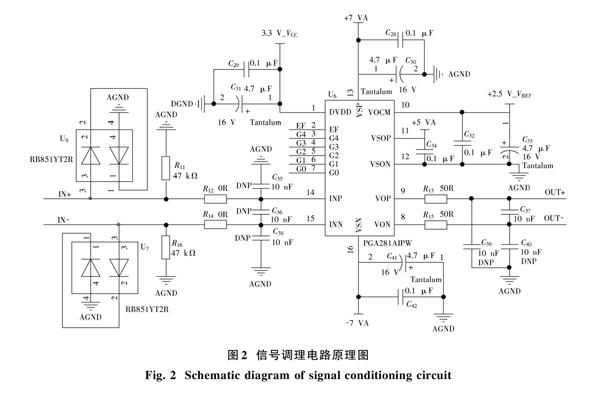

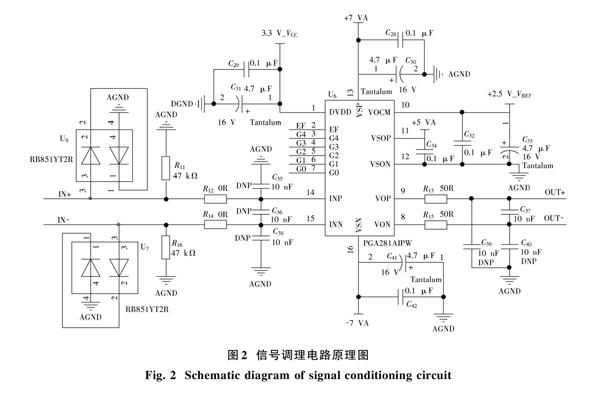

为了将地震检波器接收到的地震波信号转换为能被ADC采集识别的标准信号,在地震检波器和ADC采集模块之间增加信号调理电路,电路原理图如图2所示。

信号调理电路分为两级:第一级为由大于1 GΩ输入阻抗的低噪低零漂可编程放大器PGA281组成的程控放大电路;第二级为RC组成的低通滤波电路,滤除高频干扰信号。PGA281采用数控增益设计,通过控制其G[0:4]管脚实现0.125~128倍增益,然而增益太高会增加前置放大的失真,本地震勘探系统主要选取4~16倍。在PGA281的差分输入端增加肖特基稳压二极管设计,保护其输入管脚不被击穿。

1.1.2 ADC采集电路

地震勘探中对地震勘探采集系统都要求具有较高的动态范围[6],因此,本系统选用高精度、高信噪比的24 bit ADC采集芯片ADS1278[7]进行数据采集。ADS1278在满足高动态范围的同时,还具有8个差分模拟信号输入通道,在其同步管脚SYNC#的控制下,各个通道实现μs级同步采集,达到地震勘探各个通道μs级同步采集要求,并且各个通道支持独立选通,可根据勘探需求设置PWDN#[1?8]的值而变化采集通道数。ADS1278工作在高精度模式下,具有高達111 dB的信噪比,最高采样率达到52 kS/s,满足地震勘探中高达48 kS/s采样率的需求,在此工作模式下,ADS1278的采样率为其主时钟频率的[1512]。另外,ADS1278支持信号线少、协议简单的SPI接口协议进行数据传输,传输速率由FPGA控制,其值小于ADC主时钟频率。

整个信号调理及ADC采集电路采用平衡式设计,并对数字地与模拟地进行电磁隔离,PCB布局远离系统电源等噪声源模块,PCB布线采用等长布线。

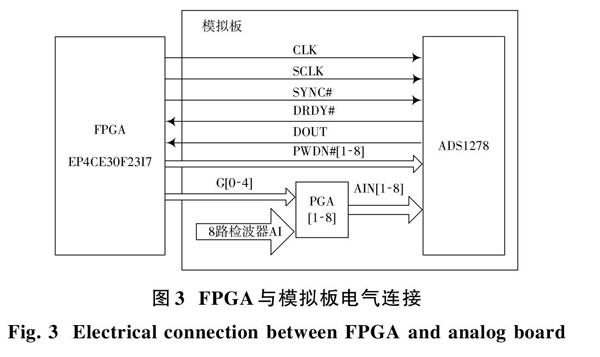

本系统采用6片ADC采集芯片,每片采集芯片有8个通道,实现48通道地震波信号的采集。鉴于FPGA灵活精准的并行执行结构和丰富的管脚资源,设计6块模拟板作为信号采集板与FPGA进行并行连接,每块模拟板具有一个ADC采集电路及8个信号调理电路,在FPGA并行控制下每块模拟板同时工作,实现48通道间ns级同步采集。每块模拟板与FPGA电气连接图如图3所示,模拟板所有管脚都连接到FPGA通用I/O管脚。

1.2 DDRⅡ SDRAM设计

DDRⅡ(Double Data RateⅡ) SDRAM[8]是第二代双倍速率同步动态随机存储器,与SDRAM和DDR SDRAM相比,DDRⅡ SDRAM有着更高的数据传输速率、更大的存储容量和相对更低的功耗。

本系统选用Micron公司的MT47H128M16RT?25E芯片作为采集数据存储器。MT47H128M16RT?25E属于DDRⅡ SDRAM,其在列地址脉冲选通潜伏期(CL)设置为3个时钟周期时,数据传输率最高达到400 Mb/s,结合其16 bit的数据总线,数据突发传输速率达到800 MB/s,并且具有2 Gb的数据存储深度。

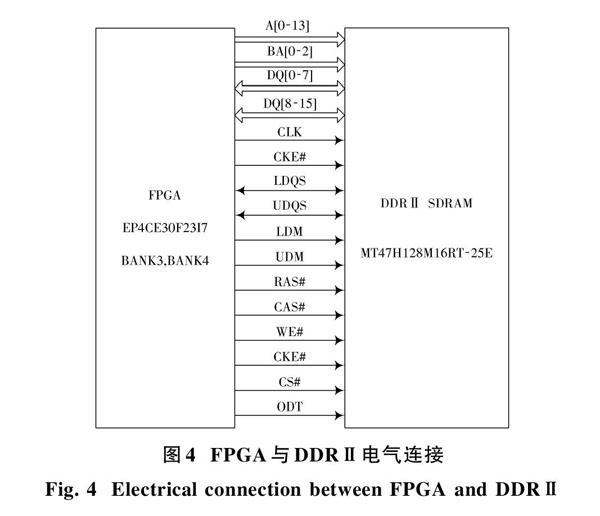

MT47H128M16RT?25E芯片采用SSTL?18接口协议,供电电压为1.8 V,接口信号线分为5组:地址总线A[0?13]、bank地址总线BA[0?2]、数据总线DQ[0?15];差分时钟信号线CLK/CLK#;数据传输信号线LDQS,UDQS,LDM,UDM;命令信号线CAS#,RAS#,WE#;控制信号线CKE#,CS#,ODT。与FPGA的电气连接图如图4所示。

本系统采用Altera公司提供的DDRⅡ IP核对MT47H128M16存储芯片进行读写控制,在使用DDRⅡ IP核时,FPGA提供专用的外部存储器接口管脚DQ,DM,DQS和差分时钟信号管脚[9],因此DDRⅡ与FPGA的管脚连接不能随意分配。本系统选用EP4CE30F23I7 FPGA的BANK4和BANK3与DDRⅡ的管脚进行连接,其中:DDRⅡ的地址总线、BANK地址总线、命令信号线、信号线管脚连接到BANK3和BANK4的通用I/O管脚;DDRⅡ的数据总线、数据传输信号线连接到BANK3的两组专用外部存储器接口管脚5B和3B中,数据总线的低8位,LDQS,LDM分别连接到DQ5B,DQS5B,DM5B,数据总线的高8位,UDQS,UDM分别接到DQ3B,DQS3B,DM3B,每组的DQS与DM管脚是固定的,但数据DQ可以交换;DDRⅡ的差分时钟信号连接到BANK3的一组差分信号输出管脚DIFFIO_P和DIFFIO_N,并且在DDRⅡ的差分时钟信号之间接100 Ω电阻进行差模信号匹配。

由于DDRⅡ采用SSTL接口协议,需提供其SSTL参考电压VREF,其值为DDRⅡ供电电压的一半,并且为了保证信号质量,对DDRⅡ的地址总线和控制线需端接50 Ω精密电阻上拉到VTT电平,因此本系统选用双倍速率存储器专用的Sink和Source终端稳压器TPS51200提供DDRⅡ的VREF电压和VTT电平。另外,由于EP4CE30F23I7的BANK3和BANK4的管脚与DDRⅡ相连,因此这两个BANK管脚需采用SSTL接口电平,其VCCIO3和VCCIO4接DDRⅡ供电电压、VREF3B和VERF4B接DDRⅡ的VREF,并且为了实现片上匹配阻抗(On?chip termination),减少信号反射和保持信号完整性,在BANK4的RUP与RDN端口分别接50 Ω精密电阻进行上拉和下拉。

2 FPGA逻辑控制设计

本系统选用的Altear公司Cyclone IV EP4CE30F23I7 FPGA具有3万个逻辑单元、4个PLL锁相环、600 kb的存储空间,采用484pin的FBGA封装,具有8组16 bit的外部存储器接口管脚,在满足本系统设计的同时,可以将本系统选用的DDRⅡ存储器扩展到8片。

在设计时,采用QuartusⅡ 13.0为开发环境,Verilog为设计语言,ModelSim为综合前仿真工具,进行FPGA控制逻辑设计。FPGA的逻辑控制采用模块化设计,主要包括数据采集逻辑控制模块、数据存储逻辑控制模块、数据传输逻辑控制模块三部分。

2.1 数据采集逻辑控制

数据采集逻辑控制的作用是对6块模拟板进行数据采集控制,主要分为参数配置和ADC转换数据接收两部分。

2.1.1 参数配置

参数配置主要是对ADC采样率、ADC采集时间、ADC采集通道数、PGA放大倍数进行配置,这些参数值通过RS 485串口通信从上位机接收并存入参数配置寄存器中。

本系统设计的FPGA外部时钟为24.576 MHz,通过FPGA的PLL锁相环技术将其倍频到98.304 MHz,设计时钟分频器模块,对98.304 MHz时钟进行4,8,12,24,48,96,192,384分频。根据从上位机获得的ADC采样率值,选择对应的分频倍数,将分频后的时钟传输到ADC的CLK端口,实现48 kHz,24 kHz,16 kHz,8 kHz,4 kHz,2 kHz,1 kHz,500 Hz的ADC采样率配置。设计精确时间计数器模块,以98.304 MHz作为时钟脉冲,计数满98 034 000次后为1 s,实现精确到ns的ADC采集时间配置。根据ADC采集通道数和PGA放大倍数的值设置ADC的PWDN#[1?8]管脚和PGA的G[0?4]管脚高低电平,实现对采集通道数和程控放大倍数的配置。

2.1.2 ADC转换数据接收

参数配置完成后,接收到采集命令,开启ADC主时钟CLK,在整秒脉冲到达时,拉低ADC的同步管脚SCLK至少一个CLK时钟周期后,各个打开的采集通道开始同步采集。ADC一个采集点转换完成,DRDY#管脚由高到低,根据ADC的SPI数据接收时序,在至少一个CLK时钟周期后,连续输出192个SCLK时钟周期,从ADC的DOUT管脚接收24 bit[×]8通道的192 bit数据。将每块模拟板同时接收到的192 bit数据存储到数据缓冲器DATA[6][192]中,待缓存器中的数据存入DDRⅡ中后,开始下一采集点数据的转换接收。

2.2 数据存储逻辑控制

数据存储逻辑控制的作用是利用DDRⅡ IP核实现对DDRⅡ的读写控制[10],并在ADC采集间隔的时间里将48通道[×]24位总共1 152 bit数据存储到DDRⅡ中,实现实时采集存储功能,采集存储完成后,讀出所有数据,通过RS 485串口通信上传到上位机。

2.2.1 利用IP核实现DDRⅡ读写控制

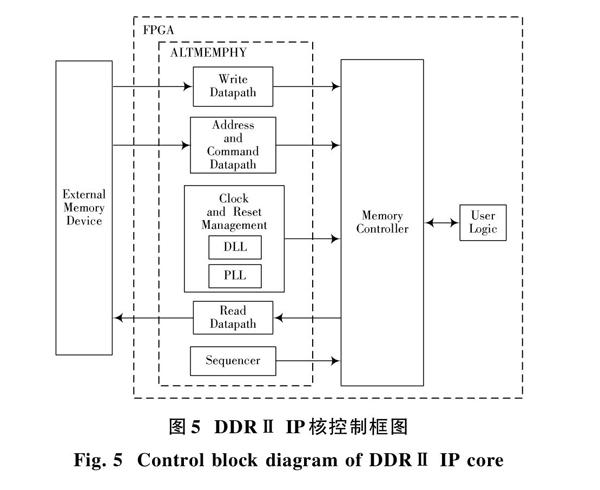

FPGA利用DDRⅡ IP核控制外部DDRⅡ存储器的框图如图5所示[11]。ALTMEMPHY和Memory Controller为IP核生成的DDRⅡ控制器,User Logic为本系统驱动IP核控制DDRⅡ读写的驱动器,External Memory Device为外部DDRⅡ存储器。

调用QuartusⅡ 13.1的IP库MegaWizard Plug?In Manager,选择DDRⅡ SDRAM Controller with ALTMEMPHY,进行本系统选择的DDRⅡ存储器MT47H128M16的参数设置,生成结合ALTMEMPHY的DDRⅡ控制器。DDRⅡ控制器的mem_xx信号连接外部DDRⅡ存储器,用于对本系统选用的MT47H128M16存储器控制,local_xx为本地总线信号,用于User Logic驱动器和DDRⅡ控制器通信。DDRⅡ控制器的外部时钟为FPGA的外部时钟为24.576 MHz,控制DDRⅡ的输入时钟为166.7 MHz,满足Cyclone IV E speed grade 7的DDRⅡ IP最高支持167 MHz的要求。生成的IP core文件中,有用于对DDRⅡ控制器测试的顶层测试文件_example_top,其功能框图如图6所示,_example_top文件例化了DDRⅡ控制器和一个用于驱动DDRⅡ控制器的例程驱动器_example_driver文件。在工程里,设置_example_top为顶层文件,运行IP core里_pin_assignments.tcl脚本文件,添加IP core文件里sdc时序约束文件_phy_ddr_timing.sdc和_example_top.sdc,综合编译顶层文件成功后,配置_example_top文件外部存储器管脚和测试管脚,再次综合编译后,生成.sof文件,通过JTAG连接下载到FPGA中,调用SignalTapⅡ Logic Analyer检测到_example_top的信号 test_complete为高电平,表示生成的DDRⅡ控制器正常控制DDRⅡ。

DDRⅡ控制器成功完成测试后,根据DRRⅡ控制器手册和DDRⅡ时序手册,设计本系统DDRⅡ控制器的驱动器User Logic部分,其与DDRⅡ控制器的Block Diagram连接如图7所示。

驱动器的逻辑设计采用三段式的有限Mealy状态机,其状态图如图8所示。状态图中,1,2,3,4,5,6分别表示:IDLE空状态,进行各个参数值初始化;MEM_WRIT_FIRST第一次写状态,用于准备写入的数据;MEN_READ读命令状态,进行DDRⅡ存储器读取数据操作;MEM_WRITE_BURST_BEGIN产生bustbegin信号状态,准备写DDRⅡ存储器;MEM_WRIT写命令状态,进行DDRⅡ存储器写入数据操作;MEM_READ_WAIT等待读取数据完成状态,等待DDRⅡ存储器数据读取完成。

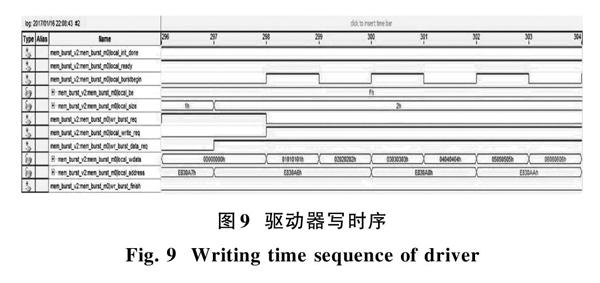

驱动器主时钟为DDRⅡ控制器提供的外部存储器时钟phy_clk,与外部存储器时钟同步。由于在时钟上升沿进行数据传输,而DDRⅡ在上升与下降沿进行数据传输,因此驱动器及DDRⅡ控制器数据总线为32 bit,地址总线也由27 bit变为26 bit,设置读写节拍数local_size为2。在进行写DDRⅡ存储器时,置高wr_burst_req写请求信号,给定一次性写入的32 bit的数据个数wr_burst_len[9:0],写入的初始地址wr_burst_addr[25:0],每接收到wr_burst_data_req数据请求信号,给一个32 bit数据wr_burst_data[31:0]写入DDRⅡ中,直至全部数据写完成。在进行读DDRⅡ存储器时,置高rd_burst_req读请求信号,给定一次性读出的32 bit的数据个数rd_burst_len[9:0],读数据的初始地址rd_burst_addr[25:0],每接收到rd_burst_data_valid信号,读出32 bit的数据rd_burst_data[25:0],对驱动器综合编译下载后,调用SignalTapⅡ Logic Analyzer进行时序分析,得出具体驱动器写时序如图9所示。在wr_burst_data_req信号到达后,给定此时的local_address地址为“E830A6H”,在一个local_burstbegin脉冲下,根据local_size的2个节拍数连续将2个32 bit数据“01010101h”和“02020202h”写入“E830A6H”和“E830A7h”中,按照此时序直至所有数据写入完成。

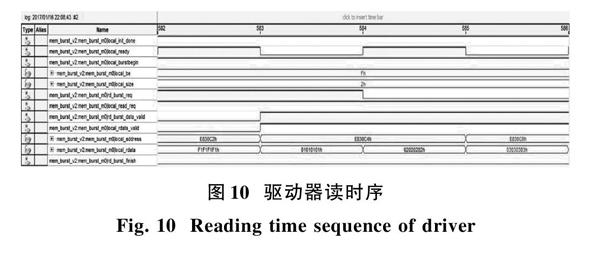

具体的驱动逻辑的读时序如图10所示。local_ read_req信号到达,此时的读地址为“E830A6H”,按照local_size的2个读写节拍数,local_rdata_valid信号到达后连续读出地址“E830A6H”和“E830A7h”中的32 bit数据,读出的数据为“01010101h”和“02020202h”,按照此时序直至所有数据读取完成。

结合读写逻辑时序图,驱动器的写入和读出保持一致,实现了对DDRⅡ的读写控制。

2.2.2 采集数据实时存储与读取逻辑设计

48通道的一个ADC采集转换点数据输出完成后,置高data_ready信号,表示采集转换数据DATA[6][192]准备好,设置wr_burst_len[9:0]的值为36,将一个点的数据DATA[6][192]存入DDRⅡ中,每存储完一个点的数据后写地址wr_burst_addr[25:0]的值加36,直至所有采样点存储完成。读取时,采取同样的方式,置rd_burst_len[9:0]的值为36,在读取命令信号到达后,将一个点的数据读出,每读完一个点的数據后读地址rd_burst_addr[25:0]的值加36,直至读地址与写地址的值相等时表示所有数据读取完成。

2.3 数据传输逻辑控制

采用11位数据格式的串口通信协议进行系统的上位机通信和数据传输,其中上位机为主,本系统为从。以外部时钟为主频,设计时钟分频模块,分频数可变,提供串口通信不同波特率的选择,用以适应不同的传输距离和传输速度。由于最小采样率为500 Hz,采集1 s为500个点,因此,以500个采集点数据为一帧数据进行串口传输,每帧数据进行CRC32校验计算,若CRC32校验主从不一致,则该帧数据重新传输,直至CRC32校验主从一致,保证数据传输的准确性。

3 测试与结论

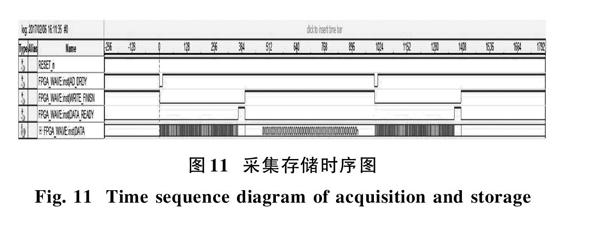

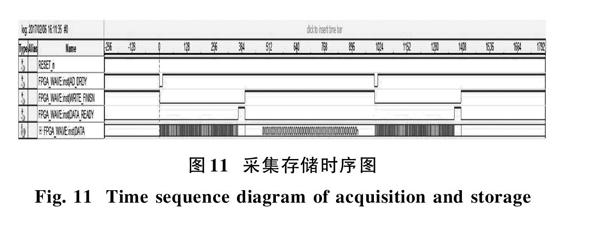

利用RS 485转串口模块进行本系统与PC机的通信,对系统进行性能测试。在PC机上,设置波特率为115 200 b/s的串口小助手软件,将配置信息传输到本系统,配置ADC采样率为48 kHz、ADC采集时间为30 s、ADC通道全开、PGA放大倍数为16倍。利用任意函数波形发生器模拟检波器输出,输出波峰值为140 mV、频率为1 kHz的正弦波信号,接到48通道信号调理电路。给本系统一个触发信号开始进行数据采集。在采集过程中调用SignalTapⅡ Logic analyzer观察整个采集过程,如图11所示。

由于FPGA的存储单元有限,不能同时观察6块模拟板一个点的数据,但每块模拟板与FPGA采取并行结构连接,同时输出一个点192 bit数据,因此,选取其中一块模拟板的数据进行观察。在图11中,AD_DRDY由高到底表示ADC一个点采集转换完成,通过SPI导出ADC转换数据存入寄存器DATA中,一个点数据导出完成置DATA_READY为高,开始存储数据到DDRⅡ中,此时DATA的值保持不变,存储完成后置WRIT_FINISH信号为高,DATA值复位置0,等待下一个采集点数据,在此时48 kHz采样率的两个采样点之间,完成6块模拟板一个采集点1 152 bit数据的转换与存储,满足地震波信号采集的实时性要求。

30 s采集时间到达后,采集结束,将48 000×30 s的1 440 000个采集点,合计1 658 880 kbit采集数据上传到上位机,利用Matlab对采集数据进行图形绘制,绘制出的波形与任意函数波形发生器输出波形基本保持一致。因此,本地震勘探采集系统完成48通道实时采集设计,并且具有存储容量大、实时性好、系统稳定的特点。

4 结 语

本文设计了一种基于FPGA的多通道实时地震勘探采集系統,采用“FPGA+DDRⅡ SDRAM+ADC+RS 485”的硬件结构,利用FPGA精准、灵活、并行的高性能控制以及DDRⅡ高速大容量存储,实现500 Hz~48 kHz采样率下48通道的同步实时地震勘探信号采集,与传统的4通道或8通道的采集系统相比,降低地震勘探工作复杂度,提高地震勘探的工作效率,对地震勘探工程实施具有重要意义。

参考文献

[1] 武喜尊,赵镨.中国煤炭地震勘探技术发展[J].中国煤田地质,2003,15(6):51?55.

WU X Z, ZHAO P. Development of coal seismic exploration technology in China [J]. Coal geology of China, 2003, 15(6): 51?55.

[2] 倪宇东关,王井富,马涛,等.可控震源地震采集技术的进展[J].石油地球物理勘探,2011,46(3):349?356.

NI Y D G, WANG J F, MA T, et al. Progress in seismic acquisition technology of vibroseis [J]. Geophysical exploration of petroleum, 2011, 46(3): 349?356.

[3] 张晓琴,罗隆.基于FPGA的6通道同步数据采集系统研究[J].煤炭技术,2010,29(5):38?40.

ZHANG X Q, LUO L. Research of 6?channel synchronous data acquisition system based on FPGA [J]. Coal technology, 2010, 29(5): 38?40.

[4] 肖积涛,马幼鸣,周鸣争,等.基于FPGA的高速数据采集系统的设计与实现[J].计算机技术与发展,2012,22(6):217?220.

XIAO J T, MA Y M, ZHOU M Z, et al. Design and implementation of high speed data acquisition system based on FPGA [J]. Computer technology and development, 2012, 22(6): 217?220.

[5] Altera. CycloneIV_handbook [EB/OL]. [2009?01?23]. https://www.altera.com.cn/products/fpga/cyclone?series/cyclone?iv/overview.html.

[6] 孙娴,罗桂娥.一种高精度地震勘探数据采集系统的设计与实现[J].计算机测量与控制,2008,16(6):881?883.

SUN X, LUO G E. Design and implementation of a high precision data acquisition system for seismic exploration [J]. Computer measurement and control, 2008, 16(6): 881?883.

[7] TI. ADS1278_datasheet [EB/OL]. [2010?05?07]. http://www.ti.com/product/ads1278.

[8] JEDEC Solid State Technology Association. JESD79?2F:DDR2 SDRAM specification [S]. Arlington: JEDEC Solid State Technology Association, 2009.

[9] Altera. External memory interface handbook [EB/OL]. [2015?11?04]. https://www.altera.com/support/support?resources/external?memory.html.

[10] 陈平,张春,张一山,等.DDR2 SDRAM控制器IP功能测试与FPGA验证[J].微电子学,2016,46(2):251?254.

CHEN P, ZHANG C, ZHANG Y S, et al. DDR2 SDRAM controller IP function test and FPGA verification [J]. Microelectronics, 2016, 46(2): 251?254.

[11] Altera. DDR and DDR2 SDRAM controllers with ALTMEMPHY IP user guide [EB/OL]. [2011?03?25]. https://www.altera.com/bin/search?q=DR+and+DDR2+SDRAM+controllers& client=www&output=xml_no_dtd&proxystylesheet=www&ie= UTF?8&sort=date%3AD%3AL%3Ad1&entqr=3&entsp=a&oe=UTF?8&ud=1&getfields=*&entqrm=0&site=www&mainsite=&access=p.